June 1989

# 5497/DM7497 Synchronous Modulo-64 Bit Rate Multiplier

### **General Description**

The '97 contains a synchronous 6-stage binary counter and six decoding gates that serve to gate the clock through to the output at a sub-multiple of the input frequency. The output pulse rate, relative to the clock frequency, is determined by signals applied to the Select (S0–S5) inputs. Both true and complement outputs are available, along with an enable input for each. A Count Enable input and a Terminal Count output are provided for cascading two or more packages. An asynchronous Master Reset input prevents counting and resets the counter.

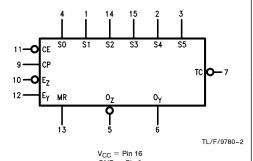

### **Connection Diagram**

### **Logic Symbol**

Order Number 5497DMQB, 5497FMQB or DM7497N See NS Package Number J16A, N16E or W16A

**Pin Names** Description S0-S5 Rate Select Inputs  $\overline{\mathsf{E}}_{\mathsf{Z}}$  $\overline{O}_Z$  Enable Input (Active LOW) E<sub>Y</sub> O<sub>Y</sub> Enable Input Count Enable Input (Active LOW) CP Clock Pulse Input (Active Rising Edge) MR Asynchronous Master Reset Input (Active HIGH) Gated Clock Output (Active LOW)  $\overline{\mathsf{O}}_\mathsf{Z}$ O<sub>y</sub> TC Complement Output (Active HIGH) Terminal Count Output (Active LOW)

### **Absolute Maximum Ratings (Note)**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 7V

Input Voltage 5.5V

Operating Free Air Temperature Range

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for acutual device operation.

## **Recommended Operating Conditions**

| Symbol             | Parameter                       |     | 5497 |      |      | Units |      |        |

|--------------------|---------------------------------|-----|------|------|------|-------|------|--------|

| Oymbor             | i didilicici                    | Min | Nom  | Max  | Min  | Nom   | Max  | Oilits |

| V <sub>CC</sub>    | Supply Voltage                  | 4.5 | 5    | 5.5  | 4.75 | 5     | 5.25 | V      |

| V <sub>IH</sub>    | High Level Input Voltage        | 2   |      |      | 2    |       |      | V      |

| V <sub>IL</sub>    | Low Level Input Voltage         |     |      | 0.8  |      |       | 0.8  | V      |

| loh                | High Level Output Current       |     |      | -0.4 |      |       | -0.4 | mA     |

| l <sub>OL</sub>    | Low Level Output Current        |     |      | 16   |      |       | 16   | mA     |

| T <sub>A</sub>     | Free Air Operating Temperature  | -55 |      | 125  | 0    |       | 70   | °C     |

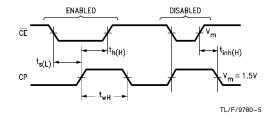

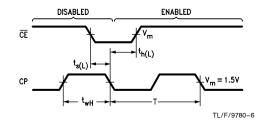

| t <sub>s</sub> (L) | Setup Time LOW, CE to CP Rising | 25  |      |      | 25   |       |      | ns     |

| t <sub>h</sub> (H) | Hold Time HIGH, CE to CP Rising | 0   |      |      | 0    |       |      | ns     |

| t <sub>h</sub> (L) | Hold Time LOW, CE to CP Falling | 0   |      |      | 0    |       |      | ns     |

| t <sub>w</sub> (H) | CP Pulse Width HIGH             | 20  |      |      | 20   |       |      | ns     |

| t <sub>w</sub> (L) | CP Pulse Width LOW              | 20  |      |      |      |       |      | ns     |

| t <sub>w</sub> (H) | MR Pulse Width HIGH             | 15  |      |      | 15   |       |      | ns     |

### **Electrical Characteristics** Over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                                        | Conditions                                      |      | Min | Typ<br>(Note 1) | Max  | Units |  |

|-----------------|--------------------------------------------------|-------------------------------------------------|------|-----|-----------------|------|-------|--|

| VI              | Input Clamp Voltage                              | $V_{CC} = Min, I_I = -12 \text{ mA}$            |      |     |                 | -1.5 | ٧     |  |

| V <sub>OH</sub> | High Level Output<br>Voltage                     | $V_{CC} = Min, I_{OH} = Max,$<br>$V_{IL} = Max$ |      | 2.4 | 3.4             |      | ٧     |  |

| $V_{OL}$        | Low Level Output<br>Voltage                      | $V_{CC} = Min, I_{OL} = Max,$<br>$V_{IH} = Min$ |      |     | 0.2             | 0.4  | V     |  |

| II              | Input Current @ Max<br>Input Voltage             | $V_{CC} = Max, V_I = 5.5V$                      |      |     |                 | 1    | mA    |  |

| I <sub>IH</sub> | High Level Input Current                         | $V_{CC} = Max, V_I = 2.4V$                      | DM74 |     |                 | 40   | μΑ    |  |

|                 |                                                  | Clock Inputs                                    | 54   |     |                 | 80   |       |  |

| I <sub>IL</sub> | Low Level Input Current V <sub>CC</sub> = Max, V |                                                 | DM74 |     |                 | -1.6 | mA    |  |

|                 |                                                  | Clock Inputs                                    | 54   |     |                 | -3.2 | ]     |  |

| los             | Short Circuit                                    | V <sub>CC</sub> = Max                           | 54   | -20 |                 | -55  | mA    |  |

|                 | Output Current                                   | (Note 2) DM74                                   |      | -18 |                 | -55  | IIIA  |  |

| Icc             | Supply Current With<br>Outputs High              | V <sub>CC</sub> = Max                           |      |     |                 | 120  | mA    |  |

Switching Characteristics  $V_{CC}=+5.0V$ ,  $T_A=+25^{\circ}C$  (See Section 1 for waveforms and load configurations)

|                                      |                                                       | 54  | 497           | DM               | Units    |     |

|--------------------------------------|-------------------------------------------------------|-----|---------------|------------------|----------|-----|

| Symbol                               | Parameter                                             | _   | 15 pF<br>400Ω | C <sub>L</sub> = |          |     |

|                                      |                                                       | Min | Max           | Min              | Max      |     |

| f <sub>max</sub>                     | Maximum Clock Frequency                               | 25  |               | 25               |          | MHz |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>E <sub>Z</sub> to Ō <sub>Z</sub> |     | 18<br>23      |                  | 18<br>23 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay  E <sub>Z</sub> to O <sub>Y</sub>   |     | 30<br>33      |                  | 30<br>33 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>E <sub>Y</sub> to O <sub>Y</sub> |     | 14<br>10      |                  | 14<br>10 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>S <sub>n</sub> to O <sub>Y</sub> |     | 23<br>23      |                  | 23<br>23 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>S <sub>n</sub> to O <sub>Z</sub> |     | 14<br>14      |                  | 14<br>14 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to O <sub>Y</sub>             |     | 39<br>30      |                  | 39<br>30 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to O <sub>Z</sub>             |     | 18<br>26      |                  | 18<br>26 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to TC                         |     | 35<br>33      |                  | 30<br>33 | ns  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay CE to TC                            |     | 25<br>21      |                  | 20<br>21 | ns  |

| t <sub>PLH</sub>                     | Propagation Delay<br>MR to O <sub>Y</sub>             |     | 43            |                  | 36       | ns  |

| t <sub>PHL</sub>                     | Propagation Delay<br>MR to Ō <sub>Z</sub>             |     | 34            |                  | 23       | ns  |

# **Timing Diagrams**

### **Functional Description**

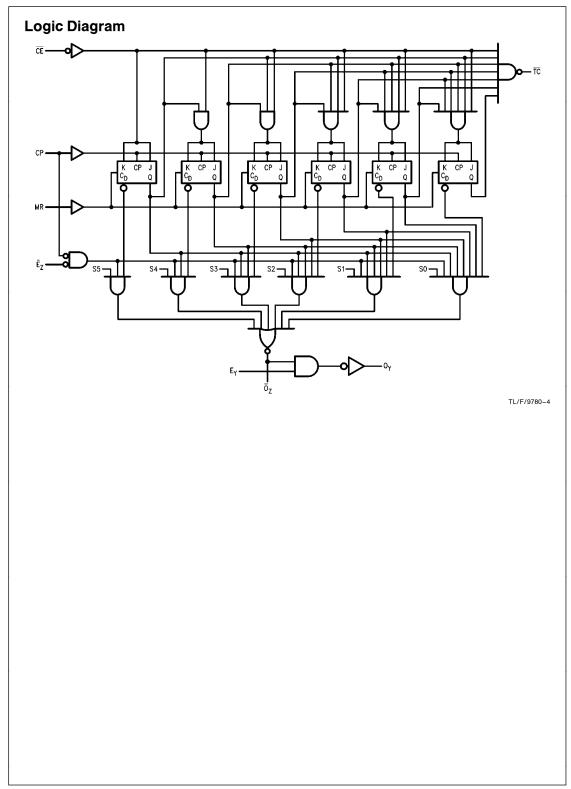

The '97 contains six JK flip-flops connected as a synchronous modulo-64 binary counter. A LOW signal on the Count Enable ( $\overline{\text{CE}}$ ) input permits counting, with all state changes initiated simultaneously by the rising edge of the clock. When the count reaches maximum (63), with all Qs HIGH, the Terminal Count ( $\overline{\text{TC}}$ ) output will be LOW if  $\overline{\text{CE}}$  is LOW. A HIGH signal on Master Reset (MR) resets the flip-flops and prevents counting, although output pulses can still occur if the clock is running,  $\overline{\text{E}}_{\text{Z}}$  is LOW and S5 is HIGH.

The flip-flop outputs are decoded by a 6-wide AND-OR-IN-VERT gate. Each AND gate also contains the buffered and inverted CP and Z-enable ( $\overline{E}_Z$ ) functions, as well as one of the Select (S0–S5) inputs. The Z output,  $\overline{O}_Z$  is normally HIGH and goes LOW when CP and  $\overline{E}_Z$  are LOW and any of the AND gates has its other inputs HIGH. The AND gates are enabled by the counter at different times and different rates relative to the clock. For example, the gate to which S5 is connected is enabled during every other clock period, assuming S5 is HIGH. Thus, during one complete cycle of the counter (64 clocks) the S5 gate is enabled 32 times and can therefore gate 32 clocks per cycle to the output. The S4 gate is enabled 16 times per cycle, the S3 gate 8 times per cycle, etc. The output pulse rate thus depends on the clock rate and which of the S0–S5 inputs is HIGH.

$$f_{out} = \frac{m}{64} \bullet f_{in}$$

Thus by appropriate choice of signals applied to the S0–S5 inputs, the output pulse rate can range from  $^{1}\!/_{64}$  to  $^{63}\!/_{64}$  of the clock rate, as suggested in Rate Select Table. There is no output pulse when the counter is in the "all ones" condition. When m is 1, 2, 4, 8, 16 or 32, the output pulses are evenly spaced, assuming that the clock frequency is constant. For any other value of m the output pulses are not evenly spaced, since the pulse train is formed by interleav-

ing pulses passed by two or more of the AND gates. The Pulse Pattern Table indicates the output pattern for several values of m. In each row, a one means that the  $\overline{O}_Z$  output will be HIGH during that entire clock period, while a zero means that  $\overline{O}_Z$  will be LOW when the clock is LOW in that period. The first column in the output field coincides with the "all zeroes" condition of the counter, while the last column represents the "all ones" condition. The pulse pattern for any particular value of m can be deduced by factoring it into the sum of appropriate powers of two (e.g. 19=16+2+1) and combining the pulses (i.e., the zeroes) shown for each for the relevant powers of two (e.g. for m=16,2 and 1).

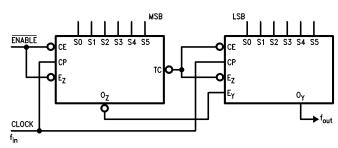

The Y output  $O_Y$  is the complement of  $\overline{O}_Z$  and is thus normally LOW. A LOW signal on the Y-enable input,  $E_Y$ , disables  $O_Y$ . To expand the multiplier to 12-bit rate select, two packages can be cascaded as shown in Figure A. Both circuits operate from the basic clock, with the  $\overline{\Gamma}\overline{O}$  output of the first acting to enable both counting and the output pulses of the second package. Thus the second counter advances at only  $\frac{1}{64}$  the rate of the first and a full cycle of the two counters combined requires 4096 clocks. Each rate select input of the first package has 64 times the weight of its counterpart in the second package.

$$f_{out} = \frac{m_1 \, + \, m_2}{64 \bullet 64} \bullet f_{in}$$

Where:

$$m_1 = S5 \bullet 2^{11} + S4 \bullet 2^{10} + S3 \bullet 2^9 + S2 \bullet 2^8 + S1 \bullet 2^7 + S0 \bullet 2^6$$

(first package)

$$m_2 = S5 \bullet 2^5 + S4 \bullet 2^4 + S3 \bullet 2^3 + S2 \bullet 2_2 + S1 \bullet 2^1 + S0 \bullet 2^0$$

(second package)

Combined output pulses are obtained in *Figure A* by letting the Z output of the first circuit act as the Y-enable function for the second, with the interleaved pulses obtained from the Y output of the second package being opposite in phase to the clock.

FIGURE A. Cascading for 12-Bit Rate Select

TL/F/9780-3

# Functional Description (Continued)

### Mode and Rate Select Table (Note 1)

| Inputs |    |                  |    |    |    |     |    | Clock | Outputs |    |                | Notes |    |       |

|--------|----|------------------|----|----|----|-----|----|-------|---------|----|----------------|-------|----|-------|

| MR     | CE | $\overline{E}_Z$ | S5 | S4 | S3 | S 2 | S1 | S0    | Pulses  | Εγ | O <sub>Y</sub> | Oz    | TC | Notes |

| Н      | Х  | Н                | Х  | Х  | Χ  | Х   | Х  | Χ     | Х       | Н  | L              | Н     | Н  | 2     |

| L      | L  | L                | L  | L  | L  | L   | L  | L     | 64      | Н  | L              | Н     | 1  | 3     |

| L      | L  | L                | L  | L  | L  | L   | L  | Н     | 64      | Н  | 1              | 1     | 1  | 3     |

|        |    |                  |    |    |    |     |    |       |         |    |                |       |    |       |

| L      | L  | L                | L  | L  | L  | L   | Н  | L     | 64      | Н  | 2              | 2     | 1  | 3     |

| L      | L  | L                | L  | L  | L  | Н   | L  | L     | 64      | Н  | 4              | 4     | 1  | 3     |

| L      | L  | L                | L  | L  | Н  | L   | L  | L     | 64      | Н  | 8              | 8     | 1  | 3     |

| L      | L  | L                | L  | Н  | L  | L   | L  | L     | 64      | Н  | 16             | 16    | 1  | 3     |

|        |    |                  |    |    |    |     |    |       |         |    |                |       |    |       |

| L      | L  | L                | Н  | L  | L  | L   | L  | L     | 64      | Н  | 32             | 32    | 1  | 3     |

| L      | L  | L                | Н  | Н  | Н  | Н   | Н  | Н     | 64      | Н  | 63             | 62    | 1  | 3     |

| L      | L  | L                | Н  | Н  | Н  | Н   | Н  | Н     | 64      | L  | Н              | 63    | 1  | 4     |

| L      | L  | L                | Н  | L  | L  | L   | L  | L     | 64      | Н  | 40             | 40    | 1  | 5     |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Note 1: Numerals indicate number of pulses per cycle.

Note 2: This is a simplified illustration of the clear function. CP and  $\overline{E}_Z$  also affect the logic level of  $O_Y$  and  $\overline{O}_Z$ . A LOW signal on  $E_Y$  will cause  $O_Y$  to remain HIGH.

Note 3: Each rate illustrated assumes S0-S5 are constant throughout the cycle; however, these illustrations in no way prohibit variable-rate operation.

Note 4:  $E_Y$  is used to inhibit output Y.

Note 5:  $f_{out} = m \bullet \frac{f_{in}}{64} = \frac{(32 + 8) f_{in}}{64} = \frac{40 f_{in}}{64} = 0.625 f_{in}$

### Pulse Pattern Table

|    | Outsid Parks Parks at 2                                              |  |  |  |  |  |

|----|----------------------------------------------------------------------|--|--|--|--|--|

| m  | Output Pulse Pattern at $\overline{O}_Z$                             |  |  |  |  |  |

| 1  | 111111111111111111111111111111111111111                              |  |  |  |  |  |

| 2  | 111111111111111111111111111111111111111                              |  |  |  |  |  |

| 3  | 111111111111111111111111111111111111111                              |  |  |  |  |  |

| 4  | 111111101111111111111111111111111111111                              |  |  |  |  |  |

| 5  | 111111101111111111111111111111111111111                              |  |  |  |  |  |

|    |                                                                      |  |  |  |  |  |

| 6  | 111111101111111101111111111111111111111                              |  |  |  |  |  |

| 8  | 111011111110111111111111111111111111111                              |  |  |  |  |  |

| 10 | 111011111110111111111111111111111111111                              |  |  |  |  |  |

| 12 | 111011101110111111111101110111011111111                              |  |  |  |  |  |

| 14 | 1110111011101110111011101110111111111101110111011101110111011101111  |  |  |  |  |  |

|    |                                                                      |  |  |  |  |  |

| 16 | 10111011101110111011101110111011101110111011101110111011101110111011 |  |  |  |  |  |

| 20 | 101110101011110111011101010111101110111010                           |  |  |  |  |  |

| 24 | 1010101111010101111010101111010101111010                             |  |  |  |  |  |

| 28 | 1010101010101011110101010101010111010101                             |  |  |  |  |  |

| 32 | 0101010101                                                           |  |  |  |  |  |

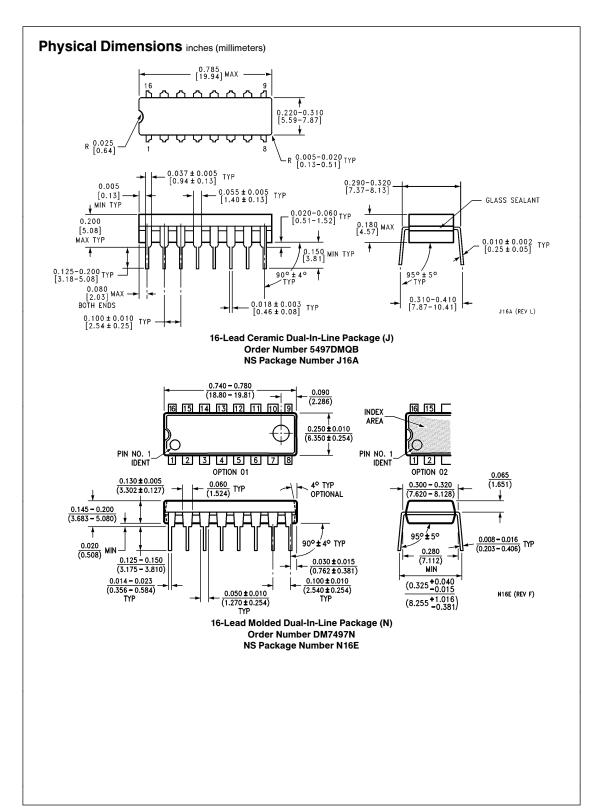

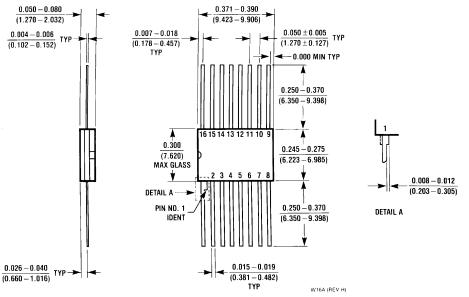

### Physical Dimensions inches (millimeters) (Continued)

16-Lead Ceramic Flat Package (W) Order Number 5497FMQB NS Package Number W16A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408