## **ADVANCE INFORMATION**

#

# 74LVT16374 3.3V ABT 16-Bit D Flip-Flop with TRI-STATE® Outputs

#### **General Description**

The LVT16374 contains sixteen non-inverting D flip-flops with TRI-STATE outputs and is intended for bus oriented applications. The device is byte controlled. A buffered clock (CP) and Output Enable (OE) are common to each byte and can be shorted together for full 16-bit operation.

These flip-flops are designed for low-voltage (3.3V) V<sub>CC</sub> applications, but with the capability to provide a TTL interface to a 5V environment. The LVT16374 is fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.

#### Features

- Input and output interface capability to systems at 5V  $V_{CC}$

- Bus-Hold data inputs eliminate the need for external pull-up resistors to hold unused inputs

- Live insertion/extraction permitted

- Power Up/Down high impedance provides glitch-free bus loading

- Outputs source/sink -32 mA/+64 mA

- Available in SSOP and TSSOP

- E Functionally compatible with the 74 series 16374

- Latch-up performance exceeds 500 mA

# Ordering Code: See Section 11 Logic Symbol

| Pin<br>Names                    | Description                                |

|---------------------------------|--------------------------------------------|

| OEn                             | TRI-STATE Output Enable Input (Active Low) |

| CPn                             | Clock Pulse Input                          |

| 10-115<br>00-015                | Data Inputs                                |

| O <sub>0</sub> -O <sub>15</sub> | TRI-STATE Outputs                          |

|                          | SSOP                            | TSSOP JEDEC                     |

|--------------------------|---------------------------------|---------------------------------|

| Order Number             | 74LVT16374MEA<br>74LVT16374MEAX | 74LVT16374MTD<br>74LVT16374MTDX |

| See NS Package<br>Number | MS48A                           | MTD48                           |

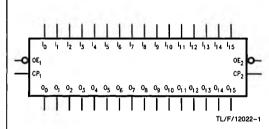

### **Connection Diagram**

TL/F/12022-2

# LVT16374

#### **Functional Description**

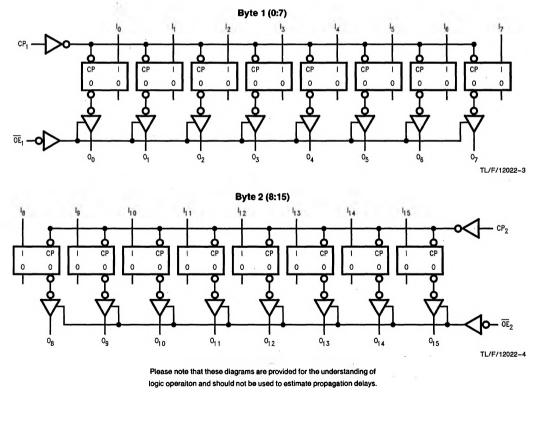

The LVT16374 consists of sixteen edge-triggered flip-flops with individual D-type inputs and TRI-STATE true outputs. The device is byte controlled with each byte functioning identically, but independent of the other. The control pins can be shorted together to obtain full 16-bit operation. Each byte has a buffered clock and buffered Output Enable common to all flip-flops within that byte. The description which follows applies to each byte. Each flip-flop will store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH Clock (CP<sub>n</sub>) transition. With the Output Enable ( $\overline{OE}_n$ ) LOW, the contents of the flip-flops are available at the outputs. When  $\overline{OE}_n$  is HIGH, the outputs go to the high impedance state. Operation of the OE<sub>n</sub> input does not affect the state of the flip-flops.

#### **Truth Tables**

|     | Inputs | Outputs |                                |

|-----|--------|---------|--------------------------------|

| CP1 | OE1    | 10-17   | 0 <sub>0</sub> -0 <sub>7</sub> |

| 5   | L      | н       | н                              |

| ~   | L      | L       | L                              |

| L   | L      | ×       | 00                             |

| х   | н      | x       | z                              |

| Inputs |        |        | Outputs                         |

|--------|--------|--------|---------------------------------|

| CP2    | P2 OE2 | I8-I15 | O <sub>8</sub> -O <sub>15</sub> |

| 5      | Ľ      | н      | н                               |

| 5      | L      | L      | Ι L                             |

| L      | L      | ×      | 00                              |

| х      | н      | x      | z                               |

H = High Voltage Level

L = Low Voltage Level

X = Immaterial

Z = High Impedance

Oo = Previous Oo before HIGH to LOW of CP

### **Logic Diagrams**