#### **ADVANCE INFORMATION**

# 74LVT240 3.3V ABT Octal Buffer/Line Driver with TRI-STATE® Outputs

### **General Description**

The LVT240 is an inverting octal buffer and line driver designed to be employed as a memory address driver, clock driver and bus oriented transmitter or receiver which provides improved PC board density.

These octal buffers and line drivers are designed for low-voltage (3.3V)  $V_{\rm CC}$  applications, but with the capability to provide a TTL interface to a 5V environment. The LVT240 is fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.

#### **Features**

- Input and output interface capability to systems at 5V Vcc

- Bus-Hold data inputs eliminate the need for external pull-up resistors to hold unused inputs

- Live insertion/extraction permitted

- Power Up/Down high impedance provides glitch-free bus loading

- Outputs source/sink -32 mA/+64 mA

- Available in SOIC JEDEC, SOIC EIAJ and TSSOP

- Functionally compatible with the 74 series 240

- Latch-up performance exceeds 500 mA

Ordering Code: See Section 11

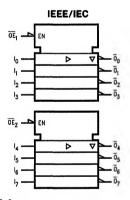

#### **Logic Symbol**

TL/F/12012-1

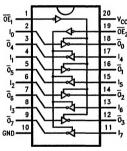

## **Connection Diagram**

# Pin Assignment for SOIC and TSSOP

TL/F/12012-2

#### **Truth Tables**

| Inp             | Inputs Outputs |                       |  |

|-----------------|----------------|-----------------------|--|

| ŌĒ <sub>1</sub> | In             | (Pins 12, 14, 16, 18) |  |

| L               | L              | Н                     |  |

| L               | н              | L                     |  |

| Н               | Х              | Z                     |  |

| Inputs          |    | Outputs           |  |

|-----------------|----|-------------------|--|

| ŌĒ <sub>2</sub> | In | (Pins 3, 5, 7, 9) |  |

| L               | L  | н                 |  |

| L               | н  | L                 |  |

| Н               | Х  | Z                 |  |

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial Z = High Impedance

| Pin Names                         | Description       |  |

|-----------------------------------|-------------------|--|

| ŌĒ₁, ŌĒ₂                          | TRI-STATE Output  |  |

|                                   | Enable Inputs     |  |

| 10-17                             | Inputs            |  |

| $\overline{O}_0 - \overline{O}_7$ | TRI-STATE Outputs |  |

|                          | SOIC JEDEC                | SOIC EIAJ                 | TSSOP        |

|--------------------------|---------------------------|---------------------------|--------------|

| Order Number             | 74LVT240WM<br>74LVT240WMX | 74LVT240SJ<br>74LVT240SJX | 74LVT240MTCX |

| See NS<br>Package Number | M20B                      | M20D                      | MTC20        |