## BASIC CIRCUIT SCHEMATIC

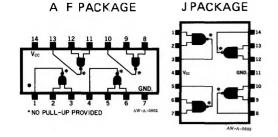

The 8881 is a Quad 2-Input NAND Gate with bare output collectors. Absence of an output pull-up structure allows the user complete freedom in the use of the 8881 in collector-logic (wired-AND) and similar applications. Proper pull-up resistor selection will allow as many as 50 outputs to be tied together.

Collector-logic, using the 8881, can provide increased system flexibility and lower system cost due to reduced can count.

Section 4 of this handbook provides detailed usage rules and collector-logic information for this element.

| ACCEPTANCE<br>TEST<br>SUB-GROUP | CHARACTERISTIC                                        | LIMITS               |      |                      |                | TEST CONDITIONS          |                       |                         |                      |                         |                      |             |

|---------------------------------|-------------------------------------------------------|----------------------|------|----------------------|----------------|--------------------------|-----------------------|-------------------------|----------------------|-------------------------|----------------------|-------------|

|                                 |                                                       | MIN.                 | TYP. | MAX.                 | UNITS          | TEMP.<br>58881           | TEMP.<br>N8881        | v <sub>ec</sub>         | DRIVEN<br>INPUT      | OTHER<br>INPUTS         | OUTPUTS              | NOTES       |

| A-4                             | "1" OUTPUT LEAKAGE CURRENT                            |                      |      | 25                   | μA             | +125°C                   | +75°C                 | 5.0V                    | 0.6V                 |                         |                      | 8           |

| A-5<br>A-3<br>A-4               | "0" OUTPUT VOLTAGE                                    |                      |      | 0.4<br>0.4<br>0.4    | v<br>v<br>v    | -55°C<br>+25°C<br>+125°C | 0°C<br>+25°C<br>+75°C | 4.75V<br>5.0V<br>4.75V  | 2.0V<br>2.0V<br>2.0V | 2.0V<br>2.0V<br>2.0V    | 17mA<br>17mA<br>17mA | 9<br>9<br>9 |

| C-1<br>A-3<br>C-1               | "0" INPUT CURRENT                                     | -0.1<br>-0.1<br>-0.1 |      | -1.6<br>-1.6<br>-1.6 | mA<br>mA<br>mA | -55°C<br>+25°C<br>+125°C | 0°C<br>+25°C<br>+75°C | 5.25V<br>5.25V<br>5.25V | 0.4V<br>0.4V<br>0.4V | 5.25V<br>5.25V<br>5.25V |                      |             |

| A-4                             | "1" INPUT CURRENT                                     |                      |      | 25                   | μA             | +125°C                   | +75°C                 | 5.0V                    | 4.5V                 | 0 <b>V</b>              |                      |             |

| A-6                             | TURN-ON DELAY                                         |                      |      | 20                   | ns             | +25°C                    | +25°C                 | 5.0V                    |                      |                         | D.C.F.O. = 20        | 10,14       |

| A-6                             | TURN-OFF DELAY                                        |                      |      | 30                   | ns             | +25°C                    | +25°C                 | 5.0V                    |                      |                         | D.C.F.O. = 20        | 10,14       |

| C-2                             | OUTPUT FALL TIME                                      |                      |      | 50                   | ns             | -55°C                    | 0°C                   | 4.75V                   |                      | )                       | A.C.F.O. = 6         | 11,14       |

| C-2                             | INPUT CAPACITANCE                                     |                      |      | 3.0                  | pf             | +25°C                    | +25°C                 | 5.0V                    | 2.0V                 |                         |                      | 7           |

| A - 2                           | POWER CONSUMPTION OUTPUT "0"<br>(Per Gate) OUTPUT "1" |                      |      | 31<br>8.9            | m₩<br>m₩       | +25°C<br>+25°C           | +25°C<br>+25°C        | 5.25V<br>5.25V          | ov                   |                         |                      |             |

| C-1                             | INPUT LATCH VOLTAGE RATING                            | 6.0                  |      |                      | v              | +25°C                    | +25°C                 | 5.0V                    | 10mA                 | ov                      |                      | 12          |

## ELECTRICAL CHARACTERISTICS (NOTES: 1, 2, 3, 4, 5, 6)

## NOTES:

- 1.

- З.

- 4. 5.

- 6. 7.

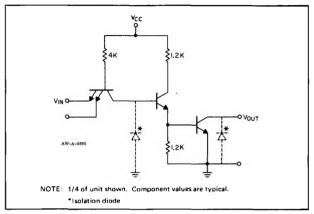

- All voltage and capacitance measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open. All measurements are taken with ground pin tied to zero volts. Positive current flow is defined as into the terminal referenced. Positive NAND Logic definition: "UP" Level = "1", "DOWN" Level = "0". Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings should the isolation diodes become forward biased. Measurements apply to each gate element independently. Capacitance as measured on Boonton Electronic Corporation Model 75A-S8 Capaci-tance Bridge or equivalent. f = 1MHz,  $V_{ac} = 25mV_{TMS}$ . All pins not specifically referenced are tied to guard for capacitance tests. Output pins are left open.

- 8. Connect an external 1K  $\pm 1\%$  resistor from  $V_{\rm CC}$  to the output terminal for this test.

- 9. Output sink current is supplied through a resistor  $V_{cc}$ .

- 10. One DC fan-out is defined as 0.8mA.

- 11. One AC fan-out is defined as 50pf.

- 12. This test guarantees operation free of input latch-up over the specified operating supply voltage range.

- 13. Manufacturer reserves the right to make design and process changes and improvements.

- 14. Detailed test conditions for AC testing are in Section 3,