# CRC GENERATOR/CHECKER

#### **OBJECTIVE SPECIFICATION**

### DESCRIPTION

The CRC Generator/Checker circuit is used to provide an error detection capability for serial digital data handling system. The serial data stream is divided by a selected polynomial and the division remainder is transmitted at the end of the data stream, as a Cyclic Redundancy check character (CRCC). When the data is received, the same calculation is performed. If the received message is error-free, the calculated remainder should satisfy a predetermined pattern. In most cases, the remainder is zero except in the case where Synchronous Data Link Control type protocols are used whereby the correct remainder is checked for 1111000010111000 (x0 - x15)

8 polynomials are provided and can be selected via a 3-bit control bus. Popular polynomials such as CRC-16 and CCITT are implemented. Polynomials can be programmed to start with either all zeros or all ones.

Automatic right justification for polynomials of degree less than 16 is provided.

### FUNCTIONAL DESCRIPTION

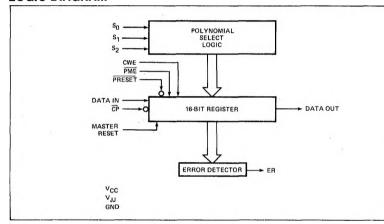

The CRC Generator/Checker circuit provides a means of detecting errors in a serial data communications environment. A binary message can be interpreted as a binary polynomial H(x). This polynomial can be divided by a generator polynomial P(x)such that H(x) = P(x) Q(x) + R(x) whereby Q(x) is the quotient and P(x) is the remainder. During transmission, the remainder is appended to the end of the message as check bits. For a given message, a unique remainder is generated. Hardware implementation of division is simply a feedback shift register with Exclusive-OR gating. Subtraction and addition in modulo 2 is implemented by the Exclusive-OR function. The number of shift register stages is equal to the degree of the divisor polynomial.

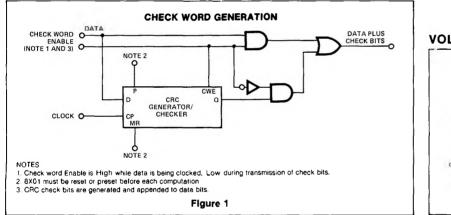

Table 1 shows the polynomials implemented in the CRC circuit. Each polynomial can be selected via the 3-bit polynomial control inputs  $S_0$ ,  $S_1$  and  $S_2$ . To generate the check bits, the data stream is entered via the Data (D) input, using the high to low transition of the Clock (CP) input. This data is gated with the most significant output (Q) of the register, and controls the exclusive OR gates. The Check Word Enable (CWE) must be held high while the data is being entered. After the last data bit is entered, the CWE is brought low and the check bits are shifted out of the register and appended to the data bits using external gating.

### FEATURES

- I<sup>2</sup>L technology

- TTL inputs/outputs

- 10MHz (max) data rate

- Total power dissipation = 175mw (max)

- V<sub>CC</sub> = 5.0V

- V<sub>JJ</sub> = 1.0V

- Separate preset and reset controls

- SDLC specified pattern match

- Automatic right justification

### TYPICAL APPLICATIONS

- Floppy and other disc systems

- · Digital cassette and cartridge systems

- Data communication systems

To check an incoming message for errors, both the data and check bits are entered through the D input with the CWE input held high. The 8X01 is not in the data path. but only monitors the message. The Error output becomes valid after the last check bit has been entered into the 8X01 by a high to low transition of CP. If no detectable errors have occurred during the data transmission, the resultant internal register bits are all low and the Error output (ER) is low. If a detectable error has occurred, ER is high. ER remains valid until the next high to low transition of CP or until the device has been preset or reset. PME must be high if ER output is used to reflect all zero result.

For data communications using the Synchronous Data Link Control protocol (SDLC), the 8X01 is first preset to all ones before any accumulation is done. This applies to both transmitter and receiver.

A special pattern of 1111000010111000 ( $x^0 - x^{15}$ ) is used in place of all zeros during receiving for valid message check. PME is incorporated to select this option. If PME is low during the last bit time of the message, ER output is low if result matches this special pattern. When ER is high, error has occurred.

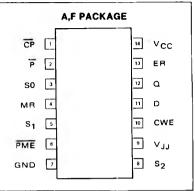

### **PIN CONFIGURATION**

### PIN DESIGNATION

| PIN NO.                                          | FUNCTION                                         |

|--------------------------------------------------|--------------------------------------------------|

| S <sub>0</sub> , S <sub>1</sub> , S <sub>2</sub> | Polynominal Select inputs                        |

| D                                                | Data input                                       |

| CP                                               | Clock (operates on high to low transition) input |

| CWE                                              | Check Word Enable                                |

| P                                                | Preset (active low) input                        |

| MR                                               | Master Reset<br>(active high) input              |

| Q                                                | Data output                                      |

| ER                                               | Error (active high) output                       |

| PME                                              | Pattern match enable (active low)                |

A high level on the Master Reset (MR) input asynchronously clears the register. A low level on the Preset (P) input asynchronously sets the entire register if the control code inputs specify a 16-bit polynomial; in the case of the 12 or 8-bit check polynomials only the most significant 12 or 8 register bits are set and the remaining bits are cleared.

For SDLC, the user must invert the check sum shifted out of the 8X01.

#### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER              |                                  | LIMITS     |     |             | UNIT    |  |

|------------------------|----------------------------------|------------|-----|-------------|---------|--|

|                        |                                  | Min        | Тур | Max         | U.I.I   |  |

| ۱ <sup>۱۱</sup><br>۸CC | Supply voltage<br>Supply current | 4.75<br>40 | 5.0 | 5.25<br>100 | V<br>mA |  |

| CP                     | Clock input                      | 0          |     | 5           | MHz     |  |

8X01-A,F

8X01

# **CRC GENERATOR/CHECKER**

### **OBJECTIVE SPECIFICATION**

## **TRUTH TABLE**

| SE             | SELECT CODE<br>S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> |   |                                                                     |                   |

|----------------|-------------------------------------------------------------|---|---------------------------------------------------------------------|-------------------|

| S <sub>2</sub> |                                                             |   | POLYNOMIAL                                                          | REMARKS           |

| L              | L                                                           | L | $\chi^{16}_{+\chi^{15}_{+\chi^2_{+1}}}$                             | CRC-16            |

| L              | L                                                           | н | X <sup>16</sup> +X <sup>14</sup> +X+1                               | CRC-16 REVERSE    |

| L              | н                                                           | L | $X^{16}+X^{15}+X^{13}+X^7+X^4+X^2+X^{1}+1$                          |                   |

| L              | н                                                           | н | $\chi_{12+\chi_{11+\chi_{3+\chi_{2+\chi_{11}}}}$                    | CRC-12            |

| н              | L                                                           | L | x <sup>8</sup> +x <sup>7</sup> +x <sup>5</sup> +x <sup>4</sup> +x+1 |                   |

| н              | L                                                           | н | X <sup>8</sup> +1                                                   | LRC-8             |

| н              | н                                                           | L | $x^{16}+x^{12}+x^{5}+1$                                             | CRC-CCITT         |

| н              | н                                                           | н | X <sup>16</sup> +X <sup>11</sup> +X <sup>4</sup> +1                 | CRC-CCITT REVERSE |

## LOGIC DIAGRAM

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

(Unless Otherwise Noted)

|                 | DADAMETED                    |                                                                           | LIMITS |     |       |      |  |

|-----------------|------------------------------|---------------------------------------------------------------------------|--------|-----|-------|------|--|

| PARAMETER       |                              | TEST CONDITIONS                                                           | Min    | Тур | Max   | UNIT |  |

| VIH             | Input high voltage           |                                                                           | 2.0    |     |       | v    |  |

| VIL             | Input low voltage            |                                                                           |        |     | 0.8   | v    |  |

| ٧ <sub>IC</sub> | Input clamp diode voltage    | $V_{CC}$ = MIN, $I_{IN}$ = -18mA                                          |        |     | -1.5  | V    |  |

| ۷он             | Output high voltage          | V <sub>CC</sub> = MIN,<br>I <sub>OH</sub> = -400μA, I <sub>JJ</sub> = MIN | 2.7    |     |       | v    |  |

| VOL             | Output low voltage           | V <sub>CC</sub> = MIN, I <sub>OL</sub> = 8mA,<br>I <sub>JJ</sub> = MIN    |        |     | 0.5   | V    |  |

| 4L              | Input low current            | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4V                             |        |     | -0.36 | mA   |  |

| ін              | Input high current           | $V_{CC}$ = MAX, $V_{IN}$ = 2.7V                                           |        |     | 20    | μA   |  |

| ЧН              | Max. input current           | V <sub>CC</sub> = MAX                                                     |        |     | 0.1   | mA   |  |

| los             | Output short circuit current | <sub>CC</sub> = MAX,<br>VOUT = OV, I <sub>JJ</sub> = MIN                  | -10    |     | -42   | mA   |  |

|                 | Supply current               | V <sub>CC</sub> = MAX, inputs open                                        | 10     |     | 18    | mA   |  |

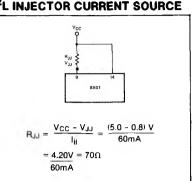

| ມັ              | Injection current            | V <sub>CC</sub> = MAX, inputs open                                        | 60     | 1   | 100   | mA   |  |

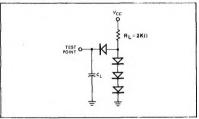

# **TEST CIRCUIT**

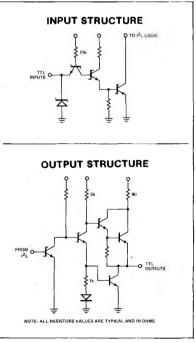

## **INPUT/OUTPUT CIRCUITS**

8X01

I<sup>2</sup>L INJECTOR CURRENT SOURCE

**OBJECTIVE SPECIFICATION**

8X01-A,F

8X01

### **AC ELECTRICAL CHARACTERISTICS**

|                                                                                                                   | 70                          |                          | TEST CONDITIONS                              | LIMITS            |                  |                 | UNIT      |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|----------------------------------------------|-------------------|------------------|-----------------|-----------|

| PARAMETER                                                                                                         | то                          | FROM                     | 1EST CONDITIONS                              | Min               | Тур              | Max             | GIAIT     |

| fmax Maximum clock frequency<br>Pulse width                                                                       |                             |                          |                                              | 5                 | 7                |                 | MHz<br>ns |

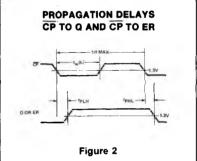

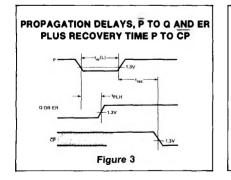

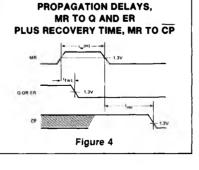

| t <sub>w</sub> CP(L) Clock low<br>t <sub>w</sub> P(L) Preset low<br>t <sub>w</sub> MR(H) Master reset high        |                             |                          | See Figure 2<br>See Figure 3<br>See Figure 4 | 100<br>120<br>150 |                  |                 | ·         |

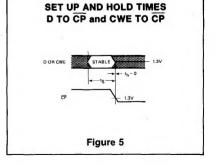

| Setup and hold time<br>t <sub>S</sub> D Setup time<br>t <sub>S</sub> CWE Setup time<br>t <sub>n</sub> Hold time   | Clock<br>Clock<br>Clock     | Data<br>CWE<br>Data, CWE | See Figure 5                                 | 0                 | 120<br>75<br>-30 | 150<br>100<br>0 | ns        |

| Propagation delay<br><sup>t</sup> PLH Low to high<br><sup>t</sup> PHL High to low<br><sup>t</sup> PLH Low to high | Data output                 | Clock, preset            | See Figures 1,2,3                            |                   | 100              | 160             | ns        |

| tPHL High to low<br>tPLH Low to high<br>tPHL High to low                                                          | Data output<br>Error output | MR<br>Clock, MR, preset  | See Figure 4<br>See Figures 2,3,4            |                   | 75<br>150        | 100<br>200      |           |

| tREC Recovery time                                                                                                | Clock                       | MR, preset               | See Figures 3,4                              |                   | 60               | 90              | ns        |

**VOLTAGE WAVEFORMS**

signetics