# 2048-BIT BIPOLAR RAM (256×8)

### **FEATURES**

- On-chip address latches

- 3-state outputs

- Schottky clamped TTL

- Internal control logic for 8X300 system

- Directly interfaces with the 8X300 bipolar microprocessor with no external logic

- May be used on left or right bank

### **APPLICATIONS**

• 8X300 or 8X305 working storage

### DESCRIPTION

The 8X350 bipolar RAM is designed principally as a working storage element in an 8X300 based system. Internal circuitry is provided for direct use in 8X300 applications. When used with the 8X300, the RAM address and data buses are tied together and connected to the IV bus of the system.

The data inputs and outputs share a common I/O bus with 3-state outputs.

The 8X350 is available in commercial and military temperature ranges. For the commercial temperature range (0°C to  $+75^{\circ}$ C) specify N8X350-F, and for the military temperature range ( $-55^{\circ}$ C to  $+125^{\circ}$ C) specify S8X350-F.

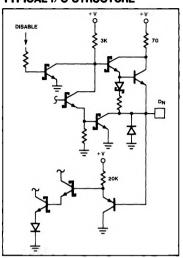

### **TYPICAL I/O STRUCTURE**

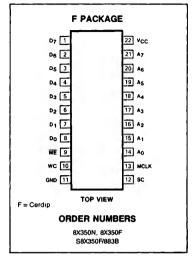

### PIN CONFIGURATION

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER |                   | RATING      | UNIT |  |  |

|-----------|-------------------|-------------|------|--|--|

| vcc       | Supply voltage    | +7          | Vdc  |  |  |

| VIN       | Input voltage     | +5.5        | Vdc  |  |  |

|           | Output voltage    | 1 (         | Vdc  |  |  |

| Vон       | High              | +5.5        |      |  |  |

| Vo        | Off-state         | +5.5        |      |  |  |

|           | Temperature range |             | °C   |  |  |

| $T_A$     | Operating         | 1           |      |  |  |

|           | Commercial        | 0 to +75    |      |  |  |

|           | Military          | -55 to +125 |      |  |  |

| TSTG      | Storage           | -65 to +150 |      |  |  |

### **TRUTH TABLE**

Note X = Don't care

| MODE                                           | ME | sc | wc       | MCLK | BUSSED<br>DATA/ADDRESS<br>LINES |

|------------------------------------------------|----|----|----------|------|---------------------------------|

| Hold address                                   |    |    |          |      |                                 |

| Disable data out                               | 1  | Х  | X        | x    | High Z data out                 |

| Input new address Hold address                 | 0  | 1  | 0        | 1    | Address<br>High Z               |

| Disable data out                               | 0  | 1  | 0        | 0    | High Z data out                 |

| Hold address<br>Write data                     | 0  | 0  | 1        | 1    | Data in                         |

| Hold address<br>Disable data out               | 0  | 0  | 1        | 0    | High Z data out                 |

| Hold address<br>Read data                      | 0  | o  | 0        | x    | Data out                        |

| Undefined state <sup>12</sup>                  | 0  | 1  | 1        | 1    | -                               |

| Hold address <sup>12</sup><br>Disable data out | 0  | 1  | <u> </u> | 0    | High Z data out                 |

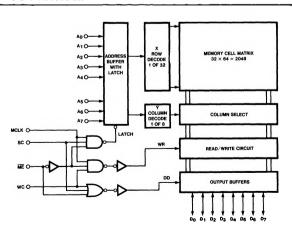

### **BLOCK DIAGRAM**

# 2048-BIT BIPOLAR RAM (256×8)

**DC ELECTRICAL CHARACTERISTICS2** N8X350:  $0^{\circ}C \le T_{A} \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$  S8X350:  $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$

|                   |                                                             |                                                                                                  | N8X350  |        |             | S8X350 |        |             |          |

|-------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------|--------|-------------|--------|--------|-------------|----------|

|                   | PARAMETER                                                   | TEST CONDITIONS                                                                                  | Min Typ |        | Max         | Min    | Тур    | Max         | UNIT     |

| VIL<br>VIH<br>VIC | Input voltage<br>Low¹<br>High¹<br>Clamp¹,3                  | V <sub>CC</sub> = Min<br>V <sub>CC</sub> = Max<br>V <sub>CC</sub> = Min, I <sub>IN</sub> = -12mA | 2.0     |        | .85<br>-1.2 | 2.0    |        | .80<br>-1.2 | ٧        |

| V <sub>OL</sub>   | Output voltage<br>Low <sup>1,4</sup><br>High <sup>1,5</sup> | V <sub>CC</sub> = Min<br>I <sub>OL</sub> = 9.6mA<br>I <sub>OH</sub> = -2mA                       | 2.4     |        | 0.5         | 2.4    |        | .5          | ٧        |

| IIL<br>IIH        | Input current<br>Low<br>High                                | V <sub>IN</sub> = 0.45V<br>V <sub>IN</sub> = 5.5V                                                |         |        | -100<br>25  |        |        | -150<br>50  | μА       |

| lo(off)           | Output current High Z state  Short circuit <sup>3,6</sup>   | ME = High, V <sub>OUT</sub> = 5.5 V<br>ME = High, V <sub>OUT</sub> = 0.5 V<br>SC = WC, ME = Low, |         |        | 40<br>-100  |        |        | 60<br>-100  | μA<br>μA |

| lcc               | V <sub>CC</sub> supply current <sup>7</sup>                 | V <sub>OUT</sub> = 0V, Stored High V <sub>CC</sub> = Max                                         | -20     |        | -70<br>185  | -15    |        | -85<br>200  | mA<br>mA |

| C <sub>IN</sub>   | Capacitance<br>Input<br>Output                              | ME = High, V <sub>CC</sub> = 5.0V<br>V <sub>IN</sub> = 2.0V<br>V <sub>OUT</sub> = 2.0V           |         | 5<br>8 |             |        | 5<br>8 |             | pF       |

# **AC ELECTRICAL CHARACTERISTICS 2.9** N8X350: $0^{\circ}C \le T_{A} \le +75^{\circ}C$ , $4.75V \le V_{CC} \le 5.25V$ R<sub>1</sub> = $470\Omega$ , R<sub>2</sub> = $1k\Omega$ , C<sub>L</sub> = 30pF S8X350: $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ , $4.75V \le V_{CC} \le 5.25V$

|                 |                           |          | FROM    | N8X350  |   |     | S8X350 |     |     |      |

|-----------------|---------------------------|----------|---------|---------|---|-----|--------|-----|-----|------|

|                 | PARAMETER                 | то       |         | Min Typ |   | Max | Min    | Тур | Max | UNIT |

|                 | Enable time               |          |         |         |   |     |        |     |     | ns   |

| TE1             | Output                    | Data out | sc-     |         |   | 35  | ł      | l   | 40  | 1    |

| T <sub>E2</sub> | Output                    | Data out | ME-     |         |   | 35  |        | L   | 40  |      |

|                 | Disable time              |          |         |         |   |     |        |     |     | ns   |

| T <sub>D1</sub> | Output                    | Data out | sc+     |         |   | 35  | 1      |     | 40  | l    |

| TD2             | Output                    | Data out | ME+     |         |   | 35  |        |     | 40  |      |

|                 | Pulse width               |          |         |         |   |     |        |     |     | ns   |

| TW              | Master clock <sup>8</sup> |          |         | 40      |   |     | 50     |     |     |      |

|                 | Setup and hold time       |          |         |         |   |     |        |     |     | ns   |

| TSA             | Setup time                | MCLK-    | Address | 30      |   |     | 40     |     |     |      |

| THA             | Hold time                 | Address  | MCLK-   | 5       | 1 |     | 10     | i   |     |      |

| TSD             | Setup time                | MCLK-    | Data in | 35      |   |     | 45     |     |     |      |

| THD             | Hold time                 | Data in  | MCLK-   | 5       | ļ |     | 10     |     | i   |      |

| T <sub>S3</sub> | Setup time                | MCLK-    | ME-     | 40      |   | 1   | 50     |     |     |      |

| Тнз             | Hold time                 | ME+      | MCLK-   | 5       |   |     | 5      |     |     |      |

| T <sub>S1</sub> | Setup time                | MCLK-    | ME-     | 30      |   | 1   | 40     |     | i   |      |

| T <sub>H2</sub> | Hold time                 | ME-      | MCLK-   | 5       |   |     | 5      |     |     |      |

| T <sub>S2</sub> | Setup time                | ME-      | SC-,WC- | 0       | 1 |     | 5      | }   | }   |      |

| TH1             | Hold time                 | sc-      | MCLK-   | 5       |   | 1   | 5      |     |     |      |

| T <sub>H4</sub> | Hold time                 | wc-      | MCLK-   | 5       |   |     | 5      | 1   | 1   |      |

Notes on following page

# 2048-BIT BIPOLAR RAM (256×8)

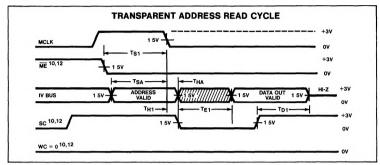

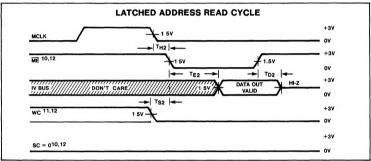

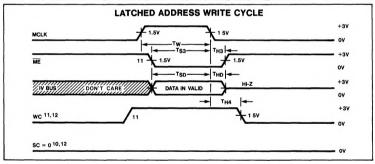

### **TIMING DIAGRAMS**

#### NOTES

- 1 All voltage values are with respect to network ground terminal

- 2 The operating ambient temperature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a 2-minute warm-up

Typical thermal resistance values of the package at maximum temperature are

OJA junction to ambient at 400fpm air flow - 50°C/watt

θ<sub>JA</sub> junction to ambient - still air - 90°C/watt

θ<sub>JA</sub> junction to case - 20°C/watt

- 3 Test each pin one at a time

- 4 Measured with a logic low stored Output sink current is supplied through a resistor to

Vcc

- 5 Measured with a logic high stored

- 6 Duration of the short circuit should not exceed 1 second

- 7 I<sub>CC</sub> is measured with the write enable and memory enable inputs grounded, all other inputs at 4 5V and the output open

- 8 Minimum required to guarantee a Write into the slowest bit

- 9 Applied to the 8X300 based system with the data and address pins tied to the IV Bus

- 10 SC + ME = 1 to avoid bus conflict

- 11 WC + ME = 1 to avoid bus conflict

- 12 The SC and WC outputs from the 8X300 are never at 1 simultaneously

#### TIMING DEFINITIONS

- TS1 Required delay between beginning of Master Enable low and falling edge of Master Clock.

- TSA Required delay between beginning of valid address and falling edge of Master Clock.

- THA Required delay between falling edge of Master Clock and end of valid Address

- TH1 Required delay between falling edge of Master Clock and when Select Command becomes low.

- TE1 Delay between beginning of Select Command low and beginning of valid data output on the IV Bus.

- T<sub>D1</sub> Delay between when select Command becomes high and end of valid data output on the IV Bus.

- TH2 Required delay between falling edge of Master Clock and when Master Enable becomes low.

- TE2 Delay between when Master Enable becomes low and beginning of valid data output on the IV Bus.

- T<sub>D2</sub> Delay between when Master Enable becomes high and end of valid data output on the IV Bus.

- TS2 Required delay between when Select Command or Write Command becomes low and when Master Enable becomes low.

- Tw Minimum width of the Master Clock pulse.

- TS3 Required delay between when Master Enable becomes low and falling edge of Master Clock.

- TH3 Required delay between falling edge of Master Clock and when Master Enable becomes high.

- TSD Required delay between beginning of valid data input on the IV Bus and falling edge of Master Clock.

- THD Required delay between falling edge of Master Clock and end of valid data input on the IV Bus.

- TH4 Required delay between falling edge of Master Clock and when Write Command becomes low.

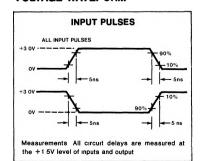

# VOLTAGE WAVEFORM

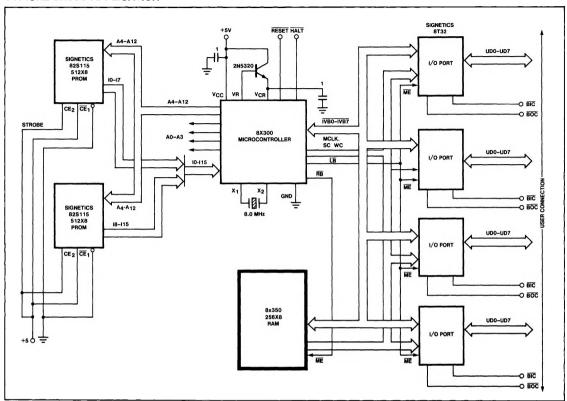

## **TYPICAL 8X350 APPLICATION**

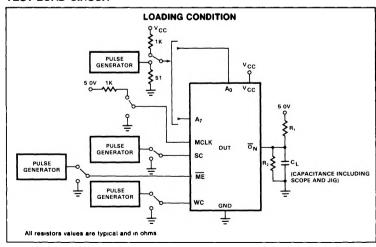

### **TEST LOAD CIRCUIT**