#### Data Sheet

September 1998 File Number 3689.4

## 800MHz Monolithic Pin Driver

intercil

The HFA5251 is a very high speed monolithic pin driver solution for high performance test systems. The device will switch at high data rates between two input voltage levels providing variable amplitude pulses. The output impedance is trimmed to achieve a precision 50 $\Omega$  source for impedance matching. Two differential ECL/TTL compatible inputs control the operation of the HFA5251, one controlling the V<sub>HIGH</sub>/V<sub>LOW</sub> switching and the other controlling the output's high-impedance state. The HFA5251's 800MHz data rate makes it compatible with today's high-speed VLSI test systems and the +7V to -2V output swing allows testing of all common logic families.

The HFA5251 is manufactured in Intersil's proprietary complementary bipolar UHF-1 process. The HFA5251 is offered in die form. Contact your local sales representative for packaging options.

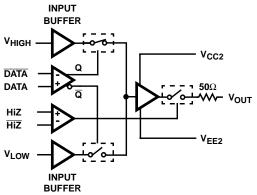

## **Functional Diagram**

#### TRUTH TABLE FOR VOUT

|     |   | DATA             |                   |  |

|-----|---|------------------|-------------------|--|

|     |   | 0                | 1                 |  |

| HiZ | 0 | V <sub>LOW</sub> | V <sub>HIGH</sub> |  |

|     | 1 | HiZ              | HiZ               |  |

#### Features

- Very Fast Rise/Fall Times......500ps

- Precise 50Ω Output Impedance

- High Impedance, Three-State Output Control

## Applications

- IC Tester Pin Electronics

- Pattern Generators

- Pulse Generators

- · Level Comparator/Translator

#### Pinout

VLOW VEE1

# Pin Descriptions

| NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC1</sub>  | Positive Supply. Nominal value is 10V $\pm$ 0.2V. Reducing supply voltage below 9.8V will reduce positive output voltage swing. The total supply voltage from V <sub>CC1</sub> to V <sub>EE1</sub> should not exceed 15.6V for normal operation or exceed 17.0V to prevent damage. Intersil recommends two wire bonds to this pad to provide the lowest possible impedance. In addition, power supply decoupling chip capacitors of 470pF, 0.1µF and a 10µF tantalum are recommended.                      |

| V <sub>EE1</sub>  | Negative Supply. Nominal value is -5.2V $\pm$ 0.2V. A supply voltage more positive than -5.0V will reduce negative output voltage swing. The total supply voltage from V <sub>CC1</sub> to V <sub>EE1</sub> should not exceed 15.6V for normal operation or exceed 17.0V to prevent damage. Intersil recommends two wire bonds to this pad to provide the lowest possible impedance. In addition, power supply decoupling chip capacitors of 470pF, 0.1µF and a 10µF tantalum are recommended.             |

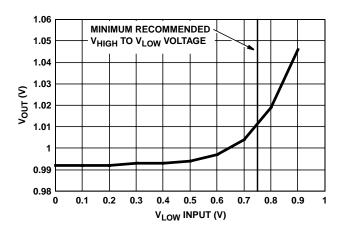

| V <sub>CC2</sub>  | Output Stage Positive Supply. Nominal voltage and cautions are the same as for $V_{CC1}$ . Having decoupling chip capacitors close to $V_{CC2}$ and $V_{EE2}$ is essential since large AC current will flow through this pad to the output during transients. Normally $V_{CC1}$ and $V_{CC2}$ are connected together close to the die and share decoupling capacitors. Intersil recommends two wire bonds for this pad.                                                                                   |

| V <sub>EE2</sub>  | Output Stage Negative Supply. Nominal voltage and cautions are the same as for $V_{EE1}$ . Having decoupling chip capacitors close to $V_{CC2}$ and $V_{EE2}$ is essential since large AC current will flow through this pad to the output during transients. Normally $V_{EE1}$ and $V_{EE2}$ are connected together close to the die and share decoupling capacitors. Intersil recommends two wire bonds for this pad.                                                                                   |

| V <sub>HIGH</sub> | Input Voltage High is used to set the output high level $V_{OH}$ . $V_{HIGH}$ is sensitive to capacitively coupled AC noise. Protection from high frequency noise can be achieved with a low pass filter consisting of a 50 $\Omega$ chip resistor and a 470pF chip capacitor. Without this precaution the pin driver may oscillate due to feedback from the output through the PC board ground.                                                                                                           |

| V <sub>LOW</sub>  | Input Voltage Low is used to set the output low level V <sub>OL</sub> . V <sub>LOW</sub> is sensitive to capacitively coupled AC noise. Protection from high frequency noise can be achieved with a low pass filter consisting of a 50 $\Omega$ chip resistor and a 470pF chip capacitor. Without this precaution the pin driver may oscillate due to feedback from the output through the PC board ground.                                                                                                |

| V <sub>OUT</sub>  | Driver Output. The output impedance has been laser trimmed to match a 50 $\Omega$ transmission line ±2 $\Omega$ . Custom output impedance trimming is available (contact sales office for details) to provide the best match possible to your 50 $\Omega$ system.                                                                                                                                                                                                                                          |

| DATA,<br>DATA     | Differential Digital Inputs used to switch V <sub>OUT</sub> to the V <sub>HIGH</sub> or V <sub>LOW</sub> level. Intersil recommends this input pair be driven by com-<br>plementary ECL signals to provide optimal switching speeds and timing accuracy. However a large Common Mode and Differen-<br>tial Voltage Range is provided to accommodate a variety of signals including single ended TTL and CMOS. When using single<br>ended signals the other input must be tied to an appropriate threshold. |

| HiŻ,<br>HiŻ       | Differential Digital Inputs used to switch V <sub>OUT</sub> from an Active to a High Impedance State. Intersil recommends that this input pair be driven by complementary ECL signals to provide optimal switching speeds and timing accuracy. However a large Common Mode and Differential Voltage Range is provided to accommodate a variety of signals including single ended TTL and CMOS. When using single ended signals the other input must be tied to an appropriate threshold.                   |

## **Absolute Maximum Ratings**

| Supply Voltage 17V                                                             |

|--------------------------------------------------------------------------------|

| Differential Input Voltage (DATA and HiZ) 5V                                   |

| Output Current Continuous (Note 1) 160mA                                       |

| Input Voltage (Any pin except as specified) V <sub>CC</sub> to V <sub>EE</sub> |

| V <sub>OUT</sub> Voltage                                                       |

| V <sub>HIGH</sub> Voltage                                                      |

| V <sub>LOW</sub> Voltage 8V to V <sub>EE</sub>                                 |

| $V_{HIGH}$ to $V_{LOW}$ VoltageV <sub>HIGH</sub> > $V_{LOW}$                   |

|                                                                                |

## **Thermal Information**

| Maximum Junction Temperature (Die) | 175 <sup>0</sup> C   |

|------------------------------------|----------------------|

| Maximum Storage Temperature Range  | o 150 <sup>0</sup> C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

| PARAMETER                                                                   | TEST CONDITIONS                     | TEMP.<br>( <sup>o</sup> C) | MIN   | ТҮР  | МАХ  | UNITS |

|-----------------------------------------------------------------------------|-------------------------------------|----------------------------|-------|------|------|-------|

| INPUT CHARACTERISTICS (V <sub>HIGH</sub> , V <sub>LOW</sub> )               |                                     | I                          |       | 1    |      |       |

| V <sub>HIGH</sub> Input Offset Voltage                                      | V <sub>OUT</sub> = 0V               | 25                         | -150  | -50  | +50  | mV    |

| V <sub>LOW</sub> Input Offset Voltage                                       | V <sub>OUT</sub> = 0V               | 25                         | -150  | -50  | +50  | mV    |

| V <sub>HIGH</sub> Input Bias Current                                        | V <sub>HIGH</sub> = -2.25V to +7.5V | 25                         | -50   | 110  | 300  | μA    |

| V <sub>LOW</sub> Input Bias Current                                         | V <sub>LOW</sub> = -2.5V to +7.25V  | 25                         | -300  | -110 | 50   | μA    |

| V <sub>HIGH</sub> Voltage Range                                             |                                     | 25                         | -2.25 | -    | 7.5  | V     |

| V <sub>LOW</sub> Voltage Range                                              |                                     | 25                         | -2.5  | -    | 7.25 | V     |

| V <sub>HIGH</sub> to V <sub>LOW</sub> Differential Voltage Range            |                                     | 25                         | 0.25  | -    | 10   | V     |

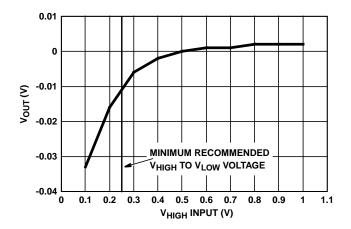

| V <sub>HIGH</sub> /V <sub>LOW</sub> Interaction at 500mV (Note 11)          |                                     | 25                         | -     | 2    | 4    | mV    |

| V <sub>HIGH</sub> /V <sub>LOW</sub> Interaction at 250mV (Note 11)          |                                     | 25                         | -     | 20   | 40   | mV    |

| LOGIC INPUT CHARACTERISTICS (DATA, DATA, HiZ, HiZ,                          | Z)                                  |                            |       | 1    | 1    |       |

| Logic Input Voltage Range                                                   |                                     | 25                         | -2    | -    | 7    | V     |

| Logic Differential Input Voltage                                            |                                     | 25                         | 0.4   | -    | 5    | V     |

| DATA/DATA Logic Input High Current                                          | $V_{IH} = 0V, V_{IL} = -2V$         | 25                         | -50   | 110  | 300  | μA    |

| DATA/DATA Logic Input Low Current                                           | $V_{IH} = 0V, V_{IL} = -2V$         | 25                         | -700  | -300 | 50   | μA    |

| HiZ/HiZ Logic Input High Current                                            | $V_{IH} = 0V, V_{IL} = -2V$         | 25                         | -50   | 70   | 200  | μΑ    |

| HiZ/HiZ Logic Input Low Current                                             | $V_{IH} = 0V, V_{IL} = -2V$         | 25                         | -300  | -80  | 50   | μA    |

| TRANSFER CHARACTERISTICS                                                    |                                     |                            |       |      |      |       |

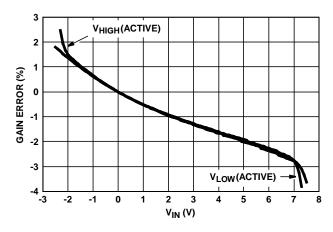

| V <sub>HIGH</sub> Voltage Gain                                              | $V_{HIGH} = -1V$ to 6.5V            | 25                         | 0.95  | -    | 1    | V/V   |

| V <sub>LOW</sub> Voltage Gain                                               | $V_{LOW} = -1.5V$ to 6V             | 25                         | 0.95  | -    | 1    | V/V   |

| V <sub>HIGH</sub> /V <sub>LOW</sub> Linearity Error (Note 7)                | Fullscale = 5V                      | 25                         | -0.5  | -    | 0.5  | %     |

| V <sub>HIGH</sub> /V <sub>LOW</sub> Linearity Error (Note 8)                | Fullscale = 8.5V                    | 25                         | -0.75 | -    | 0.75 | %     |

| V <sub>HIGH</sub> /V <sub>LOW</sub> End Point Gain Deviation (Notes 10, 13) | 0.5V Steps                          | 25                         | -2.0  | -    | 2.0  | %     |

| V <sub>HIGH</sub> End Point Gain Error (Notes 10 and 14)                    | V <sub>OUT</sub> = 6.7V to 7.0V     | 25                         | -20   | -    | 20   | mV    |

| V <sub>HIGH</sub> /V <sub>LOW</sub> -3dB Bandwidth                          | 200mV <sub>P-P</sub>                | 25                         | -     | 100  | -    | MHz   |

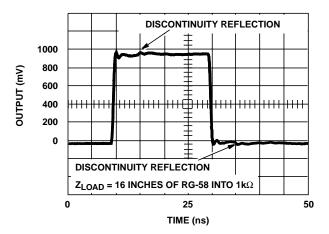

| <b>SWITCHING CHARACTERISTICS</b> ( $Z_{LOAD}$ = 16 inches of                | RG-58 Terminated with $50\Omega$ )  |                            |       |      |      |       |

| Propagation Delay (Notes 2, 17)                                             |                                     | 25                         | 0.8   | -    | 1.5  | ns    |

| Propagation Delay Match (Notes 2, 17)                                       | Rising to Falling Edge              | 25                         | -100  | -    | 100  | ps    |

| Rising Edge Propagation Delay vs Duty Cycle (Notes 12, 17)                  |                                     | 25                         | -120  | -20  | 80   | ps    |

| Falling Edge Propagation Delay vs Duty Cycle (Notes 12, 17)                 |                                     | 25                         | -80   | 20   | 120  | ps    |

| Active to HiZ Delay (Note 17)                                               |                                     | 25                         | 1.2   | 1.7  | 2.2  | ns    |

| HiZ to Active Delay (Note 17)                                               |                                     | 25                         | 2.1   | 2.6  | 3.1  | ns    |

| TRANSIENT RESPONSE (Z <sub>LOAD</sub> = 16 inches of RG-58 Te               | erminated with 5pF)                 |                            |       |      |      |       |

| Rise/Fall Time (20%-80%)                                                    | 1V <sub>P-P</sub>                   | 25                         | -     | 450  | 500  | ps    |

| Rise/Fall Time (10%-90%)                                                    | 3V <sub>P-P</sub>                   | 25                         | -     | 890  | 1000 | ps    |

| PARAMETER                                             | TEST CONDITIONS                                 | TEMP.<br>( <sup>o</sup> C) | MIN                  | ТҮР  | MAX                  | UNITS |

|-------------------------------------------------------|-------------------------------------------------|----------------------------|----------------------|------|----------------------|-------|

| Rise/Fall Time (10%-90%) (Note 6)                     | 5V <sub>P-P</sub>                               | 25                         | -                    | 1.5  | 1.7                  | ns    |

| Rise/Fall Time Match (Note 6)                         |                                                 | 25                         | -                    | 50   | 150                  | ps    |

| Minimum Pulse Width (Note 16)                         | 1V <sub>P-P</sub>                               | 25                         | -                    | 1.0  | -                    | ns    |

| Minimum Pulse Width (Note 16)                         | 3V <sub>P-P</sub>                               | 25                         | -                    | 1.2  | -                    | ns    |

| Minimum Pulse Width (Note 16)                         | 5V <sub>P-P</sub>                               | 25                         | -                    | 2.0  | -                    | ns    |

| Overshoot/Undershoot/Preshoot                         | 3V <sub>P-P</sub>                               | 25                         | -                    | 5    | -                    | %     |

| Data Settling Time to 1% (Note 3)                     |                                                 | 25                         | -                    | 10   | -                    | ns    |

| OUTPUT CHARACTERISTICS                                |                                                 |                            | 1 1                  |      |                      |       |

| Output Voltage Swing (No Load)                        | V <sub>CC</sub> = 10V, V <sub>EE</sub> = -5.2V  | 25                         | -2                   | -    | 7                    | V     |

|                                                       | At Other Supplies                               | 25                         | V <sub>EE</sub> +3.2 | -    | V <sub>CC</sub> -3.0 | V     |

| DC Output Resistance - Active (Note 18)               | -2V to 7V                                       | 25                         | 45                   | 47   | 49                   | Ω     |

| Output Leakage - HiZ                                  | -2V to 7V                                       | 25                         | -100                 | ±10  | 100                  | nA    |

| Output Capacitance - HiZ                              |                                                 | 25                         | -                    | 5    | -                    | pF    |

| Output Current - Active                               |                                                 | 25                         | 70                   | 100  | -                    | mA    |

| POWER SUPPLY CHARACTERISTICS                          |                                                 |                            | 1 1                  |      |                      |       |

| Power Supply Rejection Ratio (Note 4)                 | V <sub>HIGH</sub>                               | 25                         | -                    | 14   | 40                   | mV/V  |

|                                                       | V <sub>LOW</sub>                                | 25                         | -                    | 14   | 40                   | mV/V  |

| Total Supply Current                                  |                                                 | 25                         | 90                   | 94   | 96                   | mA    |

| Supply Current (I <sub>CC1</sub> , I <sub>EE1</sub> ) |                                                 | 25                         | -                    | 74   | -                    | mA    |

| Supply Current (I <sub>CC2</sub> , I <sub>EE2</sub> ) |                                                 | 25                         | -                    | 20   | -                    | mA    |

| Supply Voltage Range (Note 5)                         | V <sub>CC</sub>                                 | 25                         | 9.8                  | 10   | 10.2                 | V     |

| Supply Voltage Range (Note 5)                         | V <sub>EE</sub>                                 | 25                         | -5.4                 | -5.2 | -5.0                 | V     |

| Supply Voltage Differential                           | V <sub>CC</sub> - V <sub>EE</sub>               | 25                         | 12                   | -    | 15.6                 | V     |

| Power Dissipation                                     | No Load At $V_{CC} = 10V$ ,<br>$V_{EE} = -5.2V$ | 25                         | -                    | -    | 1.46                 | W     |

#### Electrical Specifications V<sub>CC</sub> = +10V, V<sub>EE</sub> = -5.2V, V<sub>IH</sub> = -0.9V, V<sub>IL</sub> = -1.75V, Unless Otherwise Specified (Continued)

NOTES:

- 1. Internal Power Dissipation may limit Output Current below 160mA.

- 2. 3V Step, 50% duty cycle, 200ns period.

- 3. 3V Step, measured from 50% of input to  $\pm 1\%$  of reference value at 50ns.

- 4.  $V_{HIGH} = 2.6V$ ,  $V_{LOW} = 2.3V$ ,  $V_{CC} = 9V$  to 10V,  $V_{EE} = -4.2V$  to -5.2V

- 5. Minimum/maximum output swing will vary with supply voltage.

- 6. 5V Step, 50% duty cycle, 100ns period.

- 7. For  $V_{HIGH} = 0V$  to 5V, For  $V_{LOW} = 0V$  to 5V, Fullscale = 5V, 0.1% = 5mV.

- 8. For  $V_{HIGH}$  = -1.5V to 7V, For  $V_{LOW}$  = -2.0V to 6.5V, Fullscale = 8.5V, 0.1% = 8.5mV

- 9. Shorting the output to a voltage outside the specified range may damage the output.

10.  $V_{CC} = 9.9V$ ,  $V_{EE} = -5.1V$ .

- 11. V<sub>HIGH</sub> to V<sub>LOW</sub> Interaction is measured as the change in V<sub>OUT</sub> (the active channel) due to a change in the inactive channel. V<sub>HIGH</sub> Interaction at 250mV is measured as the deviation from 1V as V<sub>LOW</sub> is changed from 0V to 750mV (Referred to V<sub>OUT</sub>). V<sub>Low</sub> Interaction at 250mV is measured as the deviation from 0V as V<sub>HIGH</sub> is changed from 1V to 250mV (Referred to V<sub>OUT</sub>).

- 12. 0V to 3V Step, 200ns period, Pulse Width is varied from 5ns to 195ns.

- 13. End Point Gain Deviation is the percent deviation of Gain calculated in 0.5V steps at the extremes of output voltage range. For example in the  $V_{HIGH}$  range 5.7V to 6.7V, Gain is calculated for  $V_{HIGH}$  = 5.7V to 6.2V (Note 15) and  $V_{HIGH}$  = 6.2V to 6.7V (Note 15) the difference in gain is calculated and converted to a percentage. The voltage ranges tested are:  $V_{HIGH}$  = -1.5V to -0.5V (Note 15) and 5.7V to 6.7V (Note 15),  $V_{LOW}$  = -2.0V to -1.0V (Note 15) and 5.5V to 6.5V (Note 15).

- 14. VHIGH End Point Gain Error is the VOUT absolute error from ideal for a VHIGH change from 6.7V to 7.0V (Note 15).

- 15. Input voltages V<sub>HIGH</sub> and V<sub>LOW</sub> are corrected for Offset Voltage and 7.5V Full Scale Gain Error.

- 16. Minimum Pulse Width is measured 50% to 50% of specified amplitude with pulse peak at 90% of amplitude.

- 17. Test is performed into a  $50\Omega$  load with a 3V step. Measurement is made from the 50% of input to 50% of output.

- 18. Dynamic Output Resistance will be higher (typical  $48.5\Omega$ ) than DC Output Resistance.

# Application Information

The HFA5251 is a pin driver designed for use in automatic test equipment (ATE) and high speed pulse generators. Pin drivers, especially those with very high-speed performance, have generally been implemented with discrete transistors (sometimes GaAs) on a circuit board or in a hybrid. Recent IC process improvements, specifically Intersil's UHF1 process [1], have enabled the manufacturing of this 800MHz silicon monolithic pin driver.

The ultra high speed performance of the HFA5251 is a result of UHF1 process leverages: low parasitic collector-to-substrate capacitance of the bonded wafer, low collector-to-base parasitic capacitance of the self-aligned base/emitter technology and ultra high f<sub>T</sub> NPN (8GHz) and PNP (5.5GHz) poly-silicon transistors.

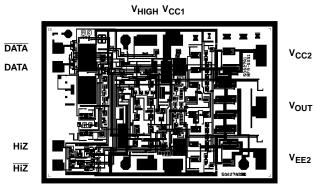

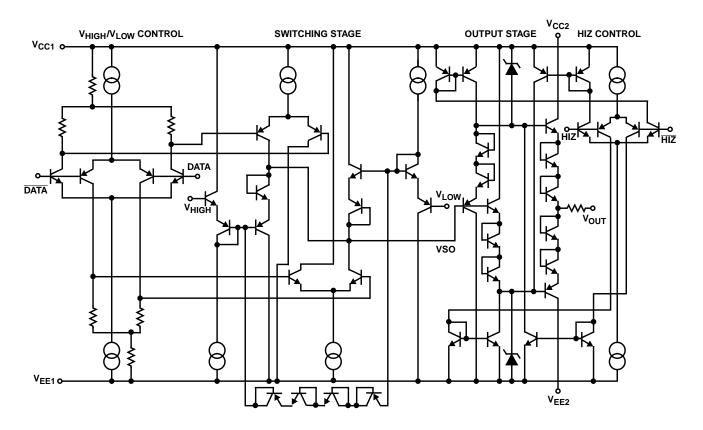

# Functional Block Diagram

The HFA5251 functional block diagram is shown in Figure 1.

FIGURE 1. BLOCK DIAGRAM

The control inputs, DATA and DATA, determine the output level. If DATA is at logic "1" and DATA is at logic "0", the output level will be the same as  $V_{HIGH}$ . If DATA is at logic "0" and DATA is at logic "1", the output will be the same as  $V_{LOW}$ . The control inputs, HiZ and HiZ, make the output either active or high-impedance. If HiZ is at logic "1" and HiZ is at logic "0", the output will be in high impedance mode. If HiZ is at logic "0" and HiZ is at logic "0" and HiZ is at logic "1", the output will be inhigh impedance mode. If HiZ is at logic "0" and HiZ is at logic "1", the output will be inhigh impedance mode. If HiZ is at logic "0" and HiZ is at logic "0".

# **Circuit Schematic**

The Pin Driver circuit consists of a switch, an output buffer, and two differential control elements as shown in Figure 2.

A two stage approach, separating the switch from the output buffer, allows the speed and accuracy requirements of the switch to be de-coupled from the load driving capability of the buffer.

The patent pending switch circuitry[2] uses cascaded emitter followers as input buffers and also to switch the input V<sub>HIGH</sub> and V<sub>LOW</sub> to node VSO. Dual differential pairs controlled by the data timing (DATA and DATA) direct current to select either the V<sub>HIGH</sub> or V<sub>LOW</sub> switch. Matching transistor types and transdiodes improve linearity and lowers the voltage

5

offset and offset drift. Stacking two emitter-base junctions allows the V<sub>HIGH</sub> to V<sub>LOW</sub> range to be extended to two BVebo's of the process. The speed of the pin driver is largely determined by the current flowing through the switch stage and the collector-base capacitance of the output stage transistors connected to the node VSO.

The output stage consists of cascaded emitter followers constructed in a typical push-pull manner as shown in Figure 2. However, transdiodes are added to increase the voltage breakdown characteristics of the output during high impedance mode. HiZ and HiZ control the mode of the output stage. A trimmed, NiCr resistor is added to provide the  $50\Omega$  output impedance.

Overall, a symmetry of device types and paths is constructed to improve slew and delay symmetry. Both the  $V_{HIGH}$  to  $V_{OUT}$  path and the  $V_{LOW}$  to  $V_{OUT}$  path contain three NPN and three PNP transistors operating at similar collector currents. Thus the transient response of  $V_{HIGH}$  to  $V_{LOW}$  and  $V_{LOW}$  to  $V_{HIGH}$  are kept symmetrical. Also, a trimmable current reference (not shown) allows the AC parameters to be adjusted to maintain unit to unit consistency.

# Speed Advantage

Intersil Pin Drivers on bonded-wafer technology definitely have a speed advantage, coming from the low collector-tosubstrate capacitance and the high  $f_T$  of the transistors. In addition, the patent-pending switching stage which fits uniquely to Intersil's UHF1 process is another big contributor for the high speed. This switching circuitry requires low seriesresistance NPN and PNP transdiodes available in UHF1. The rise and fall times of the pin driver are largely determined by the slew rate at the node VSO in Figure 2. The dominant mechanism for the slew rate is the charging/discharging of the collector-base capacitors of the transistors connected to the node VSO. The charging/discharging currents are coming from the switching stage current sources. The fast rise and fall times are achieved because of the negligible collector-tosubstrate capacitance and the small base-collector capacitance due to the self-aligned recessed oxide [1].

The DATA/DATA differential stage is not a factor for the speed if its current sources have enough current not to bottleneck the transient. However it should be noted that the propagation delay mismatch is determined by this stage. Sufficient current is allocated to the differential stage current sources to best match the low-to-high and high-to-low transient propagation delays.

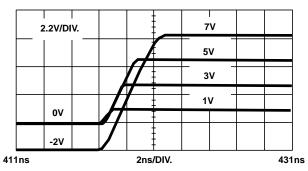

Figure 3 shows various output responses, 0V to 1V, 0V to 3V, 0V to 5V, and -2V to 7V (full swing). The load condition is a 16 inch 50 $\Omega$  SMA cable with a 5pF capacitor at the end of the cable. The rise/fall time with 5V<sub>P-P</sub> is typically 1.45ns for the HFA5251. Pin drivers, built out of the same circuit structure as shown in Figure 2, can be made faster by trimming for a

6

higher power supply current. Currently the pin driver has rise/fall times of less than 1ns (10% to 90% of  $5V_{P-P}$ ) when  $I_{CC}$  is trimmed to 125mA. Further speed enhancement will be made if there is a market demand.

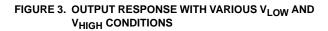

# **Basic ATE System Application**

Figure 3 shows a pin driver in a typical per-pin ATE system. The pin driver works closely with the dual-level comparator and the active load. When the DUT pin acts as an input waiting for a series of digital signals, the pin driver becomes active with a logic "0" applied on the HiZ pin and provides the DUT pin with digital signals. When the DUT pin acts as an output, the pin driver output will be in high impedance mode (HiZ) with a logic "1" applied to the "HiZ" pin of the pin driver. During this high impedance mode the pin driver presents a capacitance of less than 5pF to the DUT. Special care has to be taken to match the impedance (to  $50\Omega$ ) at the pin driver output to minimize reflections.

The dual level comparator detects the logic levels of the DUT pin when it acts as an output. The comparator has two threshold level inputs, VCH and VCL. The logic level information of DUT pin output is sent to the edge/window comparator through the dual level comparator. The edge/window comparator interprets this information in terms of corresponding transient performance in conjunction with the timing information. Thus it detects any possible failure transients.

The formatter sends a sequence of digital information to the pin driver which contains logic information over time. The active load is enabled when the DUT pin acts as an output. It simulates the load of the DUT pin by sinking or sourcing programmed current. Finally the sequencer controls the overall activities of the automatic testing.

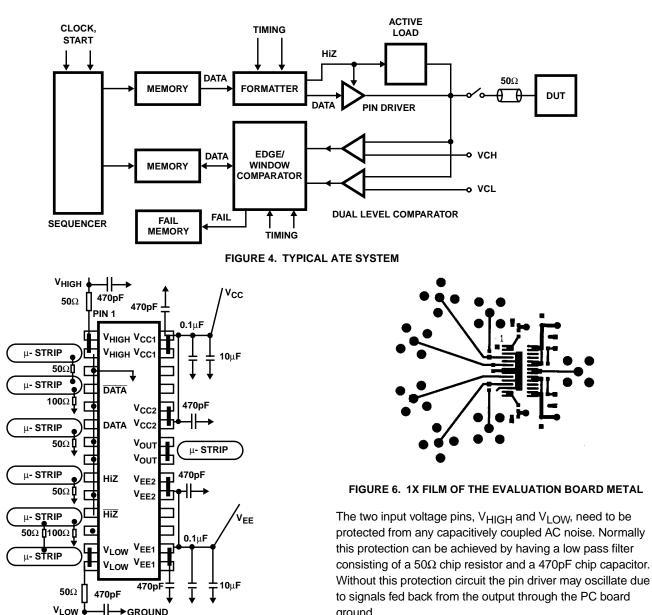

## Decoupling Circuit for Oscillation-Free Operation

To insure the oscillation-free operation in ATE or pulse generator applications, the pin driver needs an appropriate decoupling circuit on a printed circuit board which consists of chip capacitors and chip resistors. Figures 5 and 6 refer to a proven decoupling circuit currently working in the lab and a 1X scale film of its associated PC board (metal level).

The control pins, DATA, DATA, HiZ, and HiZ are fed ECL signals through  $50\Omega$  micro-strip lines terminated with  $50\Omega$  for impedance matching since the input impedance at these pins is much higher than  $50\Omega$ . At the end of the micro-strip lines there is usually a high-speed pulse generator with an output impedance of 50 $\Omega$ . A 50 $\Omega$  micro-strip line is connected to each of the pins,  $\overline{\text{DATA}}$  and  $\overline{\text{HiZ}}$  through a 50 $\Omega$ chip resistor to monitor the pulse signals.

ground.

essential since large AC current will flow through either  $V_{CC2} \mbox{ or } V_{EE2}$  during transients.

The output of the pin driver is usually connected to the device-under-test (DUT) through  $50\Omega$  micro-strip line and coaxial cable which carries the signal to a high input impedance DUT pin.

## References

- 1. Chris K. Davis et. al., "UHF1: A High Speed Complementary Bipolar Analog Process on SOI," Bipolar Circuits and Technology Meeting Proceedings, pp260-263, October 1992.

- Donald K. Whitney Jr., "Symmetrical, High Speed, Voltage Switching Circuit," United States Patent Pending, Filed November 1991.

## **Definition of Terms**

## V<sub>OH</sub> and V<sub>OL</sub>

Output High Voltage and Output Low Voltage. V<sub>OH</sub> is the voltage at V<sub>OUT</sub> when the HiZ input is Low and the DATA input is High. V<sub>OL</sub> is the voltage at V<sub>OUT</sub> when HiZ is Low and DATA is Low. The V<sub>OH</sub> and V<sub>OL</sub> levels are set with the V<sub>HIGH</sub> and V<sub>LOW</sub> inputs respectively.

## Offset Voltage

Offset Voltage is the DC error between the voltage placed on V<sub>HIGH</sub> or V<sub>LOW</sub> and the resulting V<sub>OH</sub> and V<sub>OL</sub>. V<sub>HIGH</sub> Offset Voltage Error is obtained by measuring V<sub>OH</sub> with V<sub>HIGH</sub> set to 0V and V<sub>LOW</sub> set to -2.5V to minimize interaction effects. V<sub>LOW</sub> Offset Voltage Error is the measurement of V<sub>OL</sub> with V<sub>LOW</sub> set to 0V and V<sub>HIGH</sub> set to +7.5V.

## Gain

Gain is defined as the ratio of output voltage change to input voltage change for a defined range. V<sub>HIGH</sub> Gain is calculated with the following equation with V<sub>LOW</sub> fixed at -2.5V

$$V_{\text{HIGH}}\text{GAIN} = \frac{V_{\text{OH}}(V_{\text{HIGH}} \text{ at } 6.5\text{V}) - V_{\text{OH}}(V_{\text{HIGH}} \text{ at } -1\text{V})}{7.5}$$

V<sub>LOW</sub> Gain is calculated in a similar manner.

$$V_{LOW}GAIN = \frac{V_{OL}(V_{LOW} \text{ at } 6V) - V_{OL}(V_{LOW} \text{ at } -1.5V)}{7.5}$$

$V_{\mbox{HIGH}}$  is held fixed at 7.5V. These Gain calculations minimize the effects of Interaction and End Point Nonlinearities.

## Linearity Error

Linearity Error is a measure of output voltage worst case deviation from a straight line that has been corrected for offset and 7.5V Gain. Linearity Error is given as a percentage of fullscale and is done in two ranges 5V and 8.5V. Data is measured at 0.5V steps from -1.5V to 7V for  $V_{HIGH}$  and -2V to 6.5V for  $V_{LOW}$ . The Linearity Error equation is as follows for 8.5V fullscale:

$$V_{OUT}(IDEAL) = \frac{V_{OUT}}{GAIN} - OFFSET$$

$$\mathsf{LINEARITYERROR} = \frac{\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{OUT}}(\mathsf{IDEAL})}{8.5}$$

The Linearity Error equation is as follows for 5V fullscale:

$$\mathsf{LINEARITY} \; \mathsf{ERROR} \; = \; \frac{\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{OUT}}(\mathsf{IDEAL})}{5}$$

Linearity Error is calculated for every data point in the range and the worst case value is recorded.

#### **End Point Deviation**

End Point Deviation is the percent change of gain in the 1V range at the extremes of output voltage. Gain is calculated for each 0.5V step and then compared to the adjacent step for a percentage change. This specification is designed to quantify the amount of curvature present at the end points of output swing.  $V_{HIGH}$  and  $V_{LOW}$  inputs are corrected for gain and offset to provide more accurate  $V_{OH}$  and  $V_{OL}$  levels. For example  $V_{OH}$  End Point Deviation is tested in the range 5.7V to 6.7V as shown below:

$$\begin{aligned} & \text{GAIN}_{6.7-6.2} = \frac{\text{V}_{\text{OH}}(\text{V}_{\text{HIGH}} \text{ at } 6.7\text{V}) - \text{V}_{\text{OH}}(\text{V}_{\text{HIGH}} \text{ at } 6.2\text{V})}{0.5} \\ & \text{GAIN}_{6.2-5.7} = \frac{\text{V}_{\text{OH}}(\text{V}_{\text{HIGH}} \text{ at } 6.2\text{V}) - \text{V}_{\text{OH}}(\text{V}_{\text{HIGH}} \text{ at } 5.7\text{V})}{0.5} \\ & \text{END POINT DEVIATION} = |\text{GAIN}_{6.7-6.2} - \text{GAIN}_{6.2-5.7}| \times 100 \end{aligned}$$

# End Point Gain Error

End Point Gain Error (EPGE) is the  $V_{OUT}$  absolute error in millivolts for a  $V_{HIGH}$  change from 6.7V to 7V. The  $V_{HIGH}$  input is corrected for gain and offset to provide a more accurate  $V_{OH}$  level.

$EPGE = V_{OH} (V_{HIGH} \text{ at } 7V) - V_{OH} (V_{HIGH} \text{ at } 6.7V) - 0.3$

## V<sub>HIGH</sub> to V<sub>LOW</sub> Interaction

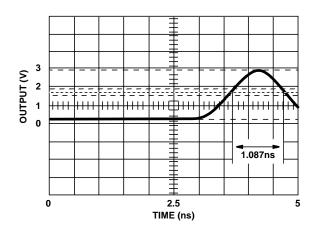

$V_{HIGH}$  to  $V_{LOW}$  Interaction is the change in  $V_{OUT}$  (the active channel) due to the inactive channel.  $V_{HIGH}$  Interaction is measured as the change in  $V_{OH}$  from 1V as  $V_{LOW}$  is moved from 0V to 750mV ( $V_{LOW}$  is corrected for gain and offset errors).  $V_{LOW}$  Interaction is measured as the change in  $V_{OL}$  from 0V as  $V_{HIGH}$  is moved from 1V to 250mV (with  $V_{HIGH}$  corrected for gain and offset errors). The minimum recommended difference between  $V_{HIGH}$  and  $V_{LOW}$  for the HFA5251 is 250mV.

## **Typical Performance Curves**

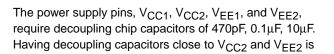

FIGURE 7. LARGE SIGNAL RESPONSE

FIGURE 9. MINIMUM PULSE WIDTH

FIGURE 11. V<sub>HIGH</sub>/V<sub>LOW</sub> INTERACTION, V<sub>HIGH</sub> ACTIVE (NOMINAL 1.0V)

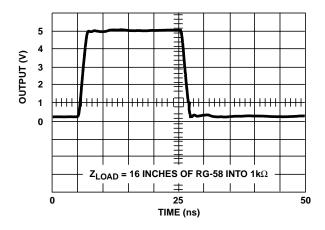

FIGURE 8. SMALL SIGNAL RESPONSE

FIGURE 10. GAIN ERROR (FULLSCALE = 8.5V)

FIGURE 12. V<sub>HIGH</sub>/V<sub>LOW</sub> INTERACTION, V<sub>LOW</sub> ACTIVE (NOMINAL 0.0V)

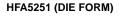

## **Die Characteristics**

## DIE DIMENSIONS:

2670μm x 1730μm x 525μm

#### **METALLIZATION:**

Type: Metal 1: Cu (2%) SiAl/TiW Thickness: Metal 1: 8kÅ ±0.4kÅ Backside: Gold

Type: Metal 2: Cu (2%) Al

Thickness: Metal 2: 16kÅ ±0.8kÅ

## Metallization Mask Layout

PASSIVATION: Nitride, 4kÅ ±0.5kÅ

### TRANSISTOR COUNT:

115

## SUBSTRATE POTENTIAL:

Floating

HFA5251

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

## Sales Office Headquarters

NORTH AMERICA Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (321) 724-7000 FAX: (321) 724-7240 EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ASIA Intersil (Taiwan) Ltd. 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029

## <u>intersil</u>