Data Sheet November 2000 File Number 3018.5

# Quad Inverting Power Drivers with Serial Diagnostic Interface

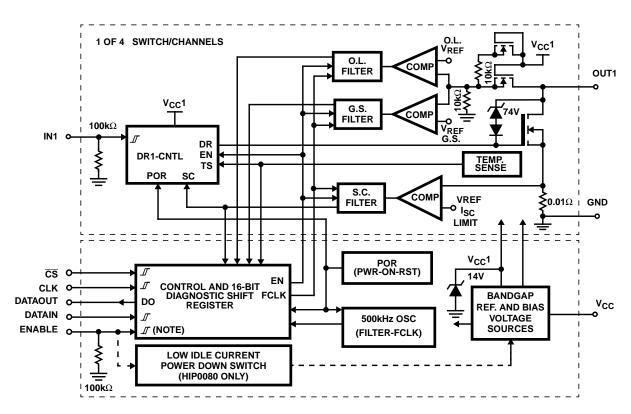

The HIP0080/0081 Quad Power Drivers contain four individually protected NDMOS power output transistor switches to drive inductive and resistive loads such as: relays, solenoids, injectors, AC and DC motors, heaters and incandescent lamp displays. The 4 Power Drivers are low-side switches driven by CMOS logic input control stages. Each Output Power Driver is protected against over-current, over-temperature and over-voltage. An internal drain-to-gate zener diode provides the clamping protection for over-voltage. Diagnostic circuits provide ground short, supply short, open load and thermal overload detection for each of the 4 output stages. Each of the 4 input drivers and their respective diagnostic filters are controlled by one ENABLE input.

The inputs are CMOS logic compatible and individually control the output drivers with an active high state for turnon. All other control inputs are active high with the exception of the Chip Select  $(\overline{\text{CS}})$  which is active low. The DATAIN (DI) and DATAOUT (DO) are positive logic and the Clock (CLK) input for the Serial Interface is active on the rising edge of the CLK pulse. All Inputs except the HIP0080 ENABLE have a nominal level of hysteresis. IN1, IN2, IN3, IN4 and ENABLE have pull-down resistors of approximately  $100 \text{k}\Omega$ . This switches off any channel that has an unterminated input.

Filters are used on the outputs of the fault sensing comparators to avoid the detection of short duration transient spikes. The on-chip oscillator is used to clock an internal shift register in each filter. If the fault condition is longer than a preset number of clock cycles, the fault condition is recognized and the respective bit is set in the diagnostic register. No filter is used in the thermal-overload feedback circuit and the bit is set when thermal shutdown occurs.

For normal operating conditions, a Reset turns off all outputs when the  $V_{CC}$  level drops below 3.5V. The internal bandgap and bias supply function includes a 5V regulated supply for the low voltage signal and logic circuits.

#### **Features**

- · Low Side Power MOSFET Output Drivers

- Output Driver Protection

- Over-Current Shutdown

- Over-Temperature Shutdown with Hysteresis

- Over-Voltage Internal Clamp

- HIP0081 Output Current Switching Capability:

- All Outputs ON, Equal I<sub>OUT</sub> . . . . . . . 8A PK, 500ms

- HIP0080 Output Current Switching Capability:

- All Outputs ON, Unequal I<sub>OUT</sub> . . . . . . . . . . . . 3A DC

- All Outputs ON, Unequal I<sub>OUT</sub> . . . . . . . 4A PK, 500ms

- HIP0080 Low Idle Current Shutdown Mode

- Regulated Interface for 5V CMOS Logic Inputs

- Open Drain High Z DATAOUT

- Fault Mode Output for Shorts, Opens and Over-Temperature

- 16-Bit Serial Diagnostic Register

- SPI Bus Compatible Data Readout

- HIP0081 Low θ<sub>JC</sub> Power Package . . . . . . . . . 3°C/W

- -40°C to 125°C Operating Temperature Range

## **Applications**

- Drivers For:

- Injectors

- System Use:

- SolenoidsRelays

- Stoppore

- Automotive

- Itelays

- Steppers

- Appliances

- Power Output

- Motors

- Industrial

- Lamps

- Displays

- Robotics

# **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |

|-------------|---------------------|------------|-------------|

| HIP0081AS1  | -40 to 125          | 15 Ld SIP  | Z15.05A     |

| HIP0081AS2  | -40 to 125          | 15 Ld SIP  | Z15.05B     |

| HIP0080AM   | -40 to 125          | 28 Ld PLCC | N28.45      |

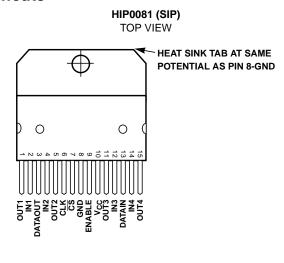

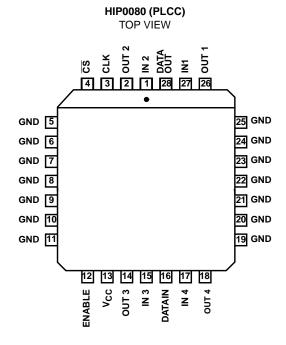

### **Pinouts**

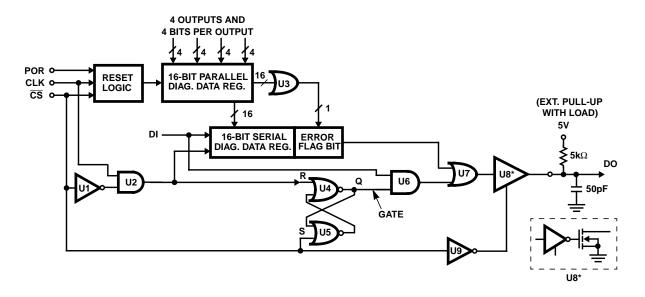

## Functional Block Diagram

NOTE: HIP0080 - No enable hysteresis.

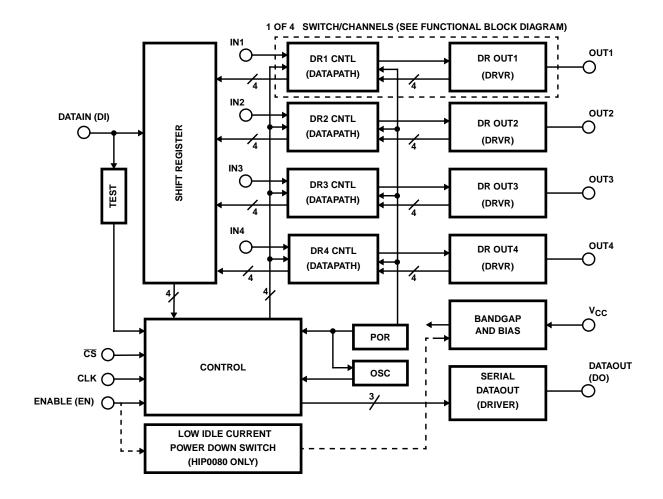

# Functional Signal Flow Diagram

#### **Absolute Maximum Ratings**

| Supply Voltage (Logic and Control), V <sub>CC</sub> 16 to 45V      |

|--------------------------------------------------------------------|

| Power MOSFET Drain Voltage, VO (Note 1)0.5 to V <sub>CLAMP</sub>   |

| Maximum Output Clamp Energy, E <sub>OK</sub> (HIP0080) Note 4      |

| Maximum Output Clamp Energy, E <sub>OK</sub> (HIP0081) Note 4      |

| Input Voltage (Logic and Driver Inputs), V <sub>IN</sub> 0.5 to 7V |

| Output Voltage, DATAOUT0.5 to 7V                                   |

| HIP0080 Output Current                                             |

| Each Output, IOUT(PEAK), (Note 2)1.5A to IOUT(SC)                  |

| Each Output, IOUT(DC) ····································         |

| Total of 4 Outputs ON, Unequal IOUT +3A                            |

| Total of 4 Outputs ON, Unequal IOUT +4A/500ms (Max)                |

| HIP0081 Output Current                                             |

| Each Output, IOUT(PEAK), (Note 2)2 to IOUT(SC)                     |

| Each Output, IOUT(DC) +2.2A                                        |

| Total of 4 Outputs, ON, Unequal IOUT+6A                            |

| Total of 4 Outputs ON, Unequal IOUT +8A/500ms (Max)                |

|                                                                    |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 3)       | $\theta_{JA}(^{O}C/W)$ | $\theta_{JC}(^{o}C/W)$                |

|--------------------------------------------|------------------------|---------------------------------------|

| HIP0080                                    | 43                     | N/A                                   |

| HIP0080 (on 2 sq. in. PC Board)            | 33                     | N/A                                   |

| HIP0081                                    | 45                     | 3                                     |

| HIP0080 Power Dissipation with a 2 sq. in  | . PC Board H           | leat Sink:                            |

| At 85°C                                    |                        | 1.95W                                 |

| Above 85°C:De                              | rate Linearly          | at 30mW/OC                            |

| HIP0081 Power Dissipation with Infinite He | eat Sink:              |                                       |

| At 125°C                                   |                        | 8.33W                                 |

| Above 125 <sup>o</sup> C Dera              | ate Linearly a         | t 333 mW/ <sup>o</sup> C              |

| Maximum Storage Temperature Range, T       | STG55                  | <sup>50</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 1      | 0s)                    | 300°C                                 |

|                                            |                        |                                       |

| Die Characteristics                        |                        |                                       |

HIP0080 Back Side Potential ...... Frame, GND Leads HIP0081 Back Side Potential ..... Heat Sink Tab, GND Lead

#### **Operating Conditions**

| Ambient Temperature Range  | <br>-40°C to 125°C |

|----------------------------|--------------------|

| Junction Temperature Range | <br>-40°C to 150°C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- The MOSFET Output Drain is internally Clamped with a Drain-to-Gate zener diode that turns-on the MOSFET to hold the Drain at the V<sub>CLAMP</sub> voltage. Refer to the Electrical Characteristic Tables for the V<sub>CLAMP</sub> voltage limits.

- 2. Each Output has Over-Current Shutdown protection in the positive current direction. The maximum peak current rating is determined by the minimum Over-Current Shutdown as detailed in the Electrical Specification Table. In the event of an Over-Current Shutdown the input drive is latched OFF. The output short must be removed and the input toggled OFF and ON to restore the output drive.

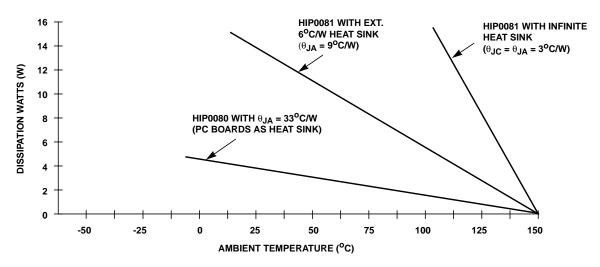

- Effective Heat Sinking for the HIP0080 PLCC package requires a PC Board solder mount or equivalent. The HIP0080 θ<sub>JA</sub> junction-to-air thermal resistance is given for a PC Board with 2 sq. in. of 1 oz. surface mount ground copper extending away from the package. For additional Power Dissipation Derating information, see Figure 8 curves.

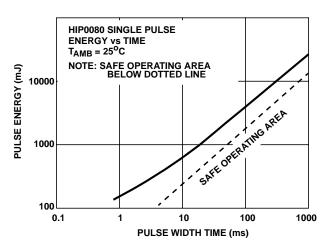

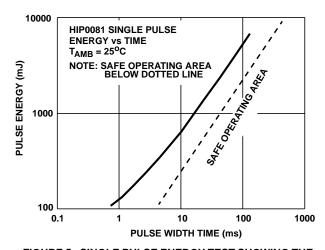

- 4. Refer to Figures 4 and 5 Single Pulse Output Clamp Energy vs. Time Capability of the HIP0080 and HIP0081. The safe margin for single pulse energy operation is below the dotted line shown in Figures 4 and 5.

#### **Electrical Specifications** $V_{CC} = 5.5V \text{ to } 25V \pm 5\%$ , $T_A = -40^{\circ}\text{C}$ to $125^{\circ}\text{C}$ , Unless Otherwise Specified

|                                   |                    |                                                                                                                                      | HIP0080 |     | ı   | HIP0081 |      |     |       |

|-----------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|---------|------|-----|-------|

| PARAMETER                         | SYMBOL             | TEST CONDITIONS                                                                                                                      | MIN     | TYP | MAX | MIN     | TYP  | MAX | UNITS |

| POWER OUTPUTS                     |                    |                                                                                                                                      |         |     |     |         |      |     |       |

| Output ON Resistance<br>(HIP0081) | ron                | $V_{CC}$ = 10 to 25V, All Outputs ON<br>$I_{OUT1}$ = $I_{OUT2}$ = $I_{OUT3}$ = $I_{OUT4}$ = 1A                                       | -       | -   | -   | -       | -    | 0.5 | Ω     |

|                                   |                    | $V_{CC}$ = 5.5 to 10V, All Outputs ON $I_{OUT1}$ = $I_{OUT2}$ = $I_{OUT3}$ = $I_{OUT4}$ = 0.7A                                       | -       | -   | -   | -       | -    | 1.0 | Ω     |

| Output ON Resistance<br>(HIP0080) | r <sub>ON</sub>    | $V_{CC}$ = 10 to 25V, All Outputs ON<br>$I_{OUT1}$ = $I_{OUT2}$ = $I_{OUT3}$ = $I_{OUT4}$ = 0.5A                                     | -       | -   | 1.0 | -       | -    | -   | Ω     |

|                                   |                    | V <sub>CC</sub> = 5.5 to 10V, All Outputs ON<br>I <sub>OUT1</sub> = I <sub>OUT2</sub> = I <sub>OUT3</sub> = I <sub>OUT4</sub> = 0.4A | -       | -   | 2.0 | -       | -    | -   | Ω     |

| HIP0081 Output Off Current        | loff               | Inputs Low, Each $V_{OUT} = 60V$<br>$T_A = 25^{\circ}C$ to $125^{\circ}C$                                                            | -       | -   | -   | -       | 0.75 | 1.0 | mA    |

|                                   |                    | Inputs Low, Each V <sub>OUT</sub> = 60V, T <sub>A</sub> = -40°C                                                                      | -       | -   | -   | -       | 0.75 | 1.5 | mA    |

| HIP0081 Output Leakage<br>Current | I <sub>OFFLK</sub> | Inputs Low, Each $V_{OUT} = 60V$ , $V_{CC} = 0V$                                                                                     | -       | -   | -   | -       | 1.0  | 10  | μΑ    |

## HIP0080, HIP0081

## **Electrical Specifications** $V_{CC} = 5.5 V$ to $25 V \pm 5\%$ , $T_A = -40 ^{o}C$ to $125 ^{o}C$ , Unless Otherwise Specified (Continued)

|                                            |                      |                                                                                         | HIP0080 |                          |      | HIP0081 |                          |      |       |

|--------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|---------|--------------------------|------|---------|--------------------------|------|-------|

| PARAMETER                                  | SYMBOL               | TEST CONDITIONS                                                                         | MIN     | TYP                      | MAX  | MIN     | TYP                      | MAX  | UNITS |

| HIP0080 Output Off<br>Current              | l <sub>OFF</sub>     | Inputs Low, Each V <sub>OUT</sub> = 25V,<br>ENABLE High, T <sub>A</sub> = 25°C to 125°C |         | 0.75                     | 1.0  | -       | -                        | -    | mA    |

|                                            |                      | Inputs Low, Each V <sub>OUT</sub> = 25V,<br>ENABLE High, T <sub>A</sub> = -40°C         |         | 0.75                     | 1.5  | -       | -                        | -    | mA    |

| HIP0080 Output Leakage<br>Current          | IOFFLK               | Inputs Low, Each V <sub>OUT</sub> = 25V,<br>ENABLE Low                                  | -       | 1.0                      | 10   | -       | -                        | -    | μА    |

| Over-Voltage Clamp Range                   | V <sub>CLAMP</sub>   | IN Inputs Low (Outputs OFF), I <sub>OUT</sub> = 40mA                                    | 27      | -                        | 43   | 73      | -                        | 89   | V     |

| Current Short Circuit Prot.                | I <sub>OUT(SC)</sub> | Note 2                                                                                  | 1.3     | -                        | 3    | 2.2     | -                        | 4.8  | Α     |

| Short Circuit Det. Delay                   | tSCDLY               |                                                                                         | -       | 6                        | -    | -       | 6                        | -    | μs    |

| Output ON-OFF Voltage<br>Ramp Rate         |                      | Resistive Load                                                                          | -       | 10                       | -    | -       | 10                       | -    | V/µs  |

| Turn-On Delay                              | t <sub>PHL</sub>     | $_{\rm CC}$ = 14V, $R_{\rm LOAD}$ = 14 $\Omega$                                         |         | -                        | 8    | -       | -                        | 8    | μs    |

| Turn-Off Delay                             | t <sub>PLH</sub>     | $V_{CC} = 14V, R_{LOAD} = 14\Omega$                                                     | -       | -                        | 8    | -       | -                        | 8    | μs    |

| SUPPLY                                     |                      |                                                                                         |         |                          |      |         |                          |      |       |

| Power Supply Current                       | Icc                  |                                                                                         | -       | 20                       | 30   | -       | 20                       | 30   | mA    |

| Power Supply Reset Active                  | V <sub>CC_RST</sub>  | $T_A = 25^{\circ}C$ to $T_A = 125^{\circ}C$                                             | 3       | -                        | 4    | 3       | -                        | 4    | V     |

|                                            |                      | $T_A = -40^{\circ}C$                                                                    | 2.7     | -                        | 4    | 2.7     | -                        | 4    | V     |

| Shut-Down Current Mode                     | I <sub>SHTDN</sub>   | Enable Low                                                                              |         | 130                      | 200  | -       | -                        | -    | μΑ    |

| INPUTS                                     |                      |                                                                                         |         | •                        |      |         |                          |      |       |

| Low-Level Input Voltage                    | V <sub>IL</sub>      |                                                                                         | -       | -                        | 1    | -       | -                        | 1    | V     |

| High-Level Input Voltage                   | V <sub>IH</sub>      |                                                                                         | 3.5     | -                        | -    | 3.5     | -                        | -    | V     |

| Input Hysteresis Threshold                 | V <sub>IN_HYS</sub>  | (N.A. to HIP0080 ENABLE)                                                                | 0.85    | -                        | 2.25 | 0.85    | -                        | 2.25 | V     |

| Input Pull-Down Resistance                 | R <sub>PD</sub>      | IN1, IN2, IN3, IN4 and ENABLE                                                           | 50      | 100                      | 200  | 50      | 100                      | 200  | kΩ    |

| DATAOUT (Open Drain)                       |                      |                                                                                         |         |                          |      |         |                          |      |       |

| Leakage Current                            | I <sub>DO_LEAK</sub> | V <sub>DO</sub> = 7V, DO OFF (High)                                                     | -       | -                        | 10   | -       | -                        | 10   | μΑ    |

| Logic Low Output Voltage                   | V <sub>OL</sub>      | I <sub>DO</sub> = 1.6mA, DO ON (Low)                                                    | -       | -                        | 0.4  | -       | -                        | 0.4  | V     |

| Max. Logic Low Current                     | ГОН                  | V <sub>DO</sub> = 4.5V, DO ON                                                           | 1.6     | -                        | -    | 1.6     | -                        | -    | mA    |

| Oscillator Frequency                       | fosc                 |                                                                                         | -       | 500                      | -    | -       | 500                      | -    | kHz   |

| Serial Interface Clock Freq.               | f <sub>CLK</sub>     | Note 5                                                                                  | -       | -                        | 2    | -       | -                        | 2    | MHz   |

| DIAGNOSTIC AND PROTEC                      | TION                 |                                                                                         |         |                          |      |         |                          |      |       |

| Over-Temperature<br>Shutdown Threshold     |                      |                                                                                         | 150     | 165                      | -    | 150     | 165                      | -    | °C    |

| Shutdown Temperature<br>Hysteresis         |                      |                                                                                         | -       | 15                       | -    | -       | 15                       | -    | °C    |

| Output Short-to-GND<br>Threshold           |                      | V <sub>CC</sub> = 5.5V to 16V                                                           | -       | 0.24x<br>V <sub>CC</sub> | -    | -       | 0.24x<br>V <sub>CC</sub> | -    | V     |

| Short-to-GND Hysteresis                    |                      | V <sub>CC</sub> = 5.5V to 16V                                                           | -       | 0.02x<br>V <sub>CC</sub> | -    | -       | 0.02x<br>V <sub>CC</sub> | -    | V     |

| Open-Load Resistance for No-Load Warning   |                      | V <sub>CC</sub> = 5.5V to 16V                                                           | 5       | -                        | 25   | 5       | -                        | 25   | kΩ    |

| Filter Delay Time for O.L. or Short-to-GND |                      |                                                                                         | -       | 12                       | -    | -       | 12                       | -    | μs    |

#### NOTE:

5. The maximum Serial Clock Frequency may be limited by the time constant of the external load network at the DATAOUT pin.

#### Diagnostic Interface Overview

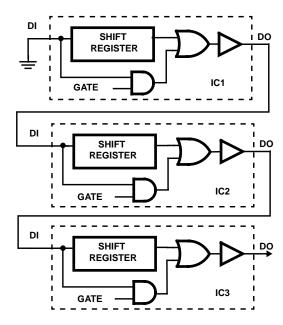

Each Quad Inverting Power Driver IC may be used as a single power switching driver, with or without the diagnostic interface. Where more than 4 Power Driver Switches are required, the HIP0080 or HIP0081 may be used in a multiple IC cascade connection. In cascade operation, the diagnostic data from all chips is read as a single serial sequence of fault bits. As shown in the Functional Block Diagram each output stage has voltage and temperature sensors to detect fault conditions while comparators and delay filters process the data. Four bits of diagnostic information is provided as fault feedback from each of the four output stages. When detected, the diagnostic data is put in a parallel diagnostic data register. Using the diagnostic control interface to address the system (one or more ICs in cascade), the fault data is transferred from the parallel diagnostic data register to a serial diagnostic data register as a sequence of 16 bits for each IC.

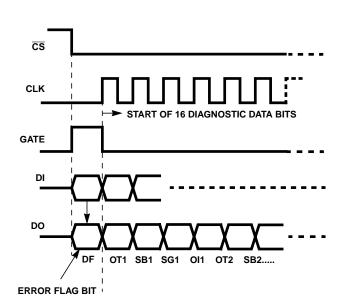

All diagnostic data bits may be read using the Chip Select (CS) and the Clock (CLK) inputs. The CLK input must be low, when CS goes active low. After reading the first bit at DO to determine if there is an error flag, the following 16 bits of serial diagnostic data may be clocked out of DO. Clocking the CLK input synchronously shifts the serial register data out of DO while cascaded data (from other devices or sources) is shifted into the DI input. As data is shifted out of DO, the parallel diagnostic data register is cleared on the first rising edge of the CLK input, following the CS low. After each 16 clocks, cascaded diagnostic data from the next IC in sequence is then shifted out of the DO output. Shifting the serial diagnostic data out of DO is done as a continuous sequence, reading the data from all ICs in cascade while  $\overline{\text{CS}}$  remains low. New diagnostic data can be stored in the parallel diagnostic data registers on each IC while the existing serial diagnostic data is read.

Referring to Figure 1 and Figure 2, there are two sources that generate an OR'ed Fault Flag at DO when  $\overline{CS}$  goes low. The two fault data sources are (1) the on-chip fault detection and (2) the off-chip DI input from front end ICs in the cascade. The fault data bit, labeled DF (Data Fault) in Figure 2, contains the OR'ed inputs from both sources. The DF bit is not part of the 16-bit serial diagnostic data sequence. In cascaded operation, the DI input for the first of the selected chips should be tied low. And, in single IC operation (no cascade), the DI input should also be tied low. In cascaded operation, the Error Flags are cascaded via the DI inputs.

The on-chip fault Error Flag goes high if any one of the 16 diagnostic data fault bits have been set HIGH. This fault Error Flag bit precedes the 16 diagnostic data fault bits and is OR'ed with all diagnostic data fault bits. The DF bit flags the presence of an Error Flag fault on the IC and in any part of the cascaded string, including DI data input. As shown in Figure 3 each IC in the cascade provides an output which is passed to the DI input of the following IC and is passed on as an OR'ed bit to the DO output of the last IC in the cascade. A fault condition is immediately evident without reading all diagnostic data bits.

However, all bits must be read to determine which chip and which diagnostic bit has been set. The Fault Flag is reset by the CLK input when the bits are read. When no fault condition is detected, it is not necessary to toggle the CLK input. When a fault is detected, at least one toggle of the clock is needed to reset the parallel diagnostic register which clears the register of all detected fault states.

The last IC in the string ORs its own 16 fault bits in the parallel diagnostic register data and sends this data bit to an Error Flag register. The Error Flag register outputs the presence of a fault in one or more bits of the parallel diagnostic data register. As shown in Figure 2, the Error Flag is the first bit in front of the serial register and is input to OR Gate, U7 with the DI input. The DI input passes through AND Gate, U6 when the GATE signal is high and output via the amplifier U8 to DO. The output amplifier U8 is active only while  $\overline{\text{CS}}$  is low. When  $\overline{\text{CS}}$  is low, the RS Flip-Flop drives the GATE output high. When the GATE is high, the cascaded DF bits are jammed from DI to DO. All Error Flags in the cascade are cleared (by the CLK input) when the serial diagnostic data is clocked out of DO.

The GATE is an internal control signal that is forced high when the CLK input is low and  $\overline{CS}$  goes low. The GATE will remain high, even when  $\overline{CS}$  is returned to a high state, provided the CLK input has not changed from a low state. This condition still applies when fault data is detected. The DO output is not latched; however, the Error Flag is latched when  $\overline{CS}$  goes low and will not be updated until the next time  $\overline{CS}$  goes low. The fault data is preserved as long as the CLK input does not go high. If the CLK is high when  $\overline{CS}$  goes low, the GATE will be disabled and no cascade data will be shifted from DI to DO. Under normal conditions, the CLK signal goes high to switch the GATE low and simultaneously shifts the first of 16 diagnostic data bits out of the serial diagnostic data register to DO. The  $\overline{CS}$  low input is not latched and must be held low while all data is shifted out of DO.

The diagnostic interfaces to the HIP0080 and HIP0081 are SPI compatible. The microcontroller is programmed to control the read and respond action based on the diagnostic readout. Normally the  $\overline{\text{CS}}$  input is addressed and DO is read. If a fault is indicated by the Error Flag, all data is shifted out of DO and processed to determine the diagnostic fault condition. The Error Flag bit does require a separate input back to the microcontroller to initiate the serial data shift. When the CLK signal starts, the serial sequence starting with the first of the 16 serial diagnostic bits is input to the microcontroller.

#### Serial Register Data Sequence

The fault data follows the Serial Register Data Sequence of Table 1 in bit sequence and, in cascade, by IC sequence. In each of the 4 power switching output channels, the diagnostic sense circuits set 1-bit in the parallel diagnostic register for each of the 4 diagnostics fault conditions. A total of 16 diagnostics data bits are shifted to the serial register when  $\overline{\text{CS}}$  goes low. Table 1 shows the order and sequence

of the serial bits as they are shifted out of DO. The fault action that sets each of the diagnostics bits for each of the 4 switches is described below:

Bit 1 - indicates a thermal overload when the sensed junction temperature of the output is greater than 150°C. When overtemperature is sensed, the sensor output directly gates-off the drive to the power output and the respective fault bit is set in the diagnostic register. When the chip is sufficiently cooled, the output is gated-on if the input remains ON.

Bit 2 - indicates the fault condition for an output-to-supply short (shorted load). A small value of resistance ( $\sim$ 0.01 $\Omega$ ) in the source-to-ground line of the output stage is used to sense the output short. A comparator senses the voltage level and filters the output to provide an input to the control stage and to the diagnostic register. The control state directly shuts down the output when an over-current condition is sensed. Under this condition of fault, the input driver is latched off. To restore the output drive, the short must be removed and the input toggled OFF and then ON. A short to the supply is the only error condition that requires an input toggle reset.

Bit 3 - indicates the condition of an output to ground short. As shown in the Functional Block Diagram, each output stage has drain-to-supply (VCC1) and drain-to-ground pullup and pull-down resistors of approximately  $10k\Omega$  to sense this condition. When the output is off and the sense level is low, an output-to-ground short is detected by the comparator. This condition is sensed when the output is pulled lower than 0.24xVCC (typical).

Bit 4 - indicates the condition of an open load on the output. The same divider noted for Bit 3 is used to set the output level. If the sense level is at or near the mid-range of the voltage supply,  $V_{CC}1$  when the output is in the off condition, a no-load condition is detected.

| TARIF 1 | SFRIAL | REGISTER | $D\Delta T\Delta$ | SEQUENCE |

|---------|--------|----------|-------------------|----------|

| CHANNEL NO. | BIT<br>NO. | FAULT FUNCTION   | FAULT<br>SYMBOL |

|-------------|------------|------------------|-----------------|

| Switch      | 1          | Over-Temperature | OT1             |

| Channel 1   | 2          | Short to Supply  | SB1             |

|             | 3          | Short to Ground  | SG1             |

|             | 4          | Open Load        | OI1             |

| Switch      | 5          | Over-Temperature | OT2             |

| Channel 2   | 6          | Short to Supply  | SB2             |

|             | 7          | Short to Ground  | SG2             |

|             | 8          | Open Load        | Ol2             |

| Switch      | 9          | Over-Temperature | OT3             |

| Channel 3   | 10         | Short to Supply  | SB3             |

|             | 11         | Short to Ground  | SG3             |

|             | 12         | Open Load        | OI3             |

| Switch      | 13         | Over-Temperature | OT4             |

| Channel 4   | 14         | Short to Supply  | SB4             |

|             | 15         | Short to Ground  | SG4             |

|             | 16         | Open Load        | Ol4             |

#### Serial Peripheral Interface Bus Control

Technically, the HIP0080 and HIP0081 fault data has only 16 bits. Except for the Error Flag, DF data bit shown in Figure 2, the format matches that of a normal CPOL = 0, CPHA = 1 SPI protocol (polarities, phase, etc). The DF bit from the DO output is active only until the clock starts. The best way to take advantage of it (if desired) is to connect the DO to the SPI bus, and also to a port pin, or other logic input. After CS goes low and before the SPI clocks starts, the DF bit can be read. If it is a zero, then the rest of the data does not have to be read. (The data will be all 0's = no errors). If the DF bit = 1, then the data must be read to find out which bit(s) is set.

Multiple ICs can be cascaded such that an error bit on any IC will daisy chain up to the last DO; this allows the microcontroller to "wire-OR" all of the devices automatically. Other than bidirectional data IC types, different IC types may be cascaded. The HIP0080 or HIP0081 should be closest to the microcontroller to use the DF bit feature. ICs that do not have an OR'ed means of passing fault bit would require all data be clocked to check the diagnostic bits.

# Clamp Energy Ratings for the HIP0080 and HIP0081

Figures 4 and 5 define the Single Pulse Energy ratings for the HIP0080 and HIP0081. Refer to Application Note AN9416 for further information on Single Pulse Energy ratings for inductive load operation and Dissipation capability for the 15 pin Power SIP Package. The Device Under Test conducts when the zener over voltage clamp turns on the output. While drain-to-source voltage, VDS and drain current, ID are monitored, the current drive pulse width,  $t_{\rm ON}$  in seconds is varied to determine the Single Pulse Energy capability. The energy in Joules is calculated from the following equation:

Single Pulse Energy = VDS x ID x  $t_{ON}$ .

Refer to Application Note 9416 for further information on Single Pulse Energy ratings for inductive load operation and Dissipation capability for the 15 pin Power SIP Package.

FIGURE 1. DIAGNOSTIC INTERFACE LOGIC

FIGURE 2. DATA AND CLOCK TIMING

FIGURE 3. CASCADED CHIP OPERATION TO READ DIAGNOSTIC DATA

FIGURE 4. SINGLE PULSE ENERGY TEST SHOWING THE FAILURE BOUNDARY FOR EACH HIP0080 OUTPUT STRESSED TO POINT OF FAILURE

## Dissipation In Multiple Outputs

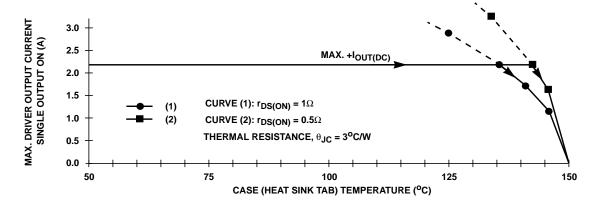

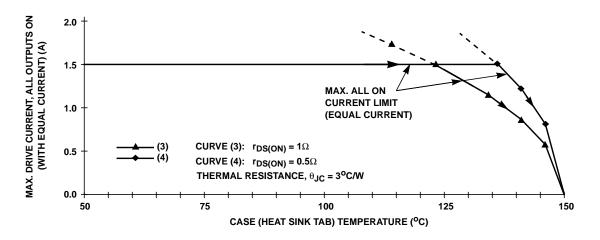

The HIP0080 and HIP0081 Power Drivers have multiple MOS Output Drivers and require special consideration with regard to maximum current and dissipation ratings. While each output has a maximum current specification consistent with the device structure, all such devices on the chip can not be simultaneously rated to the same high level of peak current. The total combined current and the dissipation on the chip must be adjusted for maximum allowable ratings, given simultaneous multiple output conditions.

For the HIP0081, the maximum positive output current rating is 2.2A when one output is ON. When ALL outputs are ON, the rating is reduced to 1.5A because the total maximum current is limited to 6A. For any given application, all output drivers on a chip may or may not have a different level of loading. The discussion here is intended to provide relatively simple methods to determine the maximum dissipation and current ratings as a general solution and, as a special solution, when all switched ON outputs have the same current loading.

#### General Solution

A general equation for dissipation should specify that the total power dissipation in a package is the sum of all significant elements of dissipation on the chip. However, in Power BiMOS Circuits very little dissipation is needed to control the logic and predriver circuits on the chip. The overall chip dissipation is primarily the sum of the  $I^2R$  dissipation losses in each channel where the current, I is the output current and the resistance, R is the NMOS channel resistance,  $r_{DS(ON)}$  of each output driver. As such, the total dissipation,  $P_D$  for n output drivers is:

$$=\sum_{k=1}^{n}P_{k}$$

(EQ. 1)

FIGURE 5. SINGLE PULSE ENERGY TEST SHOWING THE FAILURE BOUNDARY FOR EACH HIP0081 OUTPUT STRESSED TO POINT OF FAILURE

This expression sums the dissipation,  $P_k$  of each output driver without regard to uniformity of dissipation in each MOS channel. The dissipation loss in an NMOS channel is given in Equation 2 where the current, I, is determined by the output load when the channel is turned ON. The channel resistance,  $r_{DS(ON)}$  is a function of the circuit design, level of gate voltage and the chip temperature. Other switching losses may include  $I^2R$  lost in the interconnecting metal on the chip and bond wires of the package.

$$P_{k} = I^{2} \times r_{DS(ON)}$$

(EQ. 2)

The temperature rise in the package due to the dissipation is the product of the dissipation,  $P_D$  and the thermal resistance,  $\theta_{JC}$  of the package (Junction-to-Case). To determine the chip junction temperature,  $T_J$ , given the case (heat sink  $_{tab}$ ) temperature,  $T_C$ , the linear heat flow solution is:

$$T_{J} = T_{C} + P_{D} \times \theta_{JC}$$

(EQ. 3)

or:

$$T_{C} = T_{J} - P_{D} \times \theta_{JC}$$

(EQ. 3A)

Since this solution relates only to the package, further consideration must be given to a practical heat sink. The equation of linear heat flow assumes that the thermal resistance from Junction-to-Ambient ( $\theta_{JA}$ ) is the sum of the thermal resistance from Junction-to-Case and the thermal resistance from Case (heat sink)-to-Ambient. The Junction-to-Ambient thermal resistance,  $\theta_{JA}$  is the sum of all thermal paths from the chip junction to the ambient temperature ( $T_A$ ) environment and can be expressed as:

$$\theta_{JA} = \theta_{JC} + \theta_{CA}$$

(EQ. 4)

The Junction-to-Ambient equivalent to Equation 3, 3A is:

$$T_{J} = T_{A} + P_{D} \times \theta_{JA}$$

(EQ. 5)

or:

$$T_{A} = T_{J} - P_{D} \times \theta_{JA}$$

(EQ. 5A)

Not all Integrated Circuit packages have a directly definable case temperature because the heat is spread through the lead frame to a PC Board which is the effective heat sink.

#### Calculation Example 1

For the HIP0081,  $\theta_{JC} = 3^{o}$ C/W and the worst case junction temperature, as an application design solution, should not exceed 150°C. For a given application, Equation 1 determines the dissipation,  $P_{D}$ .

Assume the package is mounted to a heat sink having a thermal resistance of  $6^{\circ}\text{C/W}$  and, for a given application, assume the dissipation is 3W and the ambient temperature ( $T_A$ ) is  $100^{\circ}\text{C}$ . From Equation 4,  $\theta_{JA}$  is  $9^{\circ}\text{C/W}$ . The solution for junction temperature ( $T_C$ ) by Equation 3 is:

$$T_J = 100^{\circ}C + 3W \times 9^{\circ}C/W = 127^{\circ}C.$$

#### Calculation Example 2:

Assume for the HIP0080,  $\theta_{JA}=30^{o}\text{C/W}$  mounted on a PC Board with good heat sinking characteristics. Again, the worst case junction temperature, as an application design solution, should not exceed  $150^{o}\text{C}$ . Assume from the application, based on Equation 1, the dissipation,  $P_D=1.5\text{W}$ . The maximum junction temperature is known and can be used to determine the maximum allowable ambient temperature from Equation 5A as follows:

$$T_A = 150^{\circ}C - 1.5W \times 30^{\circ}C/W = 105^{\circ}C.$$

#### **Equal Current Loading Solution**

Many applications may have equal current loading in the output drivers with equal saturated turn ON and temperature conditions. As such, a convenient method to show rating boundaries is to substitute the dissipation Equation 2 into the junction temperature Equation 3. For m outputs that are ON and conducting with equal currents, where  $I=I_1=I_2.....=I_m$ , we have the following solution for dissipation:

$$P_{D} = m \times P_{k} = m \times I^{2} \times r_{DS(ON)}$$

(EQ. 6)

$$I = \sqrt{\frac{T_J - T_C}{m \times \theta_{JC} \times r_{DS(ON)}}}$$

(EQ. 7)

The number of output drivers ON and conducting (m) may be from 1 to n. (i.e., For all four output drivers of the HIP0081 ON, m=4.) Maximum temperature, dissipation and current ratings must be observed. For a defined number of conducting Power MOS Output Drivers, we can plot the results for m devices showing I vs  $T_C$ .

Given the HIP0081 as an example, Figures 6 and Figure 7 illustrate the boundaries for temperature and current. Figure 6 shows the maximum current for a single output ON while Figure 7 shows the maximum current for all four outputs ON with equal current plotted versus Case Temperature, T<sub>C</sub>. Boundary conditions relate to the Absolute Maximum Ratings as defined in the Data Sheet.

FIGURE 6. HIP0081 MAXIMUM SINGLE OUTPUT CURRENT vs CASE (TAB) TEMPERATURE

FIGURE 7. HIP0081 CURRENT vs CASE (TAB) TEMPERATURE, ALL OUTPUTS ON WITH EQUAL CURRENT

FIGURE 8. DISSIPATION DERATING CURVES

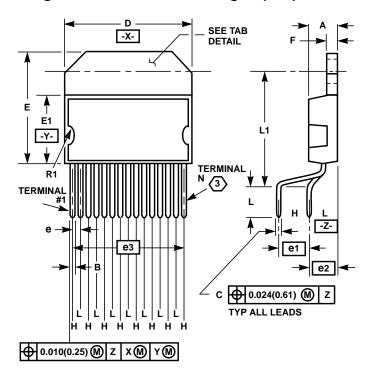

# Single-In-Line Plastic Packages (SIP)

#### NOTES:

- 1. Refer to series symbol list, JEDEC Publication No. 95.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1982.

- 3. N is the number of terminals.

- 4. Controlling dimension: INCH.

Z15.05A (JEDEC MO-048 AB ISSUE A)

15 LEAD PLASTIC SINGLE-IN-LINE PACKAGE STAGGERED

VERTICAL LEAD FORM

|                | INCHES MILLI |       |       | IETERS |

|----------------|--------------|-------|-------|--------|

| SYMBOL         | MIN          | MAX   | MIN   | MAX    |

| A              | 0.172        | 0.182 | 4.37  | 4.62   |

| В              | 0.024        | 0.031 | 0.61  | 0.79   |

| С              | 0.014        | 0.024 | 0.36  | 0.61   |

| D              | 0.778        | 0.798 | 19.76 | 20.27  |

| E              | 0.684        | 0.694 | 17.37 | 17.63  |

| E1             | 0.416        | 0.426 | 10.57 | 10.82  |

| E2             | 0.110        | BSC   | 2.79  | BSC    |

| е              | 0.050 BSC    |       | 1.27  | BSC    |

| e1             | 0.200 BSC    |       | 5.08  | BSC    |

| e2             | 0.169 BSC    |       | 4.29  | BSC    |

| e3             | 0.700 BSC    |       | 17.78 | BSC    |

| F              | 0.057        | 0.063 | 1.45  | 1.60   |

| L              | 0.150        | 0.176 | 3.81  | 4.47   |

| L <sub>1</sub> | 0.690        | 0.710 | 17.53 | 18.03  |

| N              | 1            | 5     | 1     | 5      |

| ØP             | 0.148        | 0.152 | 3.76  | 3.86   |

| R1             | 0.065        | 0.080 | 1.65  | 2.03   |

Rev. 1 4/98

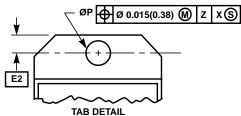

## Single-In-Line Plastic Packages (SIP)

# 000000000000000000

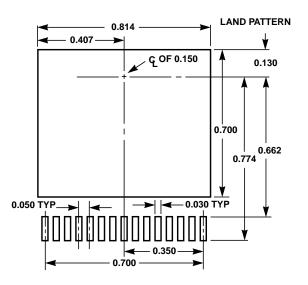

**Z15.05B**15 LEAD PLASTIC SINGLE-IN-LINE PACKAGE SURFACE MOUNT "GULLWING" LEAD FORM

|        | INC       | HES   | MILLIM   | IETERS |  |

|--------|-----------|-------|----------|--------|--|

| SYMBOL | MIN       | MAX   | MIN      | MAX    |  |

| Α      | 0.172     | 0.182 | 4.37     | 4.62   |  |

| В      | 0.024     | 0.031 | 0.61     | 0.79   |  |

| С      | 0.018     | 0.024 | 0.46     | 0.61   |  |

| D      | 0.778     | 0.798 | 19.76    | 20.27  |  |

| E      | 0.684     | 0.694 | 17.37    | 17.63  |  |

| E1     | 0.416     | 0.426 | 10.57    | 10.82  |  |

| E2     | 0.110     | BSC   | 2.79 BSC |        |  |

| е      | 0.050     | BSC   | 1.27     | BSC    |  |

| e3     | 0.700 BSC |       | 17.78    | BSC    |  |

| F      | 0.057     | 0.063 | 1.45     | 1.60   |  |

| L      | 0.065     | 0.080 | 1.66     | 2.03   |  |

| L1     | 0.098     | 0.108 | 2.49     | 2.74   |  |

| N      | 1         | 5     | 15       |        |  |

| ØP     | 0.148     | 0.152 | 3.76     | 3.86   |  |

| R1     | 0.065     | 0.080 | 1.65     | 2.03   |  |

Rev. 1 11/97

#### NOTES:

- 1. Dimensioning and Tolerancing per ANSI Y14.5M 1982.

- 2. N is the number of terminals.

- 3. All lead surfaces are within 0.004 inch of each other. No lead can be more than 0.004 inch above or below the header plane, ( -z- Datum).

- 4. Controlling dimension: INCH.

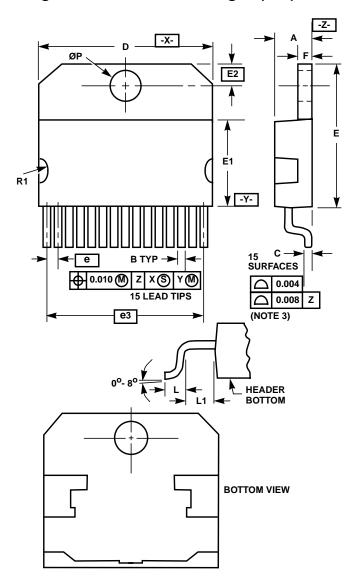

## Plastic Leaded Chip Carrier Packages (PLCC)

N28.45 (JEDEC MS-018AB ISSUE A)

28 LEAD PLASTIC LEADED CHIP CARRIER PACKAGE

|        | INCHES |       | MILLIN |       |       |

|--------|--------|-------|--------|-------|-------|

| SYMBOL | MIN    | MAX   | MIN    | MAX   | NOTES |

| Α      | 0.165  | 0.180 | 4.20   | 4.57  | -     |

| A1     | 0.090  | 0.120 | 2.29   | 3.04  | -     |

| D      | 0.485  | 0.495 | 12.32  | 12.57 | -     |

| D1     | 0.450  | 0.456 | 11.43  | 11.58 | 3     |

| D2     | 0.191  | 0.219 | 4.86   | 5.56  | 4, 5  |

| Е      | 0.485  | 0.495 | 12.32  | 12.57 | -     |

| E1     | 0.450  | 0.456 | 11.43  | 11.58 | 3     |

| E2     | 0.191  | 0.219 | 4.86   | 5.56  | 4, 5  |

| N      | 2      | 8     | 2      | 6     |       |

Rev. 2 11/97

#### NOTES:

- Controlling dimension: INCH. Converted millimeter dimensions are not necessarily exact.

- 2. Dimensions and tolerancing per ANSI Y14.5M-1982.

- 3. Dimensions D1 and E1 do not include mold protrusions. Allowable mold protrusion is 0.010 inch (0.25mm) per side. Dimensions D1 and E1 include mold mismatch and are measured at the extreme material condition at the body parting line.

- 4. To be measured at seating plane -C- contact point.

- 5. Centerline to be determined where center leads exit plastic body.

- 6. "N" is the number of terminal positions.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

## Sales Office Headquarters

**NORTH AMERICA**

Intersil Corporation P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902 TEL: (321) 724-7000 FAX: (321) 724-7240 EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium

TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

**ASIA**

Intersil Ltd. 8F-2, 96, Sec. 1, Chien-kuo North, Taipei, Taiwan 104

Republic of China TEL: 886-2-2515-8508 FAX: 886-2-2515-8369