## HIP1012, HIP1012A

#### Data Sheet

#### November 1999

## Dual Power Distribution Controller

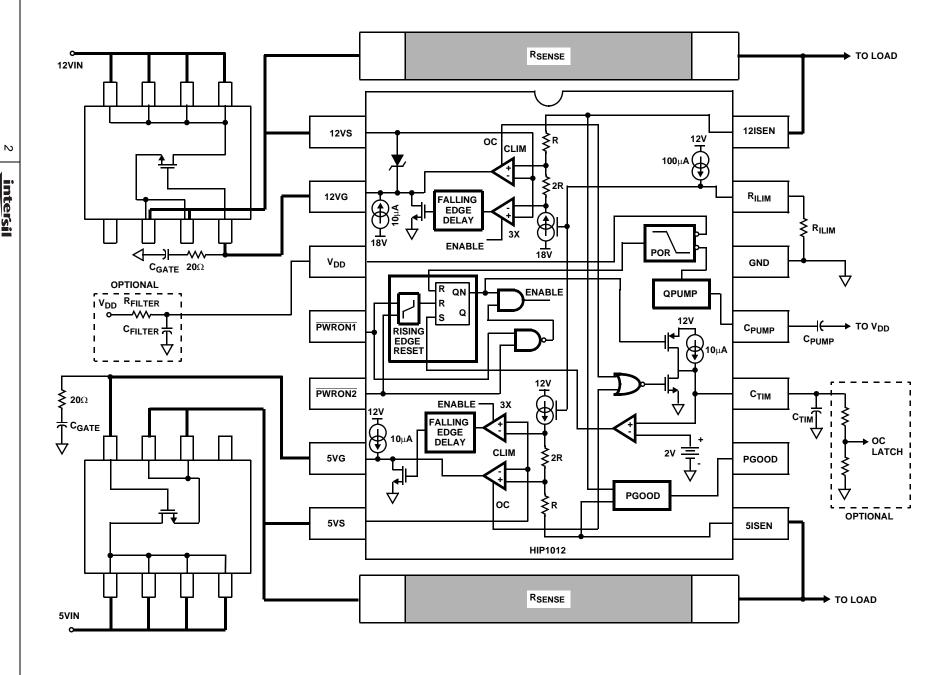

The HIP1012 is a HOT SWAP dual supply power distribution controller. Two external N-Channel MOSFETs are driven to distribute power while providing load fault isolation.

At turn-on, the gate of each external N-Channel MOSFET is charged with a 10µA current source. Capacitors on each gate (see the Typical Application Diagram), create a programmable ramp (soft turn-on) to control inrush currents. A built in charge pump supplies the gate drive for the 12V supply N-Channel MOSFET switch.

Over current protection is facilitated by two external current sense resistors. When the current through either resistor exceeds the user programmed value the controller enters the current regulation mode. The time-out capacitor, CTIM, starts charging as the controller enters the time out period. Once C<sub>TIM</sub> charges to a 2V threshold, the N-Channel MOSFETs are latched off. In the event of a fault at least three times the current limit level, the N-Channel MOSFET gates are pulled low immediately before entering time out period. The controller is reset by a rising edge on either PWRON pin.

Choosing the voltage selection mode the HIP1012 controls either +12V/5V or +3.3V/+5V supplies.

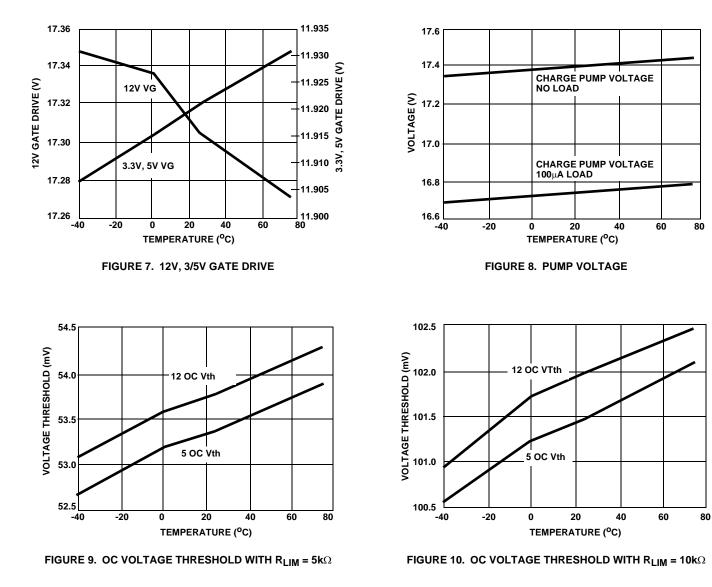

For those applications where voltage tolerance is a concern the HIP1012A has a minimum nominal over current threshold voltage of 50mV as compared to 100mV for the HIP1012.

## Ordering Information

| PART NUMBER                 | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE                     | PKG.<br>NO. |

|-----------------------------|----------------------------------|-----------------------------|-------------|

| HIP1012CB<br>HIP1012ACB     | -0 to 70                         | 14 Ld SOIC                  | M14.15      |

| HIP1012CB-T<br>HIP1012ACB-T | -0 to 70                         | 14 Ld SOIC<br>Tape and Reel | M14.15      |

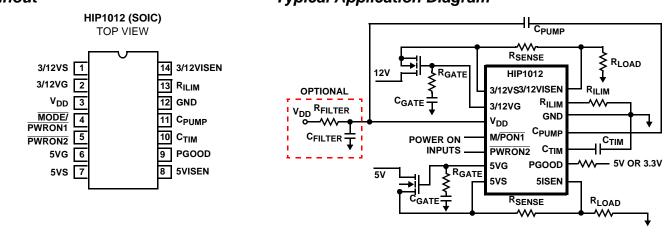

## Pinout

## Features

- HOT SWAP Dual Power Distribution Control for +5V and +12V or +5V and +3.3V

- **Provides Fault Isolation**

- Programmable Current Regulation Level

- Programmable Time Out •

- Charge Pump Allows the Use of N-Channel MOSFETs

- Power Good and Over Current Latch Indicators

- Enhanced Over Current Sensitivity Available

- Redundant Power On Controls

- Adjustable Turn-On Ramp

- Protection During Turn-On

- Two Levels of Current Limit Detection Provide Fast Response to Varying Fault Conditions

- Less Than 1µs Response Time to Dead Short

- 3µs Response Time to 200% Current Overshoot

## Applications

- Redundant Array of Independent Disks (RAID) System

- Power Distribution Control

- Hot Plug<sup>™</sup>, Hot Swap Components

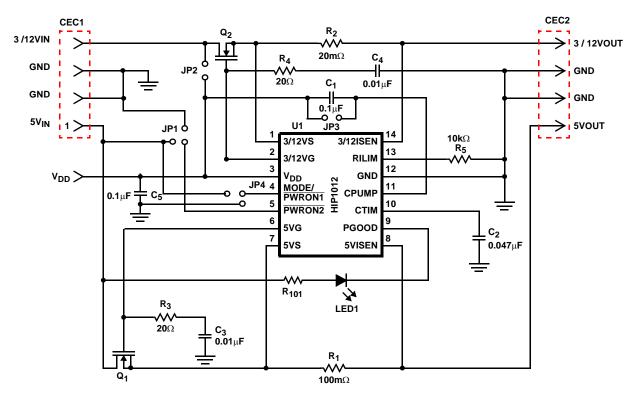

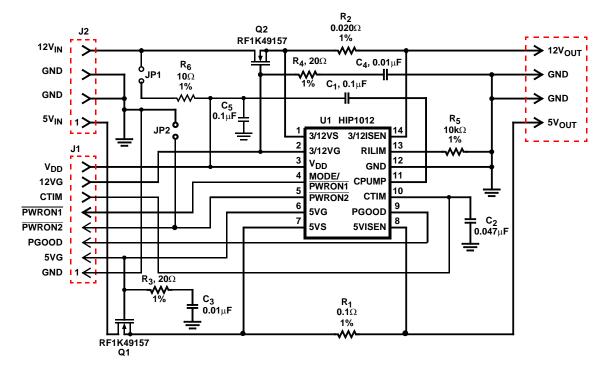

## Typical Application Diagram

1

**Simplified Schematic**

intersil

HIP1012, HIP1012A

## Pin Descriptions

| PIN # | SYMBOL            | FUNCTION                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------|-------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1     | 3V/12VS           | 3.3 V/12V Source                                                         | Connect to source of associated external N-Channel MOSFET switch to sense output voltage.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

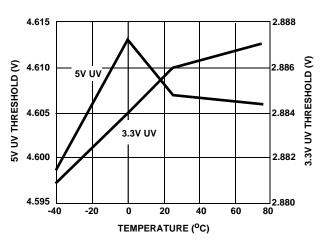

| 2     | 3V/12VG           | 3.3V/12V Gate                                                            | Connect to the gate of associated N-Channel MOSFET switch. A capacitor from this node to ground sets the turn-on ramp. At turn-on this capacitor will be charged to 17.4V by a $10\mu$ A current source when in 5v/12V mode of operation, otherwise capacitor will be charged to 11.4V. A small resistor (10 - $200\Omega$ ) should be placed in series with the gate capacitor to ground to prevent current oscillations.                                                                     |  |  |  |

| 3     | V <sub>DD</sub>   | Chip Supply                                                              | Connect to 12V supply. This can be either connected directly to the +12V rail supplying load voltage or to a dedicated $V_{DD}$ +12V supply. If the former is chosen special attention $V_{DD}$ decoupling must be paid.                                                                                                                                                                                                                                                                       |  |  |  |

| 4     | MODE/<br>PWRON1   | Power ON/ Reset Invokes 3.3V operation when shorted to $V_{DD}$ , pin 3. | WRON1 and PWRON2 are used to turn-on and reset the chip. Both outputs turn-on whether pin is driven low. After a current limit time out, the chip is reset by the rising edge cleaset signal applied to either PWRON pin. Each input has 100µA pull up capability which                                                                                                                                                                                                                        |  |  |  |

| 5     | PWRON2            | Power ON/ Reset                                                          | compatible with 3V and 5V open drain and standard logic. PWRON1 is also used to in 3.3V control operation in preference to +12V control. By tying pin 4 to pin 3 the charge is disabled and the UV threshold also shifts to 2.8V.                                                                                                                                                                                                                                                              |  |  |  |

| 6     | 5VG               | 5V Gate                                                                  | Connect to the gate of the external 5V N-Channel MOSFET. A capacitor from this node to ground sets the turn-on ramp. At turn-on this capacitor will be charged to 11.4V by a $10\mu$ A current source. A small resistor (10 - $200\Omega$ ) should be placed in series with the gate capacitor to ground to prevent current oscillations.                                                                                                                                                      |  |  |  |

| 7     | 5VS               | 5V Source                                                                | Connect to the source side of 5V external N-Channel MOSFET switch to sense output voltage.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 8     | 5VISEN            | 5V Current Sense                                                         | Connect to the load side of the 5V sense resistor to measure the voltage drop across this resistor between 5VS and 5VISEN pins.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 9     | PGOOD             | Power Good indicator                                                     | Indicates that all output voltages are within specification. PGOOD is driven by an open drain N-Channel MOSFET. It is pulled low when any output is not within specification.                                                                                                                                                                                                                                                                                                                  |  |  |  |

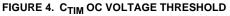

| 10    | C <sub>TIM</sub>  | Current Limit Timing<br>Capacitor                                        | Connect a capacitor from this pin to ground. This capacitor controls the time between the onset of current limit and chip shutdown (current limit time-out). The duration of current limit time-out (in seconds) = $200k\Omega \times C_{TIM}$ (Farads).                                                                                                                                                                                                                                       |  |  |  |

| 11    | C <sub>PUMP</sub> | Charge Pump<br>Capacitor                                                 | Connect a 0.1 $\mu$ F capacitor between this pin and V_DD (pin3). Directly connect this pin to V_DD when in 3.3V control mode.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 12    | GND               | Chip Ground                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

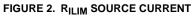

| 13    | R <sub>ILIM</sub> | Current Limit Set<br>Resistor                                            | A resistor connected between this pin and ground determines the current level at which current limit is activated. This current is determined by the ratio of the R <sub>ILIM</sub> resistor to the sense resistor (R <sub>SENSE</sub> ). The current at current limit onset is equal to 10µA x (R <sub>ILIM</sub> / R <sub>SENSE</sub> ). The HIP1012 is limited to a 10kΩ min value (OC Vth = 100mV) resistor whereas the HIP1012A can accommodate a 5kΩ resistor for a lower OC Vth (50mV). |  |  |  |

| 14    | 3V/12VISEN        | 3.3V/12V Current Sense                                                   | Connect to the load side of sense resistor to measure the voltage drop across this resistor.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|       |                   |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

#### **Absolute Maximum Ratings** T<sub>A</sub> = 25°C

| V <sub>DD</sub>                                                           |

|---------------------------------------------------------------------------|

| 3/12VG, C <sub>PUMP</sub>                                                 |

| 3/12VISEN, 3/12VS                                                         |

| 5VISEN, 5VS                                                               |

| PGOOD, R <sub>ILIM</sub> 0.3V to 7.5V                                     |

| MODE/PWRON1, PWRON2, C <sub>TIM</sub> , 5VG0.3V to V <sub>DD</sub> + 0.3V |

| ESD Classification                                                        |

#### **Operating Conditions**

| V <sub>DD</sub> Supply Voltage Range | +10.5V to +13.2                       |

|--------------------------------------|---------------------------------------|

| Temperature Range (T <sub>A</sub> )  | 0 <sup>o</sup> C to 70 <sup>o</sup> C |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)           | θ <sub>JA</sub> ( <sup>o</sup> C/W)  |

|------------------------------------------------|--------------------------------------|

| SOIC Package                                   | 120                                  |

| Maximum Junction Temperature (Plastic Package) | 150 <sup>0</sup> C                   |

| Maximum Storage Temperature Range65            | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s)       | 300 <sup>0</sup> C                   |

| (SOIC - Lead Tips Only)                        |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

2. All voltages are relative to GND, unless otherwise specified.

## **Electrical Specifications** $V_{DD} = 12V, C_{VG} = 0.01\mu F, C_{TIM} = 0.1\mu F, R_{SENSE} = 0.1\Omega, C_{BULK} = 220\mu F, ESR = 0.5\Omega, T_A = T_J = 0^{\circ}C$ to 70°C, Unless Otherwise Specified

| PARAMETER                                                                   | SYMBOL                                       | TEST CONDITIONS                                                                                                      | MIN        | ТҮР        | MAX        | UNITS    |

|-----------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------|------------|------------|----------|

| 12V CONTROL SECTION                                                         |                                              | •                                                                                                                    |            |            | •          | •        |

| Current Limit Threshold Voltage<br>(Voltage Across Sense Resistor)          | V <sub>IL12V</sub><br>V <sub>IL12V</sub>     | $ \begin{array}{l} R_{ILIM} = 10 \mathrm{k}\Omega \\ R_{ILIM} = 5 \mathrm{k}\Omega \; HIP1012A \; only \end{array} $ | 92<br>47   | 100<br>53  | 108<br>59  | mV<br>mV |

| 3X Current Limit Threshold Voltage<br>(Voltage Across Sense Resistor)       | 3XV <sub>iL12V</sub><br>3XV <sub>IL12V</sub> | $R_{ILIM} = 10 k\Omega$<br>$R_{ILIM} = 5 k\Omega$ HIP1012A only                                                      | 250<br>100 | 300<br>165 | 350<br>210 | mV<br>mV |

| ±20% Current Limit Response Time<br>(Current within 20% of Regulated Value) | 20%iLrt                                      | 200% Current Overload, $R_{ILIM} = 10k\Omega$ , $R_{SHORT} = 6.0\Omega$                                              | -          | 2          | -          | μs       |

| ±10% Current Limit Response Time<br>(Current within 10% of Regulated Value) | 10%iLrt                                      | 200% Current Overload, $R_{ILIM} = 10k\Omega$ , $R_{SHORT} = 6.0\Omega$                                              | -          | 4          | -          | μs       |

| ±1% Current Limit Response Time<br>(Current within 1% of Regulated Value)   | 1%iLrt                                       | 200% Current Overload, $R_{ILIM} = 10k\Omega$ , $R_{SHORT} = 6.0\Omega$                                              | -          | 10         | -          | μs       |

| Response Time To Dead Short                                                 | RT <sub>SHORT</sub>                          | $C_{12VG} = 0.01 \mu F$                                                                                              | -          | 500        | 1000       | ns       |

| Gate Turn-On Time                                                           | t <sub>ON12V</sub>                           | $C_{12VG} = 0.01 \mu F$                                                                                              | -          | 12         | -          | ms       |

| Gate Turn-On Current                                                        | I <sub>ON12V</sub>                           | $C_{12VG} = 0.01 \mu F$                                                                                              | 8          | 10         | 12         | μΑ       |

| 3X Gate Discharge Current                                                   | 3Xdisl                                       | 12VG = 18V                                                                                                           | 0.5        | 0.75       | -          | A        |

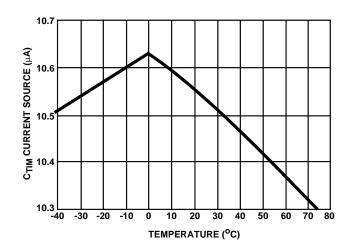

| 12V Under Voltage Threshold                                                 | 12V <sub>VUV</sub>                           |                                                                                                                      | 10.5       | 10.8       | 11.0       | V        |

| Qpumped 12VG Voltage                                                        | V12VG                                        | $C_{PUMP} = 0.1 \mu F$                                                                                               | 16.8       | 17.3       | 17.9       | V        |

| 3.3V/5V CONTROL SECTION                                                     | •                                            | •                                                                                                                    | •          | •          | •          |          |

| Current Limit Threshold Voltage<br>(Voltage Across Sense Resistor)          | V <sub>IL5V</sub>                            | $R_{ILIM} = 10 k\Omega$<br>$R_{ILIM} = 5 k\Omega$ HIP1012A only                                                      | 92<br>47   | 100<br>53  | 108<br>59  | mV<br>mV |

| 3X Current Limit Threshold Voltage<br>(Voltage Across Sense Resistor)       | 3XV <sub>IL5V</sub>                          | $R_{ILIM} = 10 k\Omega$<br>$R_{ILIM} = 5 k\Omega$ HIP1012A only                                                      | 250<br>100 | 300<br>155 | 350<br>210 | mV<br>mV |

| ±20% Current Limit Response Time<br>(Current within 20% of regulated value) |                                              | 200% Current Overload, $R_{ILIM} = 10k\Omega$ , $R_{SHORT} = 2.5\Omega$                                              | -          | 2          | -          | μs       |

| ±10% Current Limit Response Time<br>(Current within 10% of Regulated Value) |                                              | 200% Current Overload, $R_{ILIM} = 10k\Omega$ , $R_{SHORT} = 2.5\Omega$                                              | -          | 4          | -          | μs       |

| ±1% Current Limit Response Time<br>(Current within 1% of Regulated Value)   |                                              | 200% Current Overload, $R_{ILIM} = 10k\Omega$ , $R_{SHORT} = 2.5\Omega$                                              | -          | 10         | -          | μs       |

| Response Time To Dead Short                                                 | RT <sub>SHORT</sub>                          | C <sub>VG</sub> = 0.01µF                                                                                             | -          | 500        | 800        | ns       |

## **Electrical Specifications** $V_{DD} = 12V, C_{VG} = 0.01\mu$ F, $C_{TIM} = 0.1\mu$ F, $R_{SENSE} = 0.1\Omega, C_{BULK} = 220\mu$ F, ESR = $0.5\Omega, T_A = T_J = 0^{\circ}$ C to 70°C, Unless Otherwise Specified **(Continued)**

| PARAMETER                                            | SYMBOL                 | TEST CONDITIONS                                    | MIN  | ТҮР  | МАХ  | UNITS |

|------------------------------------------------------|------------------------|----------------------------------------------------|------|------|------|-------|

| Gate Turn-On Time                                    | t <sub>ON5V</sub>      | C <sub>VG</sub> = 0.01μF                           | -    | 5    | -    | ms    |

| Gate Turn-On Current                                 | I <sub>ON5V</sub>      | C <sub>VG</sub> = 0.01μF                           | 8    | 10   | 12   | μA    |

| 3X Gate Discharge Current                            | 3Xdisl                 | $C_{VG} = 0.01 \mu F$ , PWRON = Low                | 0.5  | 0.75 | -    | Α     |

| 5V Under Voltage Threshold                           | 5V <sub>VUV</sub>      |                                                    | 4.35 | 4.5  | 4.65 | V     |

| 3.3V Under Voltage Threshold                         | 3.3V <sub>VUV</sub>    |                                                    | 2.65 | 2.8  | 2.95 | V     |

| 3.3/5VG High Voltage                                 | 3/5VG                  |                                                    | 11.2 | 11.9 | -    | V     |

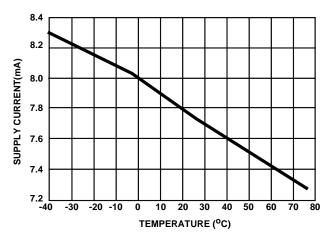

| SUPPLY CURRENT AND IO SPECIFICAT                     | TIONS                  |                                                    | ľ    | •    | •    | •     |

| V <sub>DD</sub> Supply Current                       | I <sub>VDD</sub>       |                                                    | 4    | 8    | 10   | mA    |

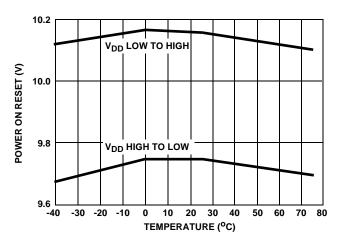

| V <sub>DD</sub> POR Rising Threshold                 |                        |                                                    | 9.5  | 10.0 | 10.7 | V     |

| V <sub>DD</sub> POR Falling Threshold                |                        |                                                    | 9.3  | 9.8  | 10.3 | V     |

| Current Limit Time-Out                               | T <sub>ILIM</sub>      | C <sub>TIM</sub> = 0.1μF                           | 16   | 20   | 24   | ms    |

| PWRON Pull-up Voltage                                | PWRN_V                 | PWRON pin open                                     | 1.8  | 2.4  | 3.2  | V     |

| PWRON Rising Threshold                               | PWR_Vth                |                                                    | 1.1  | 1.5  | 2    | V     |

| PWRON Hysteresis                                     | PWR_hys                |                                                    | 0.1  | 0.2  | 0.3  | V     |

| PWRON Pull-Up Current                                | PWRN_I                 |                                                    | 60   | 80   | 100  | μA    |

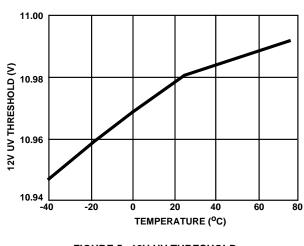

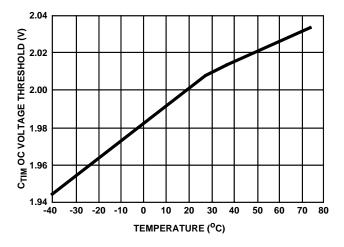

| Current Limit Time-Out Threshold (C <sub>TIM</sub> ) | C <sub>TIM</sub> _Vth  |                                                    | 1.8  | 2    | 2.2  | V     |

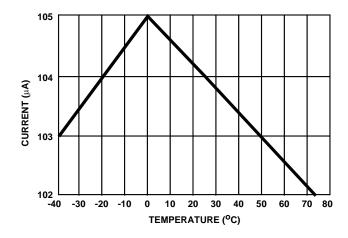

| C <sub>TIM</sub> Charging Current                    | C <sub>TIM</sub> _I    |                                                    | 8    | 10   | 12   | μA    |

| C <sub>TIM</sub> Discharge Current                   | C <sub>TIM</sub> _disl |                                                    | 1.7  | 2.6  | 3.5  | mA    |

| C <sub>TIM</sub> Pull-Up Current                     | C <sub>TIM</sub> _disI | V <sub>CTIM</sub> = 8V                             | 3.5  | 5    | 6.5  | mA    |

| R <sub>ILIM</sub> Pin Current Source Output          | R <sub>ILIM</sub> lo   |                                                    | 90   | 100  | 110  | μA    |

| Charge Pump Output Current                           | Qpmp_lo                | C <sub>PUMP</sub> = 0.1μF, C <sub>PUMP</sub> = 16V | 320  | 560  | 800  | μA    |

| Charge Pump Output Voltage                           | Qpmp_Vo                | No load                                            | 17.2 | 17.4 | -    | V     |

| Charge Pump Output Voltage - Loaded                  | Qpmp_Vlo               | Load current = 100µA                               | 16.2 | 16.7 | -    | V     |

| Charge Pump POR Rising Threshold                     | Qpmp+Vth               |                                                    | 15.6 | 16   | 16.5 | V     |

| Charge Pump POR Falling Threshold                    | Qpmp-Vth               |                                                    | 15.2 | 15.7 | 16.2 | V     |

### HIP1012 Description and Operation

The HIP1012 is a multi featured dual power supply distribution controller, including programmable current limiting regulation and time to latch off. Additionally the HIP1012 operates both as a +3.3V and 5V or a +5V and +12V power supply controller with each mode having appropriate Under Voltage (UV) fault notification levels.

Upon initial power up HIP1012 can either isolate the voltage supply from the load by holding the external N-Channel MOSFET switches off or apply the supply rail voltage directly to the load for true hot swap capability. In either case the HIP1012 turns on in a soft start mode protecting the supply rail from sudden current loading. If either  $\overline{PWRON}$  pin is pulled low the HIP1012 will be in true hot swap mode. Both  $\overline{PWRON}$  pins must be high to turn off the HIP1012 thus isolating the power supply from the load through the external FETs.

At turn-on, the gate capacitor of each external N-Channel MOSFET is charged with a  $10\mu$ A current source. These capacitors create a programmable ramp (soft turn-on). A charge pump supplies the gate drive for the 12V supply switch driving that gate to 17V.

The load currents pass through two external current sense resistors. When the voltage across either resistor exceeds the user programmed Over Current (OC) voltage threshold value, (see Table 1) the controller enters current regulation. At this time the time-out capacitor,  $C_{TIM}$ , starts charging with a 10µA current source and the controller enters the time out period. The length of the time out period is set by the single external capacitor (see Table 2) placed from the  $C_{TIM}$  pin (pin 10) to ground and is characterized by a lowered gate drive voltage to the appropriate external N-Channel MOSFET. Once  $C_{TIM}$  charges to 2V, an internal comparator is tripped resulting in both N-Channel MOSFETs being latched off.

| RILIM RESISTOR | NOMINAL OC VTH |  |  |  |  |

|----------------|----------------|--|--|--|--|

| 15kΩ           | 150mV          |  |  |  |  |

| 10kΩ           | 100mV          |  |  |  |  |

| 7.5kΩ          | 75mV           |  |  |  |  |

| 4.99kΩ         | 50mV           |  |  |  |  |

TABLE 1.

NOTE: Nominal OC Vth = Rilim x  $10\mu$ A.

| ТΔ | BI | F | 2        |

|----|----|---|----------|

|    |    | - | <u> </u> |

| C <sub>TIM</sub> CAPACITOR | NOMINAL TIME OUT PERIOD |

|----------------------------|-------------------------|

| 0.022µF                    | 4.4ms                   |

| 0.047µF                    | 9.4ms                   |

| 0.1µF                      | 20ms                    |

NOTE: Nominal time-out period in seconds =  $C_{TIM} \times 200 k\Omega$ .

The HIP1012 responds to a load short (defined as a current level 3X the OC set point) immediately, driving the relevant N-Channel MOSFET gate to 0V in less than 1 $\mu$ s. The gate voltage is then slowly ramped up turning on the N-Channel MOSFET to the programmed current limit level, this is the start of the time out period. The programmed current level is held until either the OC event passes or the time out period expires. If the former is the case then the N-Channel MOSFET is fully enhanced and the C<sub>TIM</sub> charging current is diverted away from the capacitor. If the time out period expires prior to OC resolution then both gates are quickly pulled to 0V turning off both N-Channel MOSFETs simultaneously.

Upon any OC or UV condition the PGOOD signal will pull low when tied high through a resistor to the logic supply. This pin is a fault indicator but not the OC latch off indicator. For an OC latch off indication, monitor CTIM, pin 10. This pin will rise rapidly to 12V once the time out period expires. See block diagram for OC latch off circuit suggestion.

The HIP1012 is reset by a rising edge on either  $\overline{PWRON}$  pin and is turned on by either  $\overline{PWRON}$  pin being driven low. The HIP1012 can control either +12V/5V or +3.3V/+5V supplies. Tying the  $\overline{PWRON1}$  pin to  $V_{DD}$ , invokes the +3.3V/+5V voltage mode. In this mode, the external charge pump capacitor is not needed and Cpump, pin 11 is also tied directly to  $V_{DD}$ .

## HIP1012 Application Considerations

For Applications where voltage tolerances are of critical concern the HIP1012A is better suited as it has a minimum nominal OC Vth performance of 50mV verses 100mV with the HIP1012 over the entire temperature range. This allows the use of lower Rsense value resistors resulting in higher efficiency.

#### When using the HIP1012 in the 12V and 5V mode

additional V<sub>DD</sub> decoupling may be necessary to prevent a power on reset due to a sag on V<sub>DD</sub> pin upon an OC latch off. The addition of a capacitor from V<sub>DD</sub> to GND may often be adequate but a small value isolation resistor may also be necessary. See the Simplified Schematic.

**Current loop stabilization** is facilitated through a small value resistor in series with the gate timing capacitor. As the HIP1012 drives a highly inductive current load, instability characterized by the gate voltage repeatedly ramping up and down may appear. A simple method to enhance stability is provided by the substitution of a larger value gate resistor. Typically this situation can be avoided by eliminating long point to point wiring to the load.

**Random resets** may occur if the HIP1012 sense pins are pulled below ground when turning off a highly inductive load. Place a large load capacitor  $(10-50\mu F)$  on the output to eliminate the unintended resets.

During the **Time Out delay period** with the HIP1012 in current limit mode, the V<sub>GS</sub> of the external N-Channel MOSFETs is reduced driving the N-Channel MOSFET switch into a high  $r_{DS(ON)}$  state. Thus avoid extended time out periods as the external N-Channel MOSFETs may be damaged or destroyed due to excessive internal power dissipation. Refer to the MOSFET manufacturers data sheet for SOA information.

With the high levels of inrush current e.g., highly capacitive loads and motor start up currents, **choosing the current limiting level** is crucial to provide both protection and still allow for this inrush current without latching off. Consider this in addition to the time out delay when choosing MOSFETs for your design.

**Physical layout of Rsense resistors** is critical to avoid the possibility of false over current occurrences. Ideally trace routing between the Rsense resistors and the HIP1012 is direct and as short as possible with zero current in the sense lines. Refer to the demo boards for examples.

**External Pull Down resistors**  $(5k\Omega)$  from the xISEN pins to ground will prevent the outputs from floating when the external switch FETs are disabled and the outputs are open.

#### **Typical Performance Curves**

FIGURE 3. C<sub>TIM</sub> CURRENT SOURCE

FIGURE 5. 12V UV THRESHOLD

7

#### FIGURE 6. 5V/3.3V UV THRESHOLD

### Typical Performance Curves (Continued)

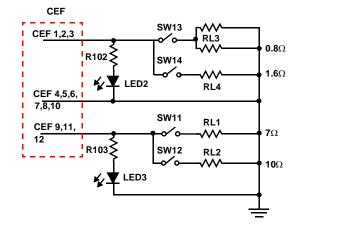

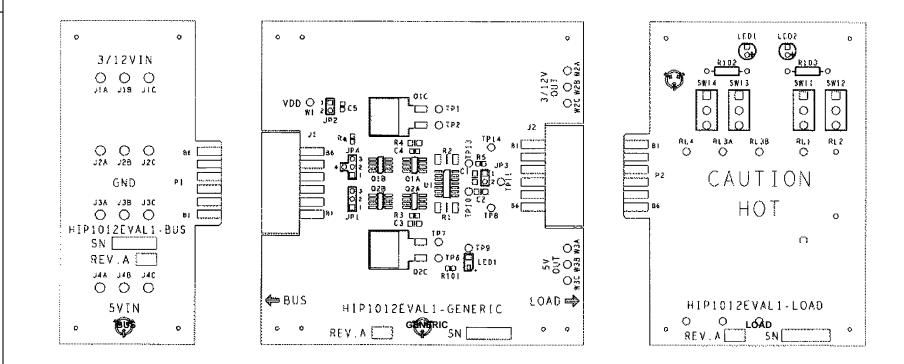

#### Exploring and Using the HIP1012EVAL1 Board (Figure 13)

The HIP1012EVAL1 is a flexible platform for a thorough evaluation of the HIP1012 dual power supply controller. This eval board comes in three separate parts allowing the evaluation of two principal configurations. To simulate a passive back plane implementation both the GENERIC and LOAD sections are first connected together and then the GENERIC board is connected onto the BUS board. For an active backplane or for the HIP1012 on an interposer board configuration, the BUS and GENERIC sections are first connected together and then the load board is connected onto the GENERIC board.

The HIP1012EVAL1 board has many built in features besides the configuration flexibility described above.

The BUS board is designed so that adding suitable connectors and/or power supply capacitive filtering is very easy to do through the numerous through holes for each rail voltage and ground. Passive backplane power sequencing can be simulated by simply shortening the finger lengths for the rail(s) that need to come up after initial ground connection is made.

The GENERIC board, is a flexible evaluation platform with many designed in features for user customizing and evaluation. The circuit is shipped default configured in the 3.3V and 5V controller mode by jumpers for easy reconfiguration (see Table 3 for jumper settings). The default configuration is highlighted in Table 3. The default OC levels are 5A on the 3.3V and 1A on the 5V supplies. To operate the HIP1012 GENERIC board in its default configuration (3V and 5V) a dedicated +12V power supply must be provided for the HIP1012 through tie point, W1 on the generic board. To operate the board in the +12V and 5V mode, JP2 and JP3 need to be reconfigured (see Table 3) and a suitable current load needs to be provided. A programmable electronic current load is an excellent evaluation tool for this device. The load board is configured to sink about 3±1A at 3.3V. For 12V operation, the load must be modified to sink less than 5A, otherwise, an OC failure upon power will occur. The GENERIC board is provided with a single pair of RF1K49156 N-Channel MOSFETs, if currents > 6A are to be evaluated then an additional pair of RF1K49156 MOSFETs can be installed in the provided space. Additionally for even higher current evaluations space for TO-252AA, DPAK or D<sup>2</sup>PAK devices has been provided. Contact Intersil Semiconductor for availability of Power MOSFET samples. Tie points on the output side of the GENERIC board are provided for direct access to a high current load. Performance customizing can easily be accomplished by substitution/addition of several SMD components to the existing layout or by utilizing the included bread board area. See Table 5 for the component listing and applicable formulae.

The LOAD board, consists of four load switches, output resistive and capacitive loads and output on indicating LED's. The resistive loads are configured so that either no current, a low or high current load relative to the OC trip point can be invoked for both supplies. An OC event can be emulated by switching both switches of any one output to the on position (see Table 4, OC conditions highlighted). Load connection sequencing can be done by shorting the desired finger lengths. As noted, the GENERIC board is default configured for 3V and 5V operation. For 12V evaluation replace RL3 and RL4 with a suitable load.

| JP # | OPEN /<br>SHORT                 | CIRCUIT CONDITION                                                                                                                                                         |

|------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Short to GND<br>2-3             | PWRON2 shorted to ground. True HOT   SWAP mode. PWRON1 only controls reset   with rising edge. PWRON1                                                                     |

| 1    | Short to 5V<br>1-2              | PWRON2 shorted to 5V. Reset and turn on controlled only by PWRON1. Single input control mode                                                                              |

| 1    | Open                            | PWRON2 will be internally pulled high to ~2.5V, compatible with logic signal. The HIP1012 can not turn on until PWRON2 is driven low.                                     |

| 2    | Open                            | HIP1012 must be powered from a dedicated +12V power supply.                                                                                                               |

| 2    | Short                           | HIP1012 V <sub>DD</sub> pin connected to same 12V<br>supply as load. See Decoupling Concerns in<br>Critical Items section.                                                |

| 3    | Open                            | C1 in circuit. Charge pump capacitor<br>necessary for 5V and 12V operating mode to<br>develop ~ 11.7V for 12VG voltage.                                                   |

| 3    | Short                           | Shorts across charge pump capacitor, C1.<br>Capacitor not needed in 3V and 5V mode.                                                                                       |

| 4    | Short to GND<br>1-2             | HIP1012 MODE/PWRON1 shorted to<br>ground. True HOT SWAP mode. PWRON2<br>rising edge only resets HIP1012.                                                                  |

| 4    | Short to 5V<br>2-4              | MODE/PWRON1 shorted to 5V. PWRON2 only single mode control.                                                                                                               |

| 4    | Short to V <sub>DD</sub><br>2-3 | HIP1012 MODE/PWRON1 connected to<br>V <sub>DD</sub> pin. This along with JP3 installed<br>invokes and configures HIP1012 for 3V<br>and 5V operation. Controlled by PWRON2 |

| 4    | Open                            | HIP1012 MODE/PWRON1 will be internally<br>pulled high to ~2.5V, compatible with logic.<br>Redundant controller mode when each<br>PWRON pin is driven by separate signals. |

#### TABLE 3. JUMPER CONFIGURATION

#### TABLE 4. LOAD CURRENT

| SW13 | SW14 | 3.3V I <sub>OUT</sub><br>A | SW11 | SW12 | 5.0V I <sub>OUT</sub><br>A |

|------|------|----------------------------|------|------|----------------------------|

| 0    | 0    | 0                          | 0    | 0    | 0                          |

| 0    | 1    | 2                          | 0    | 1    | 0.5                        |

| 1    | 0    | 4                          | 1    | 0    | 0.74                       |

| 1    | 1    | 6                          | 1    | 1    | 1.24                       |

### HIP1012EVAL1 Board Components

NOTE: Test point number equals HIP1012 pin number.

**GENERIC BOARD**

LOAD BOARD

FIGURE 13. HIP1012EVAL1 EVAL BOARD

#### TABLE 5. HIP1012EVAL1 BOARD COMPONENT LISTING

| COMPONENT<br>DESIGNATOR         | COMPONENT NAME                                                                                                             | COMPONENT DESCRIPTION                                                                                                                                                                                |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GENERIC BOARD                   | •                                                                                                                          | •                                                                                                                                                                                                    |  |  |

| U1                              | HIP1012CB                                                                                                                  | Intersil Corporation, HIP1012CB Dual Power Controller                                                                                                                                                |  |  |

| Q1, Q2                          | RF1K49156                                                                                                                  | Intersil Corporation, 30V, 30m $\Omega$ , 6.3A Logic Level N-Channel MOSFET                                                                                                                          |  |  |

| QxB and QxC                     | NOT PROVIDED                                                                                                               | Mounting areas for additional 8 SOIC, DPAK or D <sup>2</sup> PAK packaged MOSFETs                                                                                                                    |  |  |

| R <sub>1</sub>                  | 5V Sense Resistor                                                                                                          | 100m $\Omega$ , 1%, Metal Strip current sensing resistor                                                                                                                                             |  |  |

| R <sub>2</sub>                  | 3.3V/12V Sense Resistor                                                                                                    | 20mΩ, 1%, Metal Strip current sensing resistor                                                                                                                                                       |  |  |

| R <sub>3</sub> , R <sub>4</sub> | Loop compensation Resistors                                                                                                | $20\Omega$ , Resistor in series with gate capacitor. This RC may be necessary to provide current loop stability. Keep resistor < $50\Omega$ .                                                        |  |  |

| R <sub>5</sub>                  | Current Limit Set Resistor                                                                                                 | 10kΩ, Current limit = ~10µA x ( $R_{ILIM}/R_{SENSE}$ ).                                                                                                                                              |  |  |

| R*                              | Isolation resistor (not provided, see Decoupling<br>Concerns in Critical Items section)                                    | Add resistor (<50 $\Omega$ ) to isolate V <sub>DD</sub> from load transients if necessary to eliminate random V <sub>DD</sub> low reset. Cut short to install.                                       |  |  |

| C <sub>3</sub> , C <sub>4</sub> | Gate Timing Capacitors                                                                                                     | $0.01 \mu F, 10 \mu A$ charging I source provides slow ramp on of N-Channel MOSFETs                                                                                                                  |  |  |

| C <sub>1</sub>                  | Charge Pump Capacitor                                                                                                      | 0.1µF, Charge Pump Capacitor necessary for +12V and +5V operation.                                                                                                                                   |  |  |

| C <sub>2</sub>                  | Time-out Set Capacitor                                                                                                     | $0.047\mu$ F, Provides ~9ms of time-out period prior to latch off during which IOC can be resolved. The duration of current limit time-out (in seconds) = 200k $\Omega$ x C <sub>TIM</sub> (Farads). |  |  |

| C <sub>5</sub>                  | Vdd decoupling capacitor                                                                                                   | 0.1µF, Provides V <sub>DD</sub> decoupling                                                                                                                                                           |  |  |

| JP1<br>JP2<br>JP3<br>JP4        | Jumper to configure PWRON2<br>Jumper to configure VDD<br>Jumper to configure Charge Pump Cap<br>Jumper to configure PWRON1 | See Table 3 for jumper configuration descriptions                                                                                                                                                    |  |  |

| LED1                            | Pgood indicator                                                                                                            | Lit indicates a fault condition                                                                                                                                                                      |  |  |

| W1                              | NOT PROVIDED                                                                                                               | Tie point for dedicated +12V HIP1012 supply, use in default configuration                                                                                                                            |  |  |

| TP1 - TP14                      | Test Points for HIP1012 pin 1 to pin 14                                                                                    |                                                                                                                                                                                                      |  |  |

| P1 - P2                         | Edge connector fingers                                                                                                     | Modify edge connector finger lengths for power sequencing                                                                                                                                            |  |  |

| LOAD BOARD                      |                                                                                                                            |                                                                                                                                                                                                      |  |  |

| SW11 and RL1                    | 5V high load (7 $\Omega$ )                                                                                                 | Switch and load resistor pair to invoke high current load on 5V                                                                                                                                      |  |  |

| SW12 and RL2                    | 5V low load (10Ω)                                                                                                          | Switch and load resistor pair to invoke low current load on 5V                                                                                                                                       |  |  |

| SW13 and RL3                    | 3.3V high load (0.8 $\Omega$ )                                                                                             | Switch and load resistor pair to invoke high current load on 3.3V                                                                                                                                    |  |  |

| SW14 and RL4                    | 3.3V low load (1.6Ω)                                                                                                       | Switch and load resistor pair to invoke low current load on 3.3V                                                                                                                                     |  |  |

| LED2, LED3                      | Load "HOT" indicators                                                                                                      | Lit indicates N-Channel MOSFETs are on and loads are HOT                                                                                                                                             |  |  |

| BUS BOARD                       |                                                                                                                            |                                                                                                                                                                                                      |  |  |

|                                 |                                                                                                                            | Bus interconnect board                                                                                                                                                                               |  |  |

|                                 |                                                                                                                            |                                                                                                                                                                                                      |  |  |

## HIP1012 Evaluation Circuit for Disk Drive Hot Swap HIP1012EVAL2

### Introduction

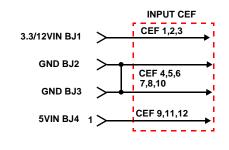

The HIP1012EVAL2 is specifically designed to test and demonstrate hot swapping of disk drives onto passive 12V and 5V power buses using the HIP1012 Hot-Swap control IC. The small size of the board allows it to be included in a shuttle alongside the disk drive during evaluation. The outlined area on the board represents the actual area used for PCB implementation.

## Description

The HIP1012EVAL2 board is provided with a standard Molex four-terminal disk-drive power connector. The solder holes J2 allows the board to be connected to a power supply connector on the disk-drive shuttle. PGOOD, PWRON1, PWRON2, 5VG. 12VG, CTIM, V<sub>DD</sub> and GND are all accessible through a ribbon cable.

With JP1 installed, the HIP1012 is powered from the same 12V power supply as the disk drive motor. JP2 connects the control signal  $\overline{PWRON2}$  to ground allowing the unit to be plugged directly into the power bus for automatic, controlled start up. In this configuration,  $\overline{PWRON1}$  is available to reset the HIP1012 in case of an over-current trip. Otherwise the HIP1012 can be reset by toggling the voltage on V<sub>DD</sub>. With JP2 removed, the circuit is controlled using one or both of the  $\overline{PWRON}$  signal lines. The HIP1012EVAL2 is shipped with both jumpers installed.

The HIP1012EVAl2 is configured with a  $10k\Omega$  RILIM resistor (R<sub>5</sub>) setting the nominal current limit threshold to 100mV. The 12V current sense resistor (R<sub>2</sub>) is  $20m\Omega$  and the 5V current sense resistor (R<sub>1</sub>) is  $100m\Omega$ . These values set the nominal current limits to 5A and 1A respectively. The C<sub>TIM</sub> capacitor (C<sub>2</sub>) sets the time out period to approximately 9ms.

# Control Connections, Fault Notification, and Test Points

HIP1012 EVAL2 is shipped with JP2 installed so that a connected disk drive is started simply by connecting 12V and 5V power supplies to J2. In this configuration, the ribbon cable is not necessary, since the HIP1012 can be reset by toggling the voltage on V<sub>DD</sub>. This configuration represents a disk drive that would be removed after any over-current trip and would start immediately upon insertion. Additional control is available using the ribbon cable and resetting the HIP1012 by applying a rising edge to PWRON1. If redundant control is desired, removing JP2 makes the second control signal PWRON2 available to start or reset the chip. An example of this control configuration would be to turn the chip on using PWRON1 and reset it using PWRON2. The PGOOD pin is an open drain logic output which can be tied high through a resistor for fault indication. Upon detection of either over-current or under-voltage fault conditions, PGOOD goes low and remains low until the fault condition is cleared.

Also included on the ribbon cable are additional monitor points for 12VG, 5VG and  $C_{TIM}$ . These are included for monitoring during evaluation and they are not necessary for operation.

## Data Line Considerations

The HIP1012 does not integrate data bus line switches, although control of the data bus can be assisted by the timeout feature of the HIP1012. During the time-out period, the operating system software can determine whether to halt I/O activity to a disk drive which is undergoing an under-voltage or over-current fault as indicated by the status of PGOOD.

FIGURE 14. HIP1012 EVALUATION CIRCUIT FOR DISK DRIVE HOT PLUG

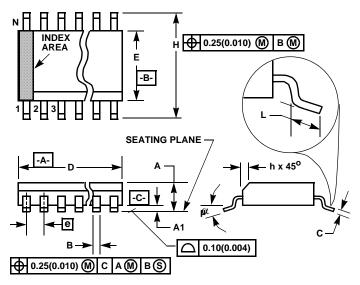

#### Small Outline Plastic Packages (SOIC)

#### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

#### M14.15 (JEDEC MS-012-AB ISSUE C) 14 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES         |                | MILLIMETERS    |                |       |

|--------|----------------|----------------|----------------|----------------|-------|

| SYMBOL | MIN            | MAX            | MIN            | MAX            | NOTES |

| А      | 0.0532         | 0.0688         | 1.35           | 1.75           | -     |

| A1     | 0.0040         | 0.0098         | 0.10           | 0.25           | -     |

| В      | 0.013          | 0.020          | 0.33           | 0.51           | 9     |

| С      | 0.0075         | 0.0098         | 0.19           | 0.25           | -     |

| D      | 0.3367         | 0.3444         | 8.55           | 8.75           | 3     |

| Е      | 0.1497         | 0.1574         | 3.80           | 4.00           | 4     |

| е      | 0.050 BSC      |                | 1.27 BSC       |                | -     |

| Н      | 0.2284         | 0.2440         | 5.80           | 6.20           | -     |

| h      | 0.0099         | 0.0196         | 0.25           | 0.50           | 5     |

| L      | 0.016          | 0.050          | 0.40           | 1.27           | 6     |

| Ν      | 14             |                | 14             |                | 7     |

| α      | 0 <sup>0</sup> | 8 <sup>0</sup> | 0 <sup>0</sup> | 8 <sup>0</sup> | -     |

Rev. 0 12/93

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com