## **16 Channel High Voltage Analog Switch**

#### **Ordering Information**

|                                  | Package Options  |          |  |  |  |  |  |

|----------------------------------|------------------|----------|--|--|--|--|--|

| V <sub>PP</sub> -V <sub>NN</sub> | 48-lead TQFP Die |          |  |  |  |  |  |

| 220V                             | HV20822FG        | HV20822X |  |  |  |  |  |

#### **Features**

- □ HVCMOS<sup>®</sup> technology for high performance

- 220V operating conditions

- Output On-resistance typically 22Ω

- □ 5.0V and 12.0V CMOS logic compatibility

- -45dB min off isolation at 7.5MHz

- Low parasitic capacitance

- Excellent noise immunity

- □ Flexible high voltage supplies

# Absolute Maximum Ratings\*

| $V_{_{DD}}$ Logic power supply voltage           | je           | -0.5V to +15V                      |

|--------------------------------------------------|--------------|------------------------------------|

| V <sub>PP</sub> - V <sub>NN</sub> Supply voltage |              | +225V                              |

| $V_{_{PP}}$ Positive high voltage supp           | oly -C       | 0.5V to V <sub>NN</sub> +225V      |

| $V_{_{\rm NN}}$ Negative high voltage sup        | oply         | +0.5V to -225V                     |

| Logic input voltages                             | -            | 0.5V to V <sub>DD</sub> +0.3V      |

| V <sub>sig</sub> Analog Signal Range             |              | $V_{_{\rm NN}}$ to $V_{_{\rm PP}}$ |

| Peak analog signal current/ch                    | annel        | 3.0A                               |

| Storage temperature                              |              | -65°C to +150°C                    |

| Power dissipation                                | 48-lead TQFP | 1.0W                               |

\* All voltages are referenced to ground. Absolute maximum ratings are those values which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability.

#### **General Description**

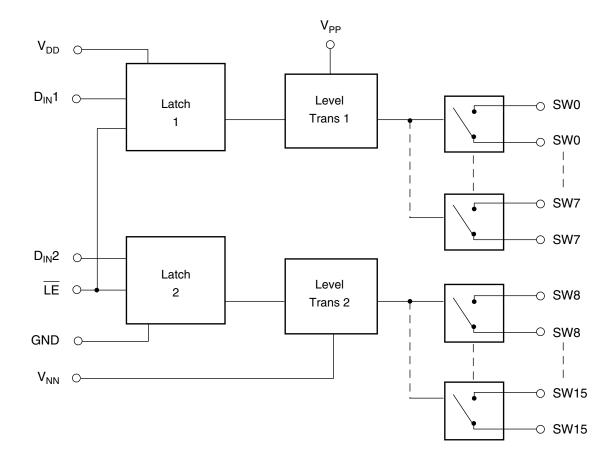

The Supertex HV208 is a 220V 16-channel high-voltage analog switch integrated circuit (IC) configured as 2 sets of 8 single pole single throw analog switches. It is intended for use in applications requiring high voltage switching controlled by low voltage control signals such as ultrasound imaging and printers. The 2 sets of 8 analog switches are controlled by 2 input logic controls,  $D_{IN}1$  and  $D_{IN}2$ . A logic high on  $D_{IN}1$  will turn ON switches 0 to 7 and a logic high on  $D_{IN}2$  will turn ON switches 8 to 15.

#### 06/26/01

Supertex Inc. does not recommend the use of its products in life support applications and will not knowingly sell its products for use in such applications unless it receives an adequate "products liability indemnification insurance agreement." Supertex does not assume responsibility for use of devices described and limits its liability to the replacement of devices determined to be defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the Supertex website: http://www.supertex.com. For complete liability information on all Supertex products, refer to the most current databook or to the Legal/Disclaimer page on the Supertex website.

## **Electrical Characteristics**

DC Characteristics (over recommended operating conditions unless otherwise noted)

| Characteristics                                 | Sym               | 0°C |      | +25°C |     | +70°C |     | L lusite | Test Canditions |                                                                                                                   |

|-------------------------------------------------|-------------------|-----|------|-------|-----|-------|-----|----------|-----------------|-------------------------------------------------------------------------------------------------------------------|

| Characteristics                                 |                   | min | max  | min   | typ | max   | min | max      | Units           | Test Conditions                                                                                                   |

| Small Signal Switch (ON)<br>Resistance          | R <sub>ONS</sub>  |     | 30   |       | 26  | 32    |     | 40       |                 | $V_{SIG} = 0V, I_{SIG} = 5mA,$<br>$V_{PP} = 50V, V_{NN} = -170V$                                                  |

|                                                 |                   |     | 25   |       | 22  | 27    |     | 35       | ohms            | $V_{SIG} = 0V$ , $I_{SIG} = 200$ mA,<br>$V_{PP} = 50V$ , $V_{NN} = -170V$                                         |

|                                                 |                   |     | 15   |       | 22  | 27    |     | 30       |                 | $V_{SIG} = 0V, I_{SIG} = 5mA,$<br>$V_{PP} = 110V, V_{NN} = -110V$                                                 |

|                                                 |                   |     | 20   |       | 18  | 22    |     | 25       |                 | $\label{eq:sigma_sigma} \begin{array}{l} V_{SIG}=0V,\ I_{SIG}=200mA,\\ V_{PP}=110V,\ V_{NN}=-110V \end{array}$    |

| Small Signal Switch (ON)<br>Resistance Matching | ΔR <sub>ONS</sub> |     | 20   |       | 5.0 | 20    |     | 20       | %               | $\label{eq:V_SIG} \begin{array}{l} V_{SIG} = 0V, \ I_{SIG} = 5mA, \\ V_{PP} = 110V, \ V_{NN} = -110V \end{array}$ |

| Large Signal Switch (ON)<br>Resistance          | R <sub>ONL</sub>  |     |      |       | 15  |       |     |          | ohms            | $V_{SIG} = 0V, I_{SIG} = 1.0A$                                                                                    |

| Switch Off Leakage<br>Per Switch                | I <sub>SOL</sub>  |     | 5.0  |       | 1.0 | 10    |     | 15       | μA              | $V_{SIG}$ = $V_{PP}$ -10V and $V_{NN}$ +10V                                                                       |

| DC Offset Switch OFF                            |                   | 300 |      |       | 100 | 300   |     | 300      |                 | R <sub>L</sub> = 100Kohms                                                                                         |

| DC Offset Switch ON                             |                   | 500 |      |       | 100 | 500   |     | 500      | mV              | R <sub>L</sub> = 100Kohms                                                                                         |

| Pos. HV Supply Current                          | I <sub>PPQ</sub>  |     |      |       | 10  | 50    |     |          |                 | All SWs OFF                                                                                                       |

| Neg. HV Supply Current                          | I <sub>NNQ</sub>  |     |      |       | -10 | -50   |     |          | μA              | All SWs OFF                                                                                                       |

| Pos. HV Supply Current                          | I <sub>PPQ</sub>  |     |      |       | 10  | 50    |     |          |                 | All SWs ON, I <sub>SW</sub> = 5 mA                                                                                |

| Neg. HV Supply Current                          | I <sub>NNQ</sub>  |     |      |       | -10 | -50   |     |          |                 | All SWs ON, I <sub>SW</sub> = 5 mA                                                                                |

| Switch Output Peak Current                      |                   |     | 3.0  |       | 3.0 | 2.0   |     | 2.0      | A               | $V_{SIG}$ duty cycle $\leq 0.1\%$                                                                                 |

| Output Switch Frequency                         | f <sub>SW</sub>   |     |      |       |     | 50    |     |          | KHz             | Duty Cycle = 50%                                                                                                  |

| I <sub>PP</sub> Supply Current                  | I <sub>PP</sub>   |     | 8.1  |       |     | 8.8   |     | 10       |                 | $V_{PP} = 50V, V_{NN} = -170V, ALL SWs$                                                                           |

| I <sub>NN</sub> Supply Current                  | I <sub>NN</sub>   |     | -8.1 |       |     | -8.8  |     | -10      | mA              | turning ON and OFF at 50KHz                                                                                       |

| I <sub>PP</sub> Supply Current                  | I <sub>PP</sub>   |     | 5    |       |     | 6.3   |     | 6.9      |                 | $V_{PP} = 110V, V_{NN} = -110V, All SWs$                                                                          |

| I <sub>NN</sub> Supply Current                  | I <sub>NN</sub>   |     | -5   |       |     | -6.3  |     | -6.9     |                 | turning ON and OFF at 50kHz                                                                                       |

| Logic Supply Quiescent Current                  | IDDQ              |     | 10   |       |     | 10    |     | 10       | μA              | All logic states are at DC                                                                                        |

| Logic Supply Average Current                    | I <sub>DD</sub>   |     | 2.0  |       |     | 2.0   |     | 2.0      | mA              | $D_{IN}1 = D_{IN}2 = 3MHz, \overline{LE} = high$                                                                  |

## **Electrical Characteristics**

AC Characteristics (over recommended operating conditions unless otherwise noted)

| Characteristics                                 | Sym                   | O°C |     | +25°C |      | +70°C |     | Linita | To at O an dition o |                                              |

|-------------------------------------------------|-----------------------|-----|-----|-------|------|-------|-----|--------|---------------------|----------------------------------------------|

|                                                 |                       | min | max | min   | typ  | max   | min | max    | Units               | Test Conditions                              |

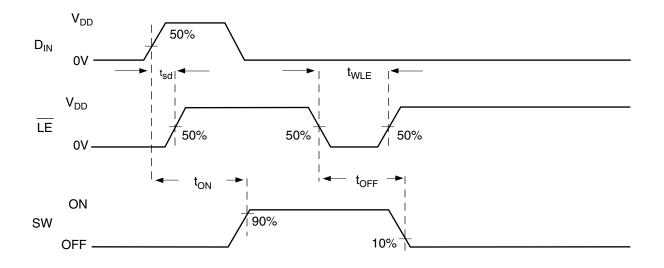

| Time to Turn OFF V <sub>SIG</sub> *             | t <sub>SIG(OFF)</sub> | 0   |     | 0     |      |       | 0   |        | ns                  |                                              |

| Time Width of LE                                | t <sub>WLE</sub>      | 150 |     | 150   |      |       | 150 |        | ns                  |                                              |

| Time Width of D <sub>IN</sub>                   | t <sub>WDIN</sub>     | 150 |     | 150   |      |       | 150 |        | ns                  |                                              |

| Set Up Time Before $\overline{\text{LE}}$ Rises | t <sub>SD</sub>       | 150 |     | 150   |      |       | 150 |        | ns                  |                                              |

| Turn On Time                                    | t <sub>ON</sub>       |     | 2.0 |       |      | 2.0   |     | 2.0    | μs                  | $V_{SIG}=V_{PP}$ - 10V, $R_{LOAD}=10K\Omega$ |

| Turn Off Time                                   | t <sub>OFF</sub>      |     | 2.0 |       |      | 2.0   |     | 2.0    | μs                  | $V_{SIG}=V_{PP}$ - 10V, $R_{LOAD}=10K\Omega$ |

| Off Isolation                                   | ко                    | -30 |     | -30   | -33  |       | -30 |        | dB                  | f = 5.0MHz, 1KΩ/15pF Load                    |

|                                                 |                       | -45 |     | -45   | -50  |       | -45 |        | dB                  | f = 7.5MHz, $R_{LOAD} = 50\Omega$            |

| Switch Crosstalk                                | K <sub>CR</sub>       | -45 |     | -45   |      |       | -45 |        | dB                  | f = 5.0MHz, $R_{LOAD} = 50\Omega$            |

| Off Capacitance Switch to GND                   | C <sub>GS(OFF)</sub>  | 5.0 | 17  | 5.0   | 12   | 17    | 5.0 | 17     | pF                  | V <sub>SIG</sub> = 0V, 1MHz                  |

| On Capacitance Switch to GND                    | C <sub>GS(ON)</sub>   | 25  | 50  | 25    | 38   | 50    | 25  | 50     | pF                  | V <sub>SIG</sub> = 0V, 1MHz                  |

| Output Voltage Spike                            | +V <sub>SPK</sub>     |     |     |       | 4.0  |       |     |        | V                   |                                              |

|                                                 | -V <sub>SPK</sub>     |     |     |       | -4.0 |       |     |        | ]                   |                                              |

\*Time required for analog signal to turn off before output switch turns off.

#### **Operating Conditions**

| Symbol           | Parameter                                       | Value                                        |  |  |  |

|------------------|-------------------------------------------------|----------------------------------------------|--|--|--|

| V <sub>PP</sub>  | Positive high voltage supply <sup>1</sup>       | +50V to +110V                                |  |  |  |

| V <sub>NN</sub>  | Negative high voltage supply <sup>1</sup>       | -10V to V <sub>PP</sub> -220V                |  |  |  |

| V <sub>DD</sub>  | Logic power supply voltage <sup>1</sup>         | 4.75V to +12.6V                              |  |  |  |

| V <sub>IH</sub>  | High-level input voltage                        | V <sub>DD</sub> -1.0V to V <sub>DD</sub>     |  |  |  |

| V <sub>IL</sub>  | Low-level input voltage                         | 0V to 1.0V                                   |  |  |  |

| V <sub>SIG</sub> | Analog signal voltage peak-to-peak <sup>2</sup> | V <sub>NN</sub> +10V to V <sub>PP</sub> -10V |  |  |  |

| T <sub>A</sub>   | Operating free air-temperature                  | 0°C to 70°C                                  |  |  |  |

Notes:

1 Power up/down sequence is arbitrary except GND must be powered-up first and powered-down last.

2  $V_{SIG}$  must be  $V_{NN} \le V_{SIG} \le V_{PP}$  or floating during power up/down transition.

#### **Truth Table**

| D <sub>IN</sub> 2 | D <sub>IN</sub> 1 | LE | SW0 to SW7          | SW8 to SW15 |  |  |

|-------------------|-------------------|----|---------------------|-------------|--|--|

| L                 | L                 | L  | OFF                 | OFF         |  |  |

| L                 | н                 | L  | ON                  | OFF         |  |  |

| Н                 | L                 | L  | OFF                 | ON          |  |  |

| Н                 | н                 | L  | ON                  | ON          |  |  |

| Х                 | Х                 | Н  | HOLD PREVIOUS STATE |             |  |  |

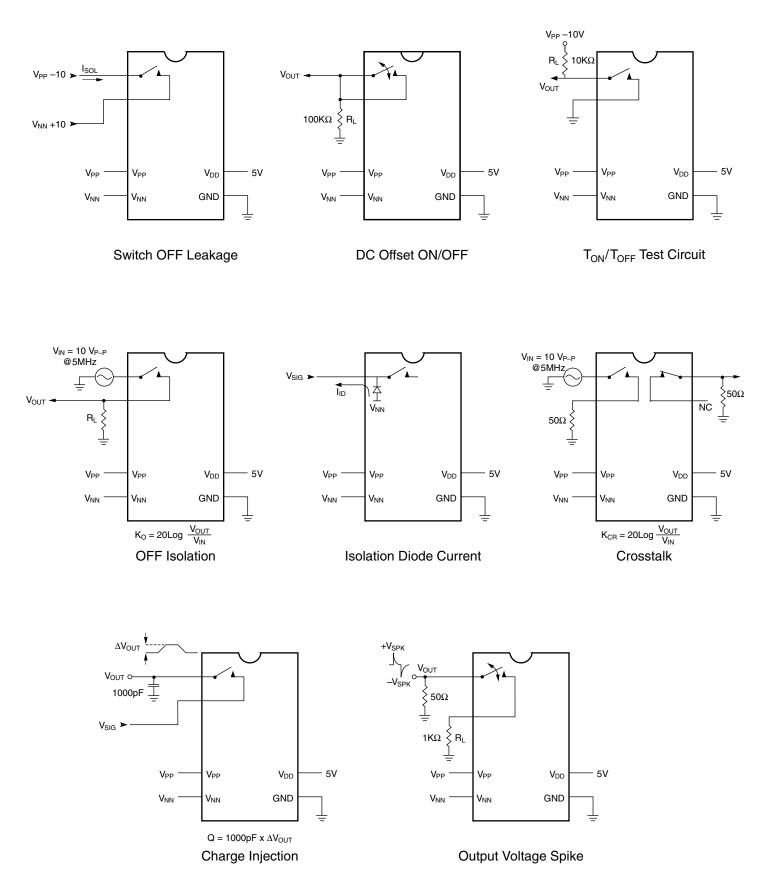

## **Test Circuits**

## **Logic Timing Waveform**

#### **Block Diagram**

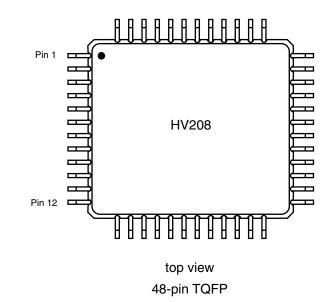

## **Pin Configuration**

#### HV208 48-Pin TQFP

| Pin | Function          | Pin | Function |

|-----|-------------------|-----|----------|

| 1   | V <sub>NN</sub>   | 25  | SW10     |

| 2   | N/C               | 26  | SW10     |

| 3   | V <sub>PP</sub>   | 27  | SW9      |

| 4   | N/C               | 28  | SW9      |

| 5   | D <sub>IN</sub> 1 | 29  | SW8      |

| 6   | LE                | 30  | SW8      |

| 7   | D <sub>IN</sub> 2 | 31  | SW7      |

| 8   | N/C               | 32  | SW7      |

| 9   | N/C               | 33  | SW6      |

| 10  | V <sub>DD</sub>   | 34  | SW6      |

| 11  | GND               | 35  | SW5      |

| 12  | N/C               | 36  | SW5      |

| 13  | N/C               | 37  | SW4      |

| 14  | SW15              | 38  | N/C      |

| 15  | SW15              | 39  | SW4      |

| 16  | SW14              | 40  | N/C      |

| 17  | SW14              | 41  | SW3      |

| 18  | SW13              | 42  | SW3      |

| 19  | SW13              | 43  | SW2      |

| 20  | SW12              | 44  | SW2      |

| 21  | SW12              | 45  | SW1      |

| 22  | SW11              | 46  | SW1      |

| 23  | SW11              | 47  | SW0      |

| 24  | N/C               | 48  | SW0      |

## Package Outline

**Supertex inc.** ©2001 Supertex Inc. All rights reserved. Unauthorized use or reproduction prohibited.