# **High Voltage Ring Generator**

#### Ordering Information

| Operating Voltage                  | Package Options |

|------------------------------------|-----------------|

| V <sub>PP1</sub> -V <sub>NN1</sub> | SOW-20          |

| 325V                               | HV430WG         |

#### **Features**

- 105Vrms ring signal

- Output over current protection

- 5.0V CMOS logic control

- Logic enable/disable to save power

- Adjustable deadband in single-control mode

- Power-on reset

- Fault output for problem detection

#### **Applications**

- Line access cards

- ☐ Set-top/Street box

## **Absolute Maximum Ratings**

| $V_{\mbox{\scriptsize PP1}}-V_{\mbox{\scriptsize NN1}},$ power supply voltage | +340V           |

|-------------------------------------------------------------------------------|-----------------|

| V <sub>PP1</sub> , positive high voltage supply                               | +220V           |

| V <sub>PP2</sub> , positive gate voltage supply                               | +220V           |

| V <sub>NN1</sub> , negative high voltage supply                               | -220V           |

| V <sub>NN2</sub> , negative gate voltage supply                               | -220V           |

| V <sub>DD</sub> , logic supply                                                | +7.5V           |

| Storage temperature                                                           | -65°C to +150°C |

| Power dissipation                                                             | 600mW           |

#### **General Description**

The Supertex HV430 is a high voltage PWM ring generator integrated circuit. The high voltage outputs,  $V_{PGATE}$  and  $V_{NGATE}$ , are used to drive the gates of external high voltage P-channel and N-channel MOSFETs in a push-pull configuration. Over current protection is implemented for both the P-channel and N-channel MOSFETs. External sense resistors set the over-current trip point.

The RESET input functions as a power-on reset when connected to an external capacitor.

The FAULT output indicates an over-current condition and is cleared after 4 consecutive cycles with no overcurrent condition. A logic low on RESET or ENABLE clears the FAULT output. It is active-low and open-drain to allow wire OR'ing of multiple drivers.

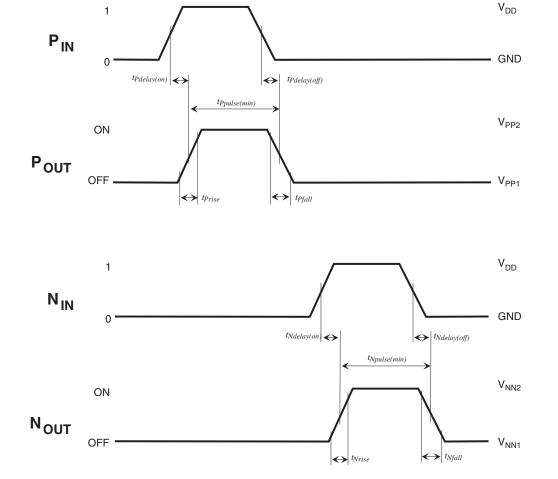

$P_{\text{gate}}$  and  $N_{\text{gate}}$  are controlled independently by logic inputs  $P_{\text{IN}}$  and  $N_{\text{IN}}$  when the MODE pin is at logic high. A logic high on  $P_{\text{IN}}$  will turn on the external P-channel MOSFET. Similarly, a logic high on  $N_{\text{IN}}$  will turn on the external N-channel MOSFET. Lockout circuitry prevents the N and P switches from turning on simultaneously. A pulse width limiter restricts pulse widths to no less than 100-200ns.

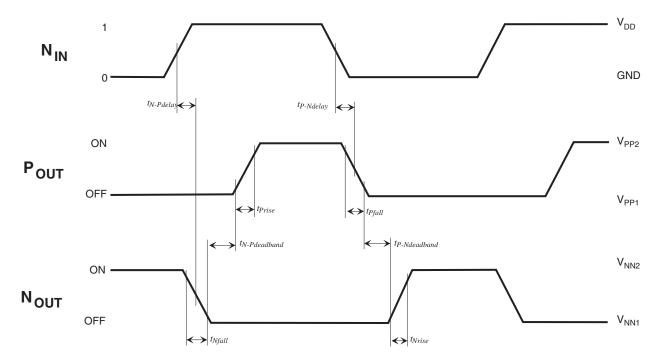

For applications where a single control input is desired, the MODE pin should be connected to SGND. The PWM control signal is then input to the  $N_{\text{IN}}$  pin. A user-adjustable deadband in the control logic ensures break-before-make on the outputs, thus avoiding cross conduction on the high voltage output during switching. A logic high on  $N_{\text{IN}}$  will turn the external P-Channel MOSFET on and the N-Channel off, and vice versa. The IC can be powered down by applying a logic low on the ENABLE pin, placing both external MOSFETs in the off state.

## **Electrical Characteristics**

(Over operating supply voltage unless otherwise specified,  $T_A = -40$ °C to +85°C.)

## **External Supplies**

| Symbol            | Parameter                          | Min                   | Тур | Max  | Unit | Conditions                                                             |

|-------------------|------------------------------------|-----------------------|-----|------|------|------------------------------------------------------------------------|

| V <sub>PP1</sub>  | High voltage positive supply       | 50                    |     | 200  | V    |                                                                        |

| I <sub>PP1Q</sub> | V <sub>PP</sub> quiescent current  |                       | 250 | 500  | μΑ   | P <sub>IN</sub> =N <sub>IN</sub> =0V                                   |

| I <sub>PP1</sub>  | V <sub>PP</sub> operating current  |                       |     | 2.0  | mA   | No load $V_{\text{OUTP}}$ and $V_{\text{OUTN}}$ switching at 100kHz    |

| V <sub>NN1</sub>  | High voltage negative supply       | V <sub>PP1</sub> -325 |     | -50  | V    |                                                                        |

| I <sub>NN1Q</sub> | V <sub>NN1</sub> quiescent current |                       | 250 | 500  | μΑ   | $P_{IN}=N_{IN}=0V$ , $R_{DB}=18k\Omega$                                |

| I <sub>NN1</sub>  | V <sub>NN1</sub> operating current |                       |     | 1.0  | mA   | No load<br>V <sub>OUTP</sub> and V <sub>OUTN</sub> switching at 100kHz |

| $V_{DD}$          | Logic supply voltage               | 4.50                  |     | 5.50 | V    |                                                                        |

| I <sub>DDQ</sub>  | V <sub>DD</sub> quiescent current  |                       | 300 | 400  | μΑ   | $P_{IN}=N_{IN}=0V$ , $R_{DB}=18k\Omega$                                |

| I <sub>DD</sub>   | V <sub>DD</sub> operating current  |                       |     | 1.0  | mA   | $P_{IN}=N_{IN}=100kHz, R_{DB}=18k\Omega$                               |

#### **Internal Supplies**

| Symbol    | Parameter                                | Min                  | Тур | Max                  | Unit | Conditions |

|-----------|------------------------------------------|----------------------|-----|----------------------|------|------------|

| $V_{PP2}$ | Positive linear regulator output voltage | V <sub>PP1</sub> -16 |     | V <sub>PP1</sub> -10 | ٧    |            |

| $V_{NN2}$ | Negative linear regulator output voltage | $V_{NN1}$ +10        |     | $V_{NN1}$ +14        | ٧    |            |

#### **Positive High Voltage Output**

| Symbol                | Parameter                                                   | Min                    | Тур                   | Max                    | Unit | Conditions                    |

|-----------------------|-------------------------------------------------------------|------------------------|-----------------------|------------------------|------|-------------------------------|

| V <sub>Pgate</sub>    | Output voltage swing                                        | $V_{PP2}$              |                       | $V_{PP1}$              | V    | No load on V <sub>Pgate</sub> |

| R <sub>sourceP</sub>  | V <sub>Pgate</sub> source resistance                        |                        |                       | 12.5                   | Ω    | I <sub>OUT</sub> =80mA        |

| R <sub>sinkP</sub>    | V <sub>Pgate</sub> sink resistance                          |                        |                       | 12.5                   | Ω    | I <sub>OUT</sub> =-80mA       |

| t <sub>riseP</sub>    | V <sub>Pgate</sub> rise time                                |                        |                       | 50                     | ns   | C <sub>load</sub> =1.4nF      |

| t <sub>fallP</sub>    | V <sub>Pgate</sub> fall time                                |                        |                       | 50                     | ns   | C <sub>load</sub> =1.4nF      |

| t <sub>pwp(min)</sub> | V <sub>Pgate</sub> minimum pulse width (internally limited) | 100                    | 150                   | 200                    | ns   |                               |

| t <sub>delayP</sub>   | P <sub>IN</sub> to Pgate delay time                         |                        |                       | 300                    | ns   | mode=1                        |

| V <sub>Psen</sub>     | V <sub>Pgate</sub> current sense voltage                    | V <sub>PP1</sub> -0.85 | V <sub>PP1</sub> -1.0 | V <sub>PP1</sub> -1.15 | V    |                               |

| t <sub>shortP</sub>   | V <sub>Pgate</sub> current sense off time                   |                        |                       | 150                    | ns   |                               |

## **Negative High Voltage Output**

| Symbol                | Parameter                                                   | Min                    | Тур                   | Max                    | Unit | Conditions                    |

|-----------------------|-------------------------------------------------------------|------------------------|-----------------------|------------------------|------|-------------------------------|

| V <sub>Ngate</sub>    | Output voltage swing                                        | V <sub>NN2</sub>       |                       | V <sub>NN1</sub>       | V    | No load on V <sub>Ngate</sub> |

| R <sub>sourceN</sub>  | V <sub>Ngate</sub> source resistance                        |                        |                       | 15.0                   | Ω    | I <sub>OUT</sub> =80mA        |

| R <sub>sinkN</sub>    | V <sub>Ngate</sub> sink resistance                          |                        |                       | 15.0                   | Ω    | I <sub>OUT</sub> =-80mA       |

| t <sub>riseN</sub>    | V <sub>Ngate</sub> rise time                                |                        |                       | 50                     | ns   | C <sub>load</sub> =1.0nF      |

| t <sub>fallN</sub>    | V <sub>Ngate</sub> fall time                                |                        |                       | 50                     | ns   | C <sub>load</sub> =1.0nF      |

| t <sub>pwn(min)</sub> | V <sub>Ngate</sub> minimum pulse width (internally limited) | 100                    | 150                   | 200                    | ns   |                               |

| t <sub>delayN</sub>   | N <sub>IN</sub> to V <sub>Ngate</sub> delay time            |                        |                       | 300                    | ns   | mode=1                        |

| V <sub>Nsen</sub>     | V <sub>Ngate</sub> current sense voltage                    | V <sub>NN1</sub> +0.85 | V <sub>NN1</sub> +1.0 | V <sub>NN1</sub> +1.15 | V    |                               |

| t <sub>shortN</sub>   | V <sub>Ngate</sub> current sense OFF time                   |                        |                       | 150                    | ns   |                               |

# **Control Circuitry**

| Symbol                         | Parameter                                                           | Min  | Тур | Max  | Unit                                    | Conditions                                      |

|--------------------------------|---------------------------------------------------------------------|------|-----|------|-----------------------------------------|-------------------------------------------------|

| V <sub>IL</sub>                | Logic input low voltage                                             | 0    |     | 0.60 | V                                       | V <sub>DD</sub> =5.0V                           |

| V <sub>IH</sub>                | Logic input high voltage                                            | 2.7  |     | 5.0  | V                                       | V <sub>DD</sub> =5.0V                           |

| I <sub>INdn</sub>              | Input pull-down current                                             | 0.5  | 1   | 5    | μА                                      | P <sub>IN</sub> , N <sub>IN</sub> , ENABLE      |

| R <sub>up</sub>                | Input pull-up resistance                                            | 100  | 200 | 300  | kΩ                                      | MODE                                            |

| V <sub>OL</sub>                | Logic output low voltage                                            |      |     | 0.50 | V                                       | V <sub>DD</sub> =5.0V, I <sub>OUT</sub> =-0.5mA |

| V <sub>OH</sub>                | Logic output high voltage                                           | 4.50 |     |      | V                                       | V <sub>DD</sub> =5.0V, I <sub>OUT</sub> =0.5mA  |

| V <sub>RST(OFF)</sub>          | Reset voltage, device off                                           | 3.2  |     | 3.5  | V                                       | V <sub>DD</sub> =5.0V                           |

| V <sub>RST(ON)</sub>           | Reset voltage, device on                                            | 3.7  |     | 4.0  | V                                       | V <sub>DD</sub> =5.0V                           |

| V <sub>RST(HYS)</sub>          | Reset hysteresis voltage                                            | 0.3  |     |      | V                                       | V <sub>DD</sub> =5.0V                           |

| I <sub>reset</sub>             | Reset pull-up current                                               | 7    | 10  | 13   | μА                                      | V <sub>RESET</sub> =0-4.5V                      |

| t <sub>RST(ON)</sub>           | RESET on delay                                                      |      |     | 1.0  | μS                                      |                                                 |

| t <sub>RST(OFF)</sub>          | RESET off delay                                                     |      |     | 1.0  | μS                                      |                                                 |

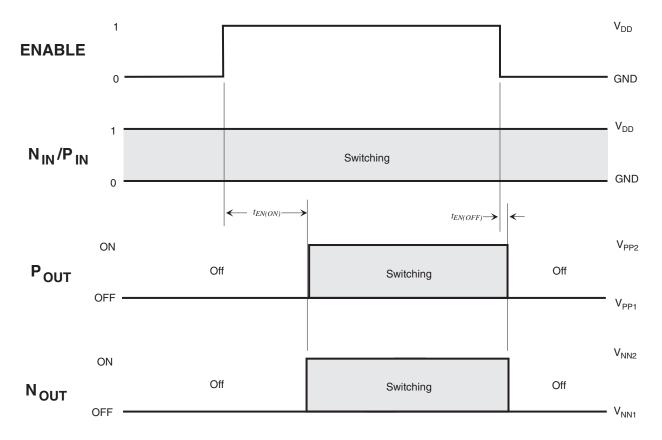

| t <sub>EN(ON)</sub>            | ENABLE on delay                                                     | 50   | 100 | 150  | μS                                      |                                                 |

| t <sub>EN(OFF)</sub>           | ENABLE off delay                                                    |      |     | 1.0  | μS                                      |                                                 |

| t <sub>FLT(HOLD)</sub>         | FAULT hold time                                                     |      | 4   |      | N <sub>IN</sub> /P <sub>IN</sub> cycles | ENABLE=1                                        |

| t <sub>DB</sub>                | Deadband time                                                       | 35   | 50  | 70   | ns                                      | Mode=0, Rdb=5.6kΩ                               |

|                                |                                                                     | 105  | 140 | 175  | ns                                      | Mode=0, Rdb=18kΩ                                |

| t <sub>delay(N-P)</sub>        | N-off to P-on transistion delay                                     |      |     | 300  | ns                                      | Mode=0, Rdb<27k $\Omega$                        |

| t <sub>delay(P-N)</sub>        | P-off to N-on transistion delay                                     |      |     | 300  | ns                                      | Mode=0, Rdb<27kΩ                                |

| $\Delta t_{\text{delay(N-P)}}$ | Delay difference t <sub>delayN(off)</sub> - t <sub>delayP(on)</sub> | -80  | 0   | 80   | ns                                      | Mode=1                                          |

| $\Delta t_{\text{delay(P-N)}}$ | Delay difference t <sub>delayP(off)</sub> - t <sub>delayP(on)</sub> | -80  | 0   | 80   | ns                                      | Mode=1                                          |

## **Truth Table**

|                 | Logic I         | nputs* |    |                           | Ou                           | tput                         |

|-----------------|-----------------|--------|----|---------------------------|------------------------------|------------------------------|

| N <sub>IN</sub> | P <sub>IN</sub> | mode   | EN | RESET                     | External N-Channel<br>MOSFET | External P-Channel<br>MOSFET |

| L               | L               | Н      | Н  | > V <sub>reset(on)</sub>  | OFF                          | OFF                          |

| L               | Н               | Н      | Н  | > V <sub>reset(on)</sub>  | OFF                          | ON                           |

| Н               | L               | Н      | Н  | > V <sub>reset(on)</sub>  | ON                           | OFF                          |

| Н               | Н               | Н      | Н  | > V <sub>reset(on)</sub>  | OFF                          | OFF                          |

| Н               | X               | L      | Н  | > V <sub>reset(on)</sub>  | OFF                          | ON                           |

| L               | X               | L      | Н  | > V <sub>reset(on)</sub>  | ON                           | OFF                          |

| Х               | Х               | Х      | L  | Х                         | OFF                          | OFF                          |

| Х               | Х               | Χ      | Х  | < V <sub>reset(off)</sub> | OFF                          | OFF                          |

$<sup>^{\</sup>ast}$  Unused logic inputs should be connected to  $V_{\text{DD}}$  or GND.

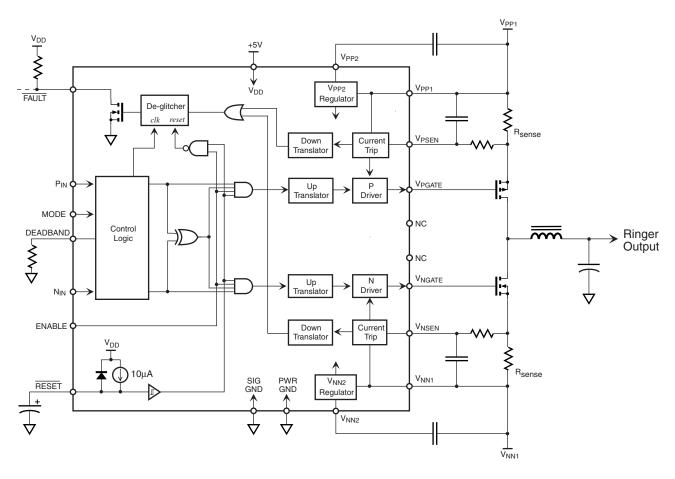

# **Block Diagram and Application Circuit**

Note:  $P_{IN}$ ,  $N_{IN}$ , and ENABLE are internally pulled low. MODE is internally pulled high. A Reset capacitor in the range of 1-10 $\mu$ F will yield a couple-second turn-on delay. Tantalum is recommended.

# **Single-Control Mode Timing**

# **Dual-Control Mode Timing**

# **ENABLE Timing**

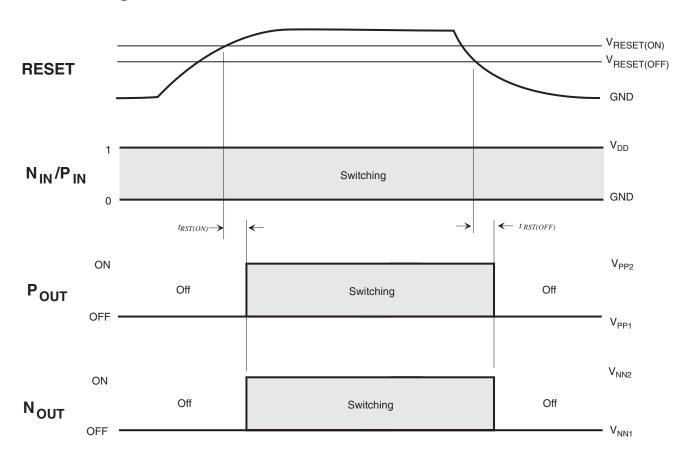

# **RESET Timing**

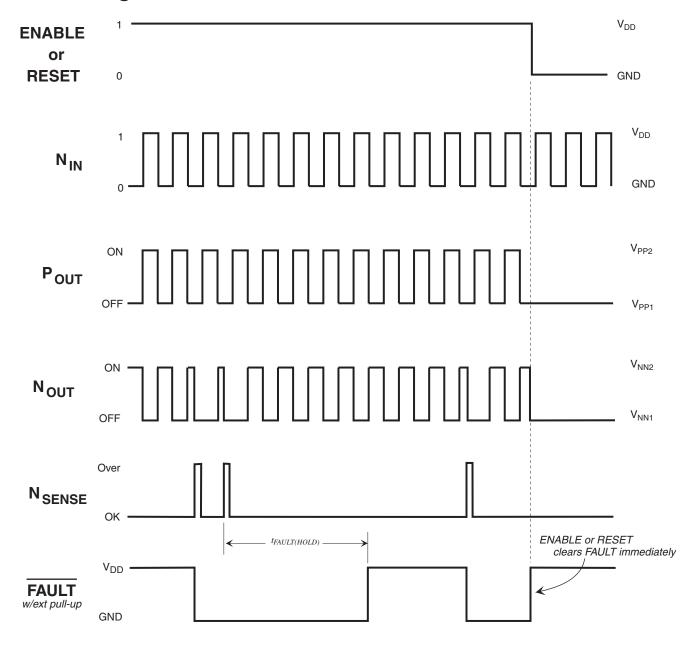

# **FAULT Timing**

Note: N<sub>sense</sub> overcurrent shown. P<sub>sense</sub> operates identically.

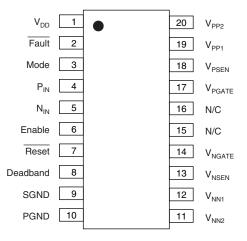

# **Pin Description**

| 1/                 | Desiring high college county                                                                                                                                                                                                                                    |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PP1</sub>   | Positive high voltage supply.                                                                                                                                                                                                                                   |

| V <sub>PP2</sub>   | Positive gate voltage supply. Generated by an internal linear regulator. A 25V, 100nF capacitor should be connected between $V_{PP2}$ and $V_{PP1}$ .                                                                                                           |

| $V_{NN1}$          | Negative high voltage supply.                                                                                                                                                                                                                                   |

| V <sub>NN2</sub>   | Negative gate voltage supply. Generated by an internal linear regulator. A 25V, 100nF capacitor should be connected between $V_{\text{NN2}}$ and $V_{\text{NN1}}$ .                                                                                             |

| $V_{DD}$           | Logic supply voltage.                                                                                                                                                                                                                                           |

| SGnd               | Low voltage logic ground.                                                                                                                                                                                                                                       |

| PGnd               | High voltage power ground.                                                                                                                                                                                                                                      |

| P <sub>IN</sub>    | Logic control input. When mode is high, logic input high turns ON the external high voltage P-channel MOSFET. Internally pulled low.                                                                                                                            |

| N <sub>IN</sub>    | Logic control input. When mode is high, logic input high turns ON the external high voltage N-channel MOSFET. Internally pulled low.                                                                                                                            |

| ENABLE             | Logic enable input. Logic high enables IC. Internally pulled low.                                                                                                                                                                                               |

| MODE               | Logic mode input. 0=single-control; 1=dual-control. When MODE is high, $N_{IN}$ and $P_{IN}$ independently control $N_{OUT}$ and $P_{OUT}$ , respectively. When MODE is low, $N_{IN}$ controls both outputs in a complementary manner. (See Truth Table)        |

| FAULT              | Logic output. Fault is at logic low when either current limit sense pin, V <sub>Psen</sub> or V <sub>Nsen</sub> , is activated. Remains active until overcurrent condition clears or ENABLE=0 or RESET=0.                                                       |

| RESET              | Power-on reset. A capacitor connected between this pin and ground determines the delay time between application of V <sub>DD</sub> and when the device outputs are enabled. Low leakage tantalum recommended.                                                   |

| DEADBAND           | A resistor between this pin and ground sets the 'break-before-make' time between output transitions. Applicable only in single-control mode. For minimum deadtime, a $5.6 \mathrm{k}\Omega$ resistor to ground should be used. For dual-input mode, tie to Vdd. |

| V <sub>Pgate</sub> | Gate drive for external P-channel MOSFET.                                                                                                                                                                                                                       |

| V <sub>Ngate</sub> | Gate drive for external N-channel MOSFET.                                                                                                                                                                                                                       |

| V <sub>Psen</sub>  | Pulse by pulse over current sensing for P-Channel MOSFET.                                                                                                                                                                                                       |

| V <sub>Nsen</sub>  | Pulse by pulse over current sensing for N-Channel MOSFET.                                                                                                                                                                                                       |

# **Pin Configuration**

top view SOW 20

02/25/03