## SONY

# ICX038DNA

### 1/2-inch CCD Image Sensor for NTSC Color Video Cameras

#### Description

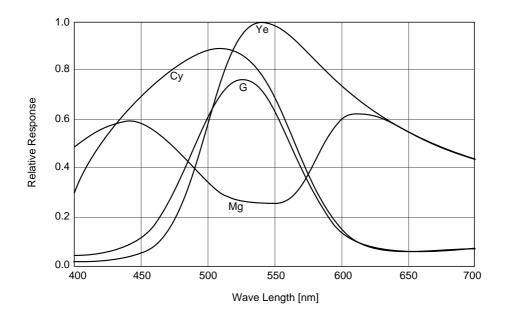

The ICX038DNA is an interline CCD solid-state image sensor suitable for NTSC color video cameras with a 1/2-inch optical system. Smear, sensitivity, Drange, S/N and other characteristics have been greatly improved compared with the ICX038BNA. High sensitivity and low dark current are achieved through the adoption of Ye, Cy, Mg and G complementary color mosaic filters and HAD (Hole-Accumulation Diode) sensors.

This chip features a field period readout system and an electronic shutter with variable charge-storage time.

This chip is compatible with and can replace the ICX038BNA.

#### Features

- Low smear (-20dB compared with the ICX038BNA)

- High sensitivity (+3.0dB compared with the ICX038BNA)

- High D range (+2.5dB compared with the ICX038BNA)

- High S/N

- High resolution and low dark current

- Excellent antiblooming characteristics

- Ye, Cy, Mg, and G complementary color mosaic filters on chip

- Continuous variable-speed shutter

- Substrate bias: Adjustment free (external adjustment also possible with 6 to 14V)

- Reset gate pulse: 5Vp-p adjustment free (drive also possible with 0 to 9V)

- Horizontal register: 5V drive

#### **Device Structure**

Interline CCD image sensor

| <ul> <li>Optical size:</li> </ul>           | 1/2-inch format                                           |

|---------------------------------------------|-----------------------------------------------------------|

| • Number of effective pixels:               | 768 (H) x 494 (V) approx. 380K pixels                     |

| <ul> <li>Total number of pixels:</li> </ul> | 811 (H) x 508 (V) approx. 410K pixels                     |

| Chip size:                                  | 7.95mm (H) x 6.45mm (V)                                   |

| <ul> <li>Unit cell size:</li> </ul>         | 8.4μm (H) x 9.8μm (V)                                     |

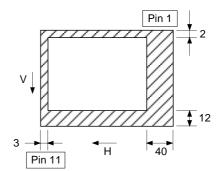

| <ul> <li>Optical black:</li> </ul>          | Horizontal (H) direction : Front 3 pixels, rear 40 pixels |

|                                             | Vertical (V) direction : Front 12 pixels, rear 2 pixels   |

| <ul> <li>Number of dummy bits:</li> </ul>   | Horizontal 22                                             |

|                                             | Vertical 1 (even fields only)                             |

| <ul> <li>Substrate material:</li> </ul>     | Silicon                                                   |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

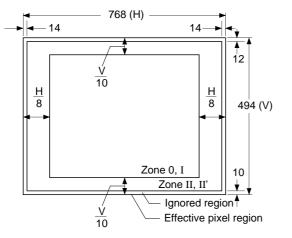

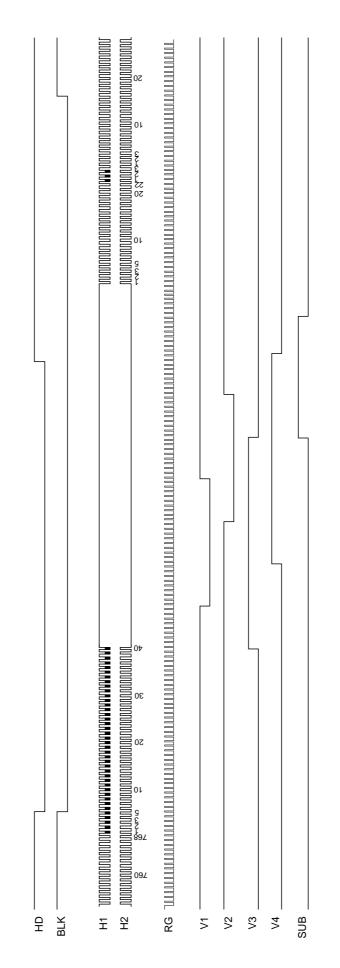

Optical black position (Top View)

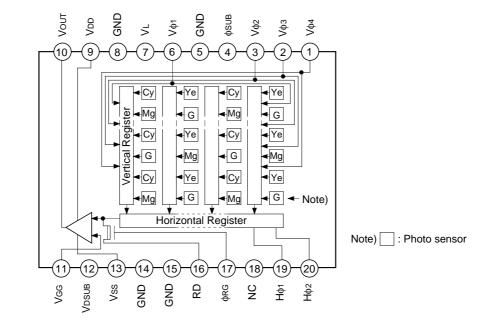

#### **Block Diagram and Pin Configuration**

(Top View)

#### **Pin Description**

| Pin No. | Symbol | Description                      | Pin No. | Symbol      | Description                           |

|---------|--------|----------------------------------|---------|-------------|---------------------------------------|

| 1       | V¢4    | Vertical register transfer clock | 11      | Vgg         | Output circuit gate bias              |

| 2       | Vфз    | Vertical register transfer clock | 12      | Vdsub       | Substrate bias circuit supply voltage |

| 3       | Vø2    | Vertical register transfer clock | 13      | Vss         | Output circuit source                 |

| 4       | фѕив   | Substrate clock                  | 14      | GND         | GND                                   |

| 5       | GND    | GND                              | 15      | GND         | GND                                   |

| 6       | Vφ1    | Vertical register transfer clock | 16      | RD          | Reset drain bias                      |

| 7       | VL     | Protective transistor bias       | 17      | <b>¢</b> RG | Reset gate clock                      |

| 8       | GND    | GND                              | 18      | NC          |                                       |

| 9       | Vdd    | Output circuit supply voltage    | 19      | Ηφ1         | Horizontal register transfer clock    |

| 10      | Vouт   | Signal output                    | 20      | Ηφ2         | Horizontal register transfer clock    |

#### Absolute Maximum Ratings

|                       | Item                              | Ratings     | Unit | Remarks |

|-----------------------|-----------------------------------|-------------|------|---------|

| Substrate clock  \$UB | – GND                             | –0.3 to +50 | V    |         |

| Supply voltogo        | VDD, VRD, VDSUB, VOUT, VSS – GND  | –0.3 to +18 | V    |         |

| Supply voltage        | Vdd, Vrd, Vdsub, Vout, Vss – φsub | –55 to +10  | V    |         |

|                       | Vφ1, Vφ2, Vφ3, Vφ4 – GND          | -15 to +20  | V    |         |

| Clock input voltage   | Vφ1, Vφ2, Vφ3, Vφ4 – φsub         | to +10      | V    |         |

| Voltage difference be | tween vertical clock input pins   | to +15      | V    | *1      |

| Voltage difference be | tween horizontal clock input pins | to +17      | V    |         |

| Ηφ1, Ηφ2 – Vφ4        |                                   | -17 to +17  | V    |         |

| ¢rg, Vgg − GND        |                                   | -10 to +15  | V    |         |

| фrg, Vgg – фsub       |                                   | –55 to +10  | V    |         |

| VL – ØSUB             |                                   | -65 to +0.3 | V    |         |

| Pins other than GND   | and φs∪в – V∟                     | –0.3 to +30 | V    |         |

| Storage temperature   |                                   | -30 to +80  | °C   |         |

| Operating temperatur  | re                                | -10 to +60  | °C   |         |

\*1 +27V (Max.) when clock width < 10 $\mu$ s, clock duty factor < 0.1%.

#### Bias Conditions 1 [when used in substrate bias internal generation mode]

| Item                                  | Symbol | Min.   | Тур.          | Max.     | Unit | Remarks   |

|---------------------------------------|--------|--------|---------------|----------|------|-----------|

| Output circuit supply voltage         | Vdd    | 14.55  | 15.0          | 15.45    | V    |           |

| Reset drain voltage                   | Vrd    | 14.55  | 15.0          | 15.45    | V    | Vrd = Vdd |

| Output circuit gate voltage           | Vgg    | 1.75   | 2.0           | 2.25     | V    |           |

| Output circuit source                 | Vss    | Ground | led with 390Ω | resistor |      |           |

| Protective transistor bias            | VL     |        | *1            |          |      |           |

| Substrate bias circuit supply voltage | Vdsub  | 14.55  | 15.0          | 15.45    | V    |           |

| Substrate clock                       | фѕив   |        |               |          |      |           |

\*1 VL setting is the VvL voltage of the vertical transfer clock waveform, or the same supply voltage as the VL power supply for the V driver should be used. (When CXD1267AN is used.)

\*2 Do not apply a DC bias to the substrate clock pin, because a DC bias is generated within the CCD.

#### Bias Conditions 2 [when used in substrate bias external adjustment mode]

| Item                                   | Symbol | Min.   | Тур.                 | Max.       | Unit | Remarks   |

|----------------------------------------|--------|--------|----------------------|------------|------|-----------|

| Output circuit supply voltage          | Vdd    | 14.55  | 15.0                 | 15.0 15.45 |      |           |

| Reset drain voltage                    | Vrd    | 14.55  | 15.0                 | 15.45      | V    | Vrd = Vdd |

| Output circuit gate voltage            | Vgg    | 1.75   | 2.0                  | 2.25       | V    |           |

| Output circuit source                  | Vss    | Ground | led with $390\Omega$ | resistor   |      |           |

| Protective transistor bias             | VL     |        | *3                   |            |      |           |

| Substrate bias circuit supply voltage  | Vdsub  |        | *4                   |            |      |           |

| Substrate voltage adjustment range     | Vsub   | 6.0    |                      | 14.0       | V    | *5        |

| Substrate voltage adjustment precision | ΔVsub  | -3     |                      | +3         | %    | *5        |

\*3 VL setting is the VvL voltage of the vertical transfer clock waveform, or the same supply voltage as the VL power supply for the V driver should be used. (When CXD1267AN is used.)

\*4 Connect to GND or leave open.

\*5 The setting value of the substrate voltage (Vsub) is indicated on the back of the image sensor by a special code. When adjusting the substrate voltage externally, adjust the substrate voltage to the indicated voltage. The adjustment precision is ±3%. However, this setting value has not significance when used in substrate bias internal generation mode.

VSUB code — one character indication

Code and optimal setting correspond to each other as follows.

| Vsub code       | E   | f   | G   | h   | J   | К   | L   | m   | Ν    | Ρ    | Q    | R    | S    | Т    | U    | V    | W    |

|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|------|------|

| Optimal setting | 6.0 | 6.5 | 7.0 | 7.5 | 8.0 | 8.5 | 9.0 | 9.5 | 10.0 | 10.5 | 11.0 | 11.5 | 12.0 | 12.5 | 13.0 | 13.5 | 14.0 |

<Example> "L"  $\rightarrow$  Vsub = 9.0V

#### **DC Characteristics**

| Item                          | Symbol | Min. | Тур. | Max. | Unit | Remarks |

|-------------------------------|--------|------|------|------|------|---------|

| Output circuit supply current | Idd    |      | 5.0  | 10.0 | mA   |         |

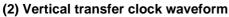

#### **Clock Voltage Conditions**

| Item                          | Symbol                    | Min.  | Тур. | Max.  | Unit | Waveform<br>diagram | Remarks                                       |

|-------------------------------|---------------------------|-------|------|-------|------|---------------------|-----------------------------------------------|

| Readout clock voltage         | Vvт                       | 14.55 | 15.0 | 15.45 | V    | 1                   |                                               |

|                               | Vvh1, Vvh2                | -0.05 | 0    | 0.05  | V    | 2                   | Vvн = (Vvн1 + Vvн2)/2                         |

|                               | Vvнз, Vvн4                | -0.2  | 0    | 0.05  | V    | 2                   |                                               |

|                               | Vvl1, Vvl2,<br>Vvl3, Vvl4 | -9.6  | -9.0 | -8.5  | V    | 2                   | VvL = (VvL3 + VvL4)/2                         |

|                               | Vφv                       | 8.3   | 9.0  | 9.65  | Vp-p | 2                   | $V\phi = V + n - V + n (n = 1 \text{ to } 4)$ |

| Vertical transfer clock       | Vvh1 – Vvh2               |       |      | 0.1   | V    | 2                   |                                               |

| voltage                       | Vvнз — Vvн                | -0.25 |      | 0.1   | V    | 2                   |                                               |

|                               | Vvh4 – Vvh                | -0.25 |      | 0.1   | V    | 2                   |                                               |

|                               | V∨нн                      |       |      | 0.5   | V    | 2                   | High-level coupling                           |

|                               | Vvhl                      |       |      | 0.5   | V    | 2                   | High-level coupling                           |

|                               | Vvlh                      |       |      | 0.5   | V    | 2                   | Low-level coupling                            |

|                               | Vvll                      |       |      | 0.5   | V    | 2                   | Low-level coupling                            |

| Horizontal transfer           | Vфн                       | 4.75  | 5.0  | 5.25  | Vp-p | 3                   |                                               |

| clock voltage                 | Vhl                       | -0.05 | 0    | 0.05  | V    | 3                   |                                               |

|                               | Vrgl                      |       | *1   |       | V    | 4                   |                                               |

| Reset gate clock<br>voltage*1 | Vørg                      | 4.5   | 5.0  | 5.5   | Vp-p | 4                   |                                               |

| Jollage I                     | Vrglh – Vrgll             |       |      | 0.8   | V    | 4                   | Low-level coupling                            |

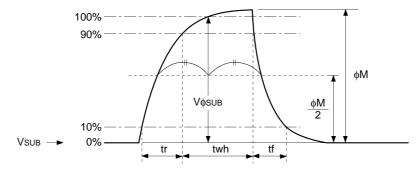

| Substrate clock voltage       | Vфsuв                     | 23.0  | 24.0 | 25.0  | V    | 5                   |                                               |

\*1 Input the reset gate clock without applying a DC bias. In addition, the reset gate clock can also be driven with the following specifications.

| ltem             | Symbol | Min. | Тур. | Max. | Unit | Waveform diagram | Remarks |

|------------------|--------|------|------|------|------|------------------|---------|

| Reset gate clock | Vrgl   | -0.2 | 0    | 0.2  | V    | 4                |         |

| voltage          | Vørg   | 8.5  | 9.0  | 9.5  | Vp-p | 4                |         |

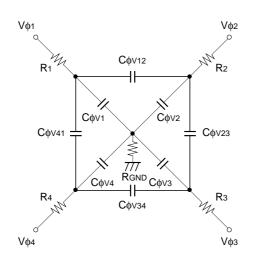

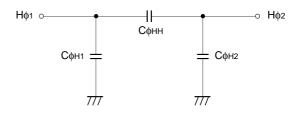

#### **Clock Equivalent Circuit Constant**

| Item                                           | Symbol                     | Min. | Тур. | Max. | Unit | Remarks |

|------------------------------------------------|----------------------------|------|------|------|------|---------|

| Capacitance between vertical transfer clock    | Cφν1, Cφν3                 |      | 1800 |      | pF   |         |

| and GND                                        | <b>C</b> φν2, <b>C</b> φν4 |      | 2200 |      | pF   |         |

| Capacitance between vertical transfer clocks   | Сфv12, Сфv34               |      | 450  |      | pF   |         |

| Capacitance between ventical transier clocks   | Сфv23, Сфv41               |      | 270  |      | pF   |         |

| Capacitance between horizontal transfer clock  | Сфн1                       |      | 64   |      | pF   |         |

| and GND                                        | Сфн2                       |      | 62   |      | pF   |         |

| Capacitance between horizontal transfer clocks | Сфнн                       |      | 47   |      | pF   |         |

| Capacitance between reset gate clock and GND   | Cộrg                       |      | 8    |      | pF   |         |

| Capacitance between substrate clock and GND    | Сфѕив                      |      | 400  |      | pF   |         |

| Vertical transfer clock series resistor        | R1, R2, R3, R4             |      | 68   |      | Ω    |         |

| Vertical transfer clock ground resistor        | Rgnd                       |      | 15   |      | Ω    |         |

Vertical transfer clock equivalent circuit

Horizontal transfer clock equivalent circuit

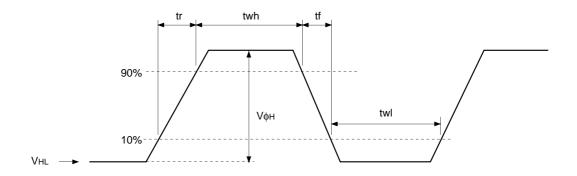

#### **Drive Clock Waveform Conditions**

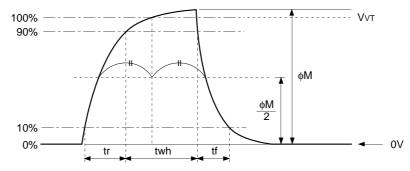

#### (1) Readout clock waveform

$V_{VH} = (V_{VH1} + V_{VH2})/2$  $V_{VL} = (V_{VL3} + V_{VL4})/2$  $V_{\varphi V} = V_{VHN} - V_{VLN} (n = 1 \text{ to } 4)$

#### (3) Horizontal transfer clock waveform

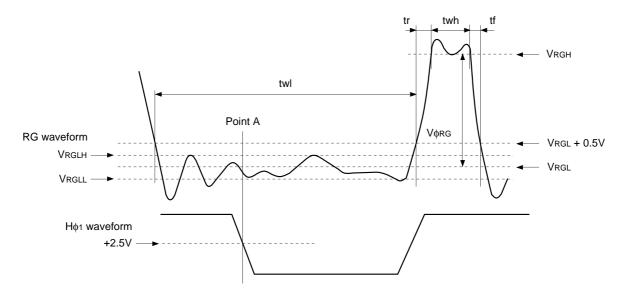

#### (4) Reset gate clock waveform

VRGLH is the maximum value and VRGLL is the minimum value of the coupling waveform during the period from Point A in the above diagram until the rising edge of RG. In addition, VRGL is the average value of VRGLH and VRGLL.

VRGL = (VRGLH + VRGLL)/2

Assuming VRGH is the minimum value during the period twh, then:

Vørg = Vrgh – Vrgl

#### (5) Substrate clock waveform

#### **Clock Switching Characteristics**

|                              | ltom                 | Symbol                |      | twh  |      |      | twl  |      |      | tr   |      |      | tf   |      | Unit | Remarks             |

|------------------------------|----------------------|-----------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|---------------------|

|                              | ltem                 | Symbol                | Min. | Тур. | Max. | Unit | Remarks             |

| Rea                          | adout clock          | Vт                    | 2.3  | 2.5  |      |      |      |      | 0.5  |      |      | 0.5  |      |      | μs   | During<br>readout   |

| Vei<br>clo                   | tical transfer<br>ck | Vφ1, Vφ2,<br>Vφ3, Vφ4 |      |      |      |      |      |      |      |      |      | 15   |      | 250  | ns   | *1                  |

| Horizontal<br>transfer clock | During<br>imaging    | Hφ                    |      | 20   |      |      | 20   |      |      | 15   | 19   |      | 15   | 19   | ns   | *2                  |

| orizo                        | During parallel-     | Hφ1                   |      | 5.38 |      |      |      |      |      | 0.01 |      |      | 0.01 |      | μs   |                     |

| trar<br>trar                 | serial conversion    | Hø2                   |      |      |      |      | 5.38 |      |      | 0.01 |      |      | 0.01 |      | μυ   |                     |

| Re                           | set gate clock       | φRG                   | 11   | 13   |      |      | 51   |      |      | 3    |      |      | 3    |      | ns   |                     |

| Sul                          | ostrate clock        | фSUB                  | 1.5  | 1.8  |      |      |      |      |      |      | 0.5  |      |      | 0.5  | μs   | During drain charge |

\*1 When vertical transfer clock driver CXD1267AN is used.

\*2 tf  $\geq$  tr – 2ns.

| Item                                  | Symbol   |      | two  | Unit | Remarks |         |  |

|---------------------------------------|----------|------|------|------|---------|---------|--|

| i i i i i i i i i i i i i i i i i i i | Gymbol   | Min. | Тур. | Max. | Unit    | Remarks |  |

| Horizontal transfer clock             | Ηφ1, Ηφ2 | 16   | 20   |      | ns      | *3      |  |

\*3 The overlap period for twh and twl of horizontal transfer clocks H $\phi_1$  and H $\phi_2$  is two.

#### **Image Sensor Characteristics**

| (Ta = 25°C) | ) |

|-------------|---|

|-------------|---|

| Item                     | Symbol | Min. | Тур.    | Max.    | Unit | Measurement method | Remarks       |

|--------------------------|--------|------|---------|---------|------|--------------------|---------------|

| Sensitivity              | S      | 550  | 660     |         | mV   | 1                  |               |

| Saturation signal        | Ysat   | 800  |         |         | mV   | 2                  | Ta = 60°C     |

| Smear                    | Sm     |      | 0.00032 | 0.00056 | %    | 3                  |               |

| Video signal shading     | SHy    |      |         | 20      | %    | 4                  | Zone 0 and I  |

|                          |        |      |         | 25      | %    | 4                  | Zone 0 to II' |

| Uniformity between video | ΔSr    |      |         | 10      | %    | 5                  |               |

| signal channels          | ΔSb    |      |         | 10      | %    | 5                  |               |

| Dark signal              | Ydt    |      |         | 2       | mV   | 6                  | Ta = 60°C     |

| Dark signal shading      | ΔYdt   |      |         | 1       | mV   | 7                  | Ta = 60°C     |

| Flicker Y                | Fy     |      |         | 2       | %    | 8                  |               |

| Flicker R-Y              | Fcr    |      |         | 5       | %    | 8                  |               |

| Flicker B-Y              | Fcb    |      |         | 5       | %    | 8                  |               |

| Line crawl R             | Lcr    |      |         | 3       | %    | 9                  |               |

| Line crawl G             | Lcg    |      |         | 3       | %    | 9                  |               |

| Line crawl B             | Lcb    |      |         | 3       | %    | 9                  |               |

| Line crawl W             | Lcw    |      |         | 3       | %    | 9                  |               |

| Lag                      | Lag    |      |         | 0.5     | %    | 10                 |               |

#### Zone Definition of Video Signal Shading

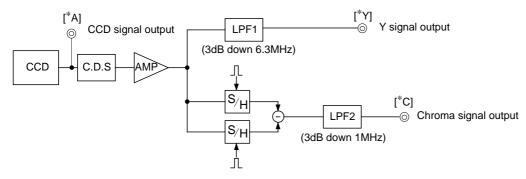

#### **Measurement System**

Note) Adjust the amplifier gain so that the gain between [\*A] and [\*Y], and between [\*A] and [\*C] equals 1.

#### Image Sensor Characteristics Measurement Method

#### **○** Measurement conditions

- 1) In the following measurements, the device drive conditions are at the typical values of the bias and clock voltage conditions. (when used with substrate bias external adjustment, set the substrate voltage to the value indicated on the device.)

- 2) In the following measurements, spot blemishes are excluded and, unless otherwise specified, the optical black level (OB) is used as the reference for the signal output, which is taken as the value of Y signal output or chroma signal output of the measurement system.

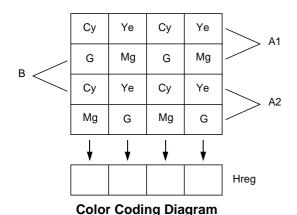

- © Color coding of this image sensor & Composition of luminance (Y) and chroma (color difference) signals

As shown in the left figure, fields are read out. The charge is mixed by pairs such as A1 and A2 in the A field. (pairs such as B in the B field)

As a result, the sequence of charges output as signals from the horizontal shift register (Hreg) is, for line A1, (G + Cy), (Mg + Ye), (G + Cy), and (Mg + Ye).

These signals are processed to form the Y signal and chroma (color difference) signal. The Y signal is formed by adding adjacent signals, and the chroma signal is formed by subtracting adjacent signals. In other words, the approximation:

$$Y = {(G + Cy) + (Mg + Ye)} x 1/2$$

is used for the Y signal, and the approximation:

$$R - Y = \{(Mg + Ye) - (G + Cy)\}$$

is used for the chroma (color difference) signal. For line A2, the signals output from Hreg in sequence are (Mg + Cy), (G + Ye), (Mg + Cy), (G + Ye).

The Y signal is formed from these signals as follows:

$$f = \{(G + Ye) + (Mg + Cy)\} \times 1/2$$

= 1/2 {2B + 3G + 2R}

This is balanced since it is formed in the same way as for line A1.

In a like manner, the chroma (color difference) signal is approximated as follows:

$$-(B - Y) = {(G + Ye) - (Mg + Cy)}$$

= - {2B - G}

In other words, the chroma signal can be retrieved according to the sequence of lines from R - Y and -(B - Y) in alternation. This is also true for the B field.

#### ◎ Definition of standard imaging conditions

1) Standard imaging condition I:

Use a pattern box (luminance 706cd/m<sup>2</sup>, color temperature of 3200K halogen source) as a subject. (Pattern for evaluation is not applicable.) Use a testing standard lens with CM500S (t = 1.0mm) as an IR cut filter and image at F5.6. The luminous intensity to the sensor receiving surface at this point is defined as the standard sensitivity testing luminous intensity.

2) Standard imaging condition II:

Image a light source (color temperature of 3200K) with a uniformity of brightness within 2% at all angles. Use a testing standard lens with CM500S (t = 1.0mm) as an IR cut filter. The luminous intensity is adjusted to the value indicated in each testing item by the lens diaphragm.

#### 1. Sensitivity

Set to standard imaging condition I. After selecting the electronic shutter mode with a shutter speed of 1/250s, measure the Y signal (Ys) at the center of the screen and substitute the value into the following formula.

$$S = Ys \times \frac{250}{60} [mV]$$

2. Saturation signal

Set to standard imaging condition II. After adjusting the luminous intensity to 10 times the intensity with average value of the Y signal output, 200mV, measure the minimum value of the Y signal.

3. Smear

Set to standard imaging condition II. With the lens diaphragm at F5.6 to F8, adjust the luminous intensity to 500 times the intensity with average value of the Y signal output, 200mV. When the readout clock is stopped and the charge drain is executed by the electronic shutter at the respective H blankings, measure the maximum value YSm [mV] of the Y signal output and substitute the value into the following formula.

Sm =  $\frac{YSm}{200}$  x  $\frac{1}{500}$  x  $\frac{1}{10}$  x 100 [%] (1/10V method conversion value)

4. Video signal shading

Set to standard imaging condition II. With the lens diaphragm at F5.6 to F8, adjust the luminous intensity so that the average value of the Y signal output is 200mV. Then measure the maximum (Ymax [mV]) and minimum (Ymin [mV]) values of the Y signal and substitute the values into the following formula.

SHy = (Ymax – Ymin)/200 x 100 [%]

5. Uniformity between video signal channels

Set to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200mV, and then measure the maximum (Crmax, Cbmax [mV]) and minimum (Crmin, Cbmin [mV]) values of the R – Y and B – Y channels of the chroma signal and substitute the values into the following formula.

$\Delta$ Sr = | (Crmax - Crmin)/200 | x 100 [%]  $\Delta$ Sb = | (Cbmax - Cbmin)/200 | x 100 [%]

6. Dark signal

Measure the average value of the Y signal output (Ydt [mV]) with the device ambient temperature 60°C and the device in the light-obstructed state, using the horizontal idle transfer level as a reference.

#### 7. Dark signal shading

After measuring 6, measure the maximum (Ydmax [mV]) and minimum (Ydmin [mV]) values of the dark signal output and substitute the values into the following formula.

$\Delta$ Ydt = Ydmax – Ydmin [mV]

8. Flicker

1) Fy

Set to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200mV, and then measure the difference in the signal level between fields ( $\Delta$ Yf [mV]). Then substitute the value into the following formula.

Fy = ( $\Delta$ Yf/200) x 100 [%]

2) Fcr, Fcb

Set to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200mV, insert an R or B filter, and then measure both the difference in the signal level between fields of the chroma signal ( $\Delta$ Cr,  $\Delta$ Cb) as well as the average value of the chroma signal output (CAr, CAb). Substitute the values into the following formula.

$Fci = (\Delta Ci/CAi) \times 100 [\%] (i = r, b)$

9. Line crawls

Set to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200mV, and then insert a white subject and R, G, and B filters and measure the difference between Y signal lines for the same field ( $\Delta$ YIw,  $\Delta$ YIr,  $\Delta$ YIg,  $\Delta$ YIb [mV]). Substitute the values into the following formula.

Lci =  $(\Delta Y li/200) \times 100 [\%]$  (i = w, r, g, b)

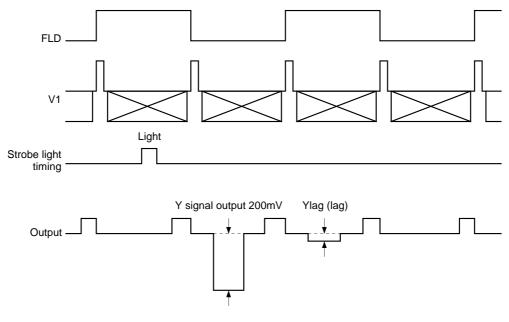

#### 10. Lag

Adjust the Y signal output value generated by strobe light to 200mV. After setting the strobe light so that it strobes with the following timing, measure the residual signal (Ylag). Substitute the value into the following formula.

Lag = (Ylag/200) x 100 [%]

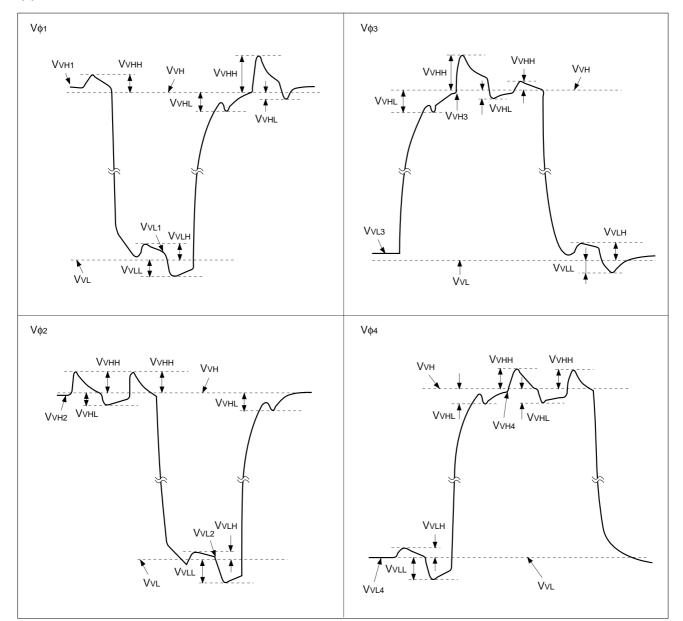

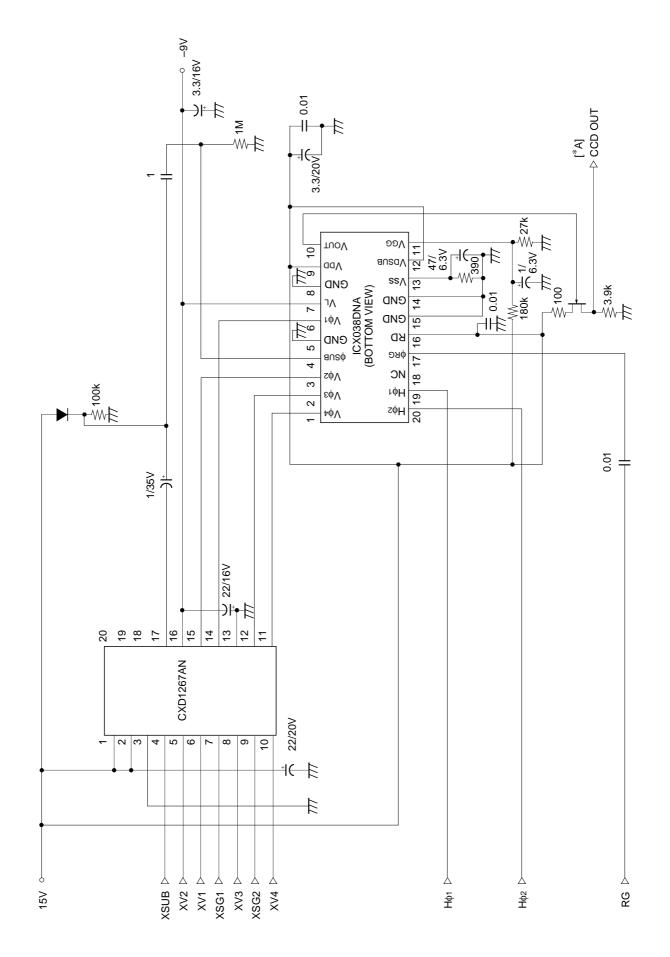

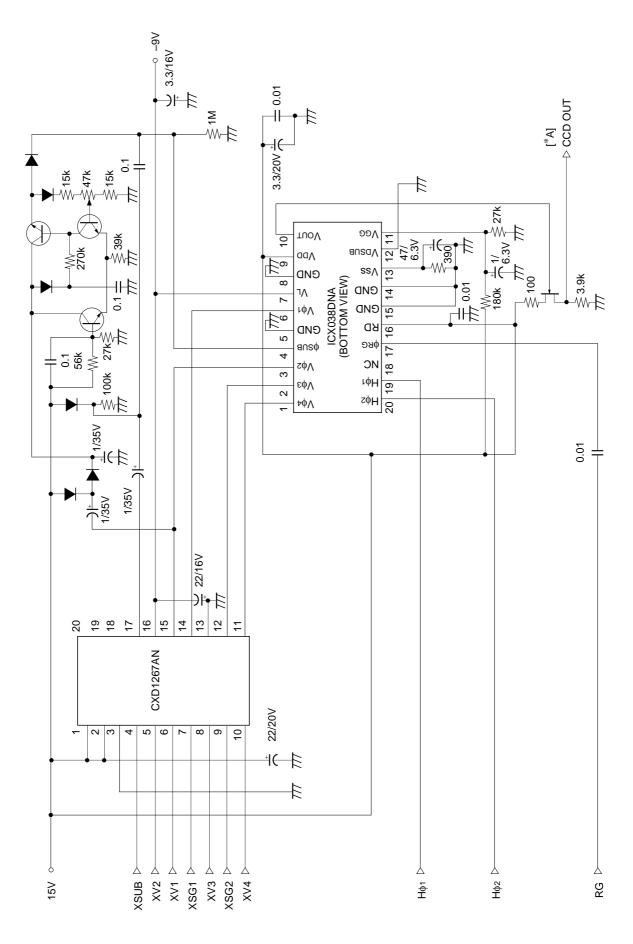

Drive Circuit 1 (substrate bias internal generation mode)

#### Spectral Sensitivity Characteristics (Excludes lens characteristics and light source characteristics)

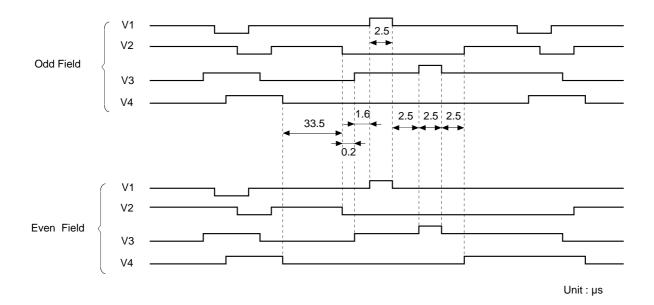

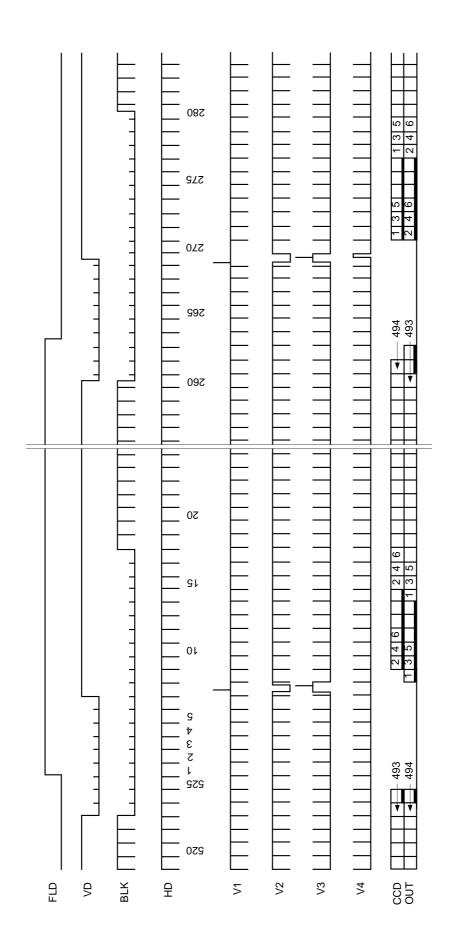

#### Sensor Readout Clock Timing Chart

#### Notes on Handling

1) Static charge prevention

CCD image sensors are easily damaged by static discharge. Before handling be sure to take the following protective measures.

- a) Either handle bare handed or use non-chargeable gloves, clothes or material. Also use conductive shoes.

- b) When handling directly use an earth band.

- c) Install a conductive mat on the floor or working table to prevent the generation of static electricity.

- d) Ionized air is recommended for discharge when handling CCD image sensors.

- e) For the shipment of mounted substrates, use boxes treated for the prevention of static charges.

- 2) Soldering

- a) Make sure the package temperature does not exceed 80°C.

- b) Solder dipping in a mounting furnace causes damage to the glass and other defects. Use a grounded 30W soldering iron and solder each pin in less than 2 seconds. For repairs and remount, cool sufficiently.

- c) To dismount an image sensor, do not use solder suction equipment. When using an electric desoldering tool, use a thermal controller of the zero cross On/Off type and connect it to ground.

- 3) Dust and dirt protection

Image sensors are packed and delivered by taking care of protecting its glass plates from harmful dust and dirt. Clean glass plates with the following operation as required, and use them.

- a) Operate in clean environments (around class 1000 is appropriate).

- b) Do not either touch glass plates by hand or have any object come in contact with glass surfaces. Should dirt stick to a glass surface, blow it off with an air blower. (For dirt stuck through static electricity ionized air is recommended.)

- c) Clean with a cotton bud and ethyl alcohol if grease stained. Be careful not to scratch the glass.

- d) Keep in a case to protect from dust and dirt. To prevent dew condensation, preheat or precool when moving to a room with great temperature differences.

- e) When protective tape is applied before shipping, just before use remove the tape applied for electrostatic protection. Do not reuse the tape.

- 4) Do not expose to strong light (sun rays) for long periods; color filters will be discolored. For continuous using under cruel condition exceeding the normal using condition, consult our company.

- 5) Exposure to high temperature or high humidity will affect the characteristics. Accordingly avoid storage or usage in such conditions.

- 6) CCD image sensors are precise optical equipment that should not be subject to too much mechanical shocks.

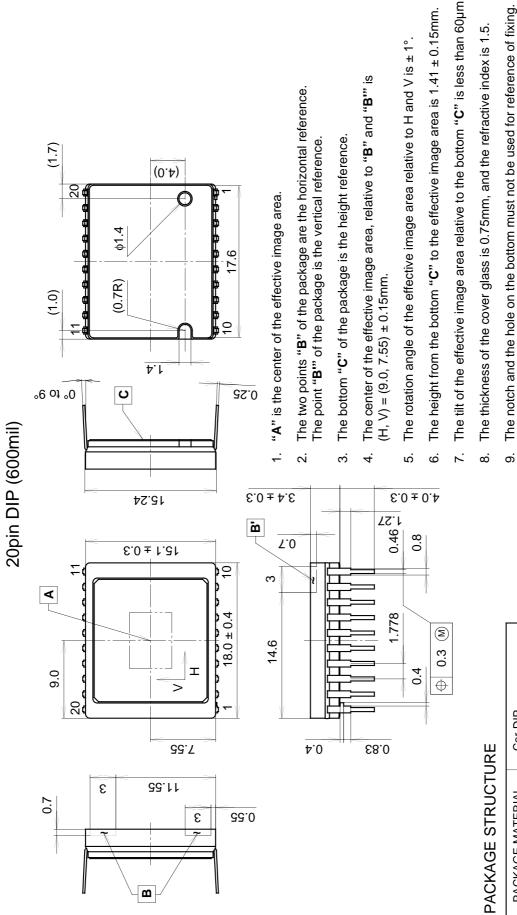

| Cer-DIP          | TIN PLATING    | 42 ALLOY      | 2.6g           |  |

|------------------|----------------|---------------|----------------|--|

| PACKAGE MATERIAL | LEAD TREATMENT | LEAD MATERIAL | PACKAGE WEIGHT |  |

Unit: mm

Package Outline