immos "

**Product data**

# IMS C012 link adaptor

.inmos. IMS and occam are trade marks of the INMOS Group of Companies.

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however no responsibility is assumed for its use, nor for any infringements of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of the INMOS Group of Companies.

Copyright INMOS Limited, 1986

| 1 | Over  | view IMS C012                            | 145 |

|---|-------|------------------------------------------|-----|

| 2 | The I | NMOS serial link interface               | 146 |

| 3 | Func  | tional description                       | 147 |

| 4 | C012  | Physical parameters                      | 149 |

|   | 4.1   | Absolute maximum ratings                 | 149 |

|   | 4.2   | Recommended operating conditions         | 149 |

|   | 4.3   | DC characteristics                       | 150 |

|   | 4.4   | Measurement of AC characteristics        | 150 |

|   | 4.5   | Connection of INMOS serial links         | 151 |

|   | 4.6   | AC characteristics of system services    | 153 |

|   | 4.7   | AC characteristics of parallel interface | 155 |

| 5 | Signa | al summary and package                   | 157 |

The IMS C012 link adaptor is a universal high speed system interconnect, providing full duplex communication according to the INMOS serial link protocol. The link protocol provides synchronised message transmission using handshaken byte streams. Data reception is asynchronous, allowing communication to be independent of clock phase.

The IMS C012 converts the bidirectional serial link data into parallel data streams. It can be used to freely interconnect transputers, INMOS peripheral controllers, I/O subsystems, and microprocessors of different families.

This manual details the product specific aspects of the IMS C012 and contains data relevant to the engineering and programming of the device.

Other information relevant to all transputer products is contained in the occam programming manual (supplied with INMOS software products and available as a separate publication), and the transputer development system manual (supplied with the development system).

This edition of the manual is dated October 27, 1986.

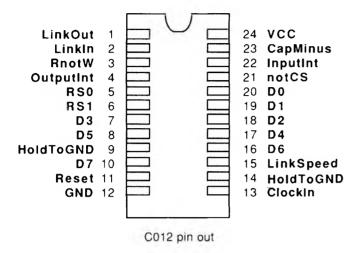

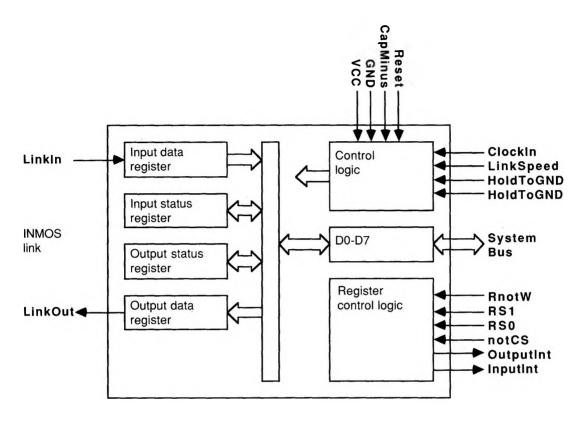

#### C012 Block Diagram

The C012 link adaptor provides an interface between an INMOS serial link and a microprocessor system bus, via an 8-bit bi-directional interface.

The device provides status/control and data registers for both input and output. Any of these can be accessed by the byte wide interface at any time. Two interrupt lines are provided, each gated by an interrupt enable flag. One presents an interrupt on output ready, and the other on data present.

The IMS C012 converts the bidirectional serial link data into parallel data streams. It can be used to fully interconnect transputers, INMOS peripheral controllers, I/O subsystems, and microprocessors of different families.

#### **Standard Clock Input**

The INMOS serial links are standard across all products in the transputer product range. All transputers will support a standard communications frequency of 10 Mbits/sec, regardless of processor performance. Thus transputers of different performance can be connected directly and future transputer systems will be able to communicate directly with those of today.

Each link consists of a serial input and a serial output, both of which are used to carry data and link control information.

#### Link protocol

| Data  |        | 0 | 1 | 2 | 3 | 4 | 5 | 6  | 7 |   |

|-------|--------|---|---|---|---|---|---|----|---|---|

| 1     | 1      |   |   | 1 | 1 |   | 1 | 1_ |   | 0 |

| Ackno | wledge | e |   |   |   |   |   |    |   |   |

| 1     | 0      |   |   |   |   |   |   |    |   |   |

A message is transmitted as a sequence of bytes. After transmitting a data byte, the sender waits until an acknowledge has been received, signifying that the receiver is ready to receive another byte. The receiver can transmit an acknowledge as soon as it starts to receive a data byte, so that transmission can be continuous. This protocol provides handshaken communication of each byte of data, ensuring that slow and fast transputers communicate reliably.

When there is no activity on the links they remain at logic 0, **GND** potential.

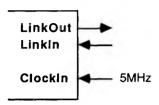

A 5 MHz input clock is used, from which internal timings are generated. Link communication is not sensitive to clock phase. Thus, communication can be achieved between independently clocked systems as long as the communications frequency is within the specified tolerance.

The IMS C012 link adaptor is controlled at the parallel interface by reading and writing status/control registers, and by reading and writing data registers. Two interrupt lines are provided. One indicates that the link adaptor is ready to output a byte to the link, and the other indicates that it is holding a byte which it has read from the link

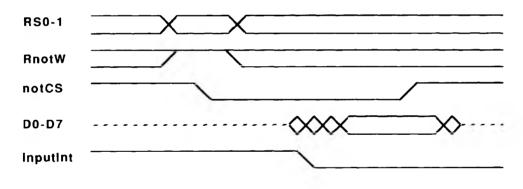

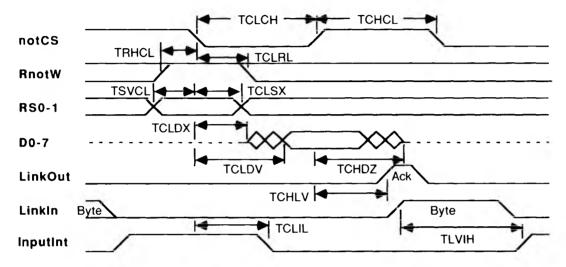

#### Parallel Interface

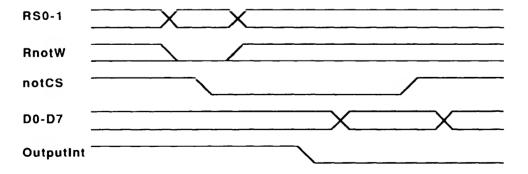

One of the four registers is selected by **RS0** and **RS1**. If a new value is to be written into the selected registers, it is set up on **D0-D7** and **RnotW** is taken low. **notCS** is then taken low. On read cycles, the current value of the selected register is placed on **D0-D7**.

| RS1 | RS0 | RnotW | Function                              |

|-----|-----|-------|---------------------------------------|

| 0   | 0   | 1     | D0-D7 := input data register          |

| 0   | 1   | 0     | output data register := <b>D0-D7</b>  |

| 1   | 0   | 1     | D0-D7 := input status register        |

| 1   | 0   | 0     | input status register := <b>D0-D7</b> |

| 1   | 1   | 1     | D0-D7 := output status register       |

| 1   | 1   | 0     | output status register := D0-D7       |

**Note**: Writing to the input data register has no effect and reading the output data register will result in undefined data on the data bus. Unused bit positions must be set to zero in both the input status register and the output status register.

#### Read register timing diagram

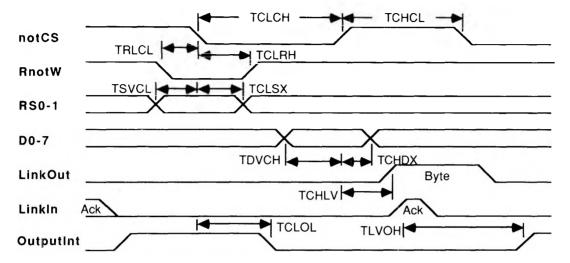

#### Write register timing diagram

#### **Output to link**

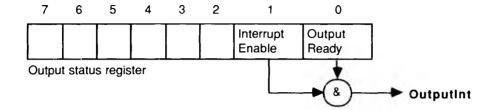

The output ready status bit indicates that the serial link is ready to send a byte of data. The bit is set high on reset, and when the link adaptor receives an acknowledgement from the serial link. It is reset low when a data byte is written to the output data register on the parallel interface. **OutputInt** is set high if both output ready and interrupt enable are set high. Output interrupt enable is set low on reset.

#### Input from link

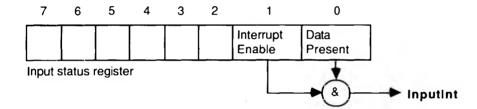

The data present status bit indicates that the serial link has received a byte of data. The bit is reset low when the data byte is read from the input data register on the parallel interface, this causes an acknowledgement to be transmitted on the serial link. **InputInt** is set high if both data present and interrupt enable are set high. Input interrupt enable and **data present** are both set low on reset.

Note: Parameters given in this section will be revised as a result of further characterization.

## 4.1 Absolute maximum ratings

| Parame       | Parameter                               |      | Max             | Unit           | Note    |

|--------------|-----------------------------------------|------|-----------------|----------------|---------|

| VCC<br>VI,VO | DC supply voltage<br>Input or output    | 0    | 7.0             | V              | 1, 2, 3 |

| OSCT         | voltage on any pin Output short circuit | -0.5 | <b>VCC</b> +0.5 | V              | 1, 2, 3 |

|              | time (one pin)                          |      | 1               | S              | 1       |

| TS<br>TA     | Storage temperature Ambient temperature | -65  | 150             | $^{\circ}C$    | 1       |

| PD           | under bias<br>Power dissipation rating  | -55  | 125<br>600      | $^{\circ}C$ mW | 1       |

#### **Notes**

- Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2 All voltages are with respect to **GND**.

- This device contains circuitry to protect the inputs against damage caused by high static voltages or electric fields; however it is advised that normal precautions be taken to avoid application of any voltage higher than the absolute maximum rated voltages to this high impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level such as **GND**.

#### 4.2 Recommended operating conditions

| Parameter    |                                              | Min      | Max               | Unit          | Note     |

|--------------|----------------------------------------------|----------|-------------------|---------------|----------|

| VCC<br>VI,VO | DC supply voltage<br>Input or output voltage | 4.5<br>0 | 5.5<br><b>VCC</b> | V<br>V        | 1<br>1,2 |

| CL           | Load capacitance on any pin                  |          | 50                | рF            |          |

| TA           | Operating temperature range                  | 0        | 70                | ${}^{\circ}C$ |          |

#### **Notes**

- 1 All voltages are with respect to **GND**.

- 2 Excursions beyond the supplies are permitted but not recommended; see DC characteristics.

#### 4.3 DC characteristics

#### 4.3 **DC** characteristics

| Param                                 | neter                                                                                                                                                                                                                         | Conditions                                                                                             | Min                          | Max                                                     | Unit                                                   |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------|--------------------------------------------------------|--|

| VIH VIL II VOH VOL IOS IOZ PD CIN COZ | High level input voltage Low level input voltage Input current Output high voltage Output low voltage Output short circuit current Tristate output current Power dissipation Input capacitance Output capacitance in tristate | GND < VI< VCC<br>IOH = -2mA<br>IOL = 4mA<br>GND < VO < VCC<br>GND < VI < VCC<br>f = 1 MHz<br>f = 1 MHz | 2.0<br>-0.5<br><b>VCC</b> -1 | VCC+0.5<br>0.8<br>±200<br>0.4<br>50<br>±200<br>100<br>7 | V<br>V<br>μ A<br>V<br>V<br>mA<br>μ A<br>mW<br>pF<br>pF |  |

Note: 4.5 V < VCC < 5.5 V  $0 \,^{\circ}C < \text{TA} < 70 \,^{\circ}C$

Input clock frequency = 5 MHz All voltages are with respect to GND

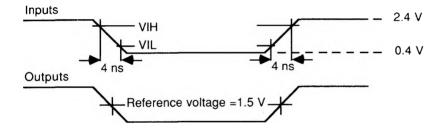

#### 4.4 Measurement of AC characteristics

## Reference points for AC characteristics

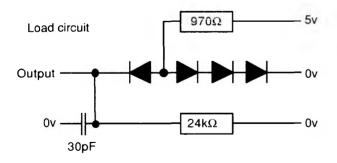

#### Load circuit for AC measurements

The load circuit approximates to two TTL loads, with a total capacitance of 30 pF.

#### 4.5 Connection of INMOS serial links

#### 4.5 Connection of INMOS serial links

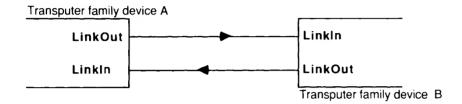

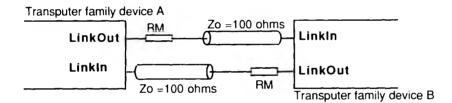

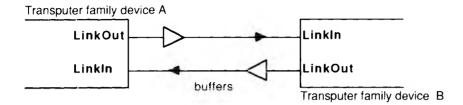

INMOS serial links can be connected in 3 different ways depending on their environment:

- 1 Directly connected

- 2 Connected via a series matching resistor

- 3 Connected via buffers

#### **Direct connection**

Direct connection is suitable for short distances on a printed circuit board.

#### Matched line

For long wires, approximately >30 cm, then a 100ohm transmission line should be used with series matching resistors.

| Parameter |                                            | Nom | Max | Unit     |

|-----------|--------------------------------------------|-----|-----|----------|

| RM        | Series matching resistor for 100 ohm line. | 47  |     | ohm      |

| TD        | Delay down line                            |     | 0.4 | bit time |

Note that if two connected devices have different values for **TD**, the lower value should be used. With series termination at **LinkOut** the transmission line reflection must return within 1 Bit time. Otherwise line buffers should be used.

#### **Buffered links**

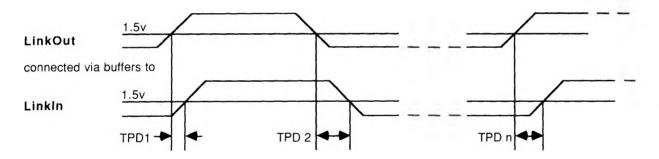

If buffers are used their overall propagation delay, TPD, should be stable within the skew tolerance.

| Parameter                                                              | Max | Unit     |

|------------------------------------------------------------------------|-----|----------|

|                                                                        | 30  | ns       |

| Skew in buffering at 10 Mbits/sec<br>Skew in buffering at 20 Mbits/sec | 10  | ns<br>ns |

| Rise and fall time of <b>LinkIn</b> (10% to 90%)                       | 20  | ns       |

The above figures indicate that buffered links can be realised at 10Mbits/sec. For the case of 20 Mbits/sec, the maximum value can only be specified as a result of further characterisation.

The absolute value of TPD is immaterial because data reception is asynchronous. However, TPD will vary from moment to moment because of ground noise, variation in the power supplies of buffers and the difference in the delay for rising and falling edges. This will vary the length of data bits reaching **LinkIn**. *Skew* is the difference between the maximum and minimum instantaneous values of TPD.

## 4.6 AC characteristics of system services

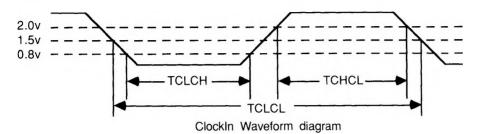

#### ClockIn waveform

| Parameter |                                                                                 | Min | Nom | Max | Unit          | Note |

|-----------|---------------------------------------------------------------------------------|-----|-----|-----|---------------|------|

| TCHCL     | Clock pulse width high                                                          | 40  |     |     | ns            | 1    |

| TCLCH     | Clock pulse width low                                                           | 40  |     |     | ns            | 1    |

|           | Rise and fall time of ClockIn (10% to 90%)                                      |     |     | 10  | ns            | 1    |

| TCLCL     | Clock period                                                                    |     | 200 | 400 | ns            | 2    |

|           | Difference in frequencies of <b>ClockIn</b> for two devices connected by a link |     |     | 400 | ppm           | 4    |

| TRHRL     | Reset pulse width high                                                          | 8   |     |     | Clockin       | 3    |

|           | Time <b>VCC</b> and <b>ClockIn</b> valid before reset is taken low              |     | 10  |     | periods<br>ms | 3,5  |

## **Notes**

- 1 The clock transitions must be monotonic within the range between VIH and VIL.

- 2 The **TCLCL** parameter is measured between corresponding points on consecutive falling edges.

- 3 During reset, LinkIn should be held low. Note that reset forces LinkOut to be low.

- 4 This value allows the use of low cost 200ppm crystal oscillators.

- 5 When powering up.

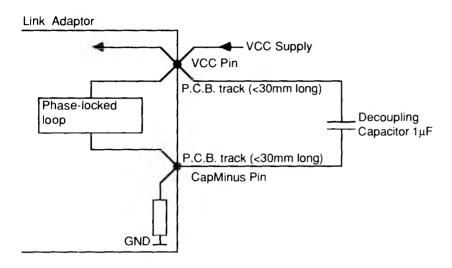

#### Recommended PLL decoupling

#### **Notes**

| Parameter |                                                                        | Min | Nom | Max | Unit | Note |

|-----------|------------------------------------------------------------------------|-----|-----|-----|------|------|

| С         | Decoupling capacitor                                                   | 1   |     |     | μF   | 1    |

|           | A.C. noise between VCC and GND                                         |     |     | 200 | mV   | 2,3  |

|           | A.C. noise between <b>VCC</b> and ground reference of load capacitance |     |     | 200 | mV   | 4    |

- The decoupling capacitor should be a high-quality tantalum (or other) type, with low series resistance (<1 ohm), and low impedance at high frequency (<10 ohm at 100 MHz). It should be connected between VCC and CapMinus, with short tracks, and with a star point at the VCC pin, as shown.

- Requires a  $0.1\mu$ F. capacitor between VCC and GND, close to the chip.

- 3 Peak to peak at all frequencies above 100 KHz.

- 4 Peak to peak at all frequencies above 30 MHz.

# 4.7 AC characteristics of parallel interface

## 4.7 AC characteristics of parallel interface

## AC characteristics of parallel interface

# Read cycle

| Parameter    |                              | Min | Max  | Unit     |

|--------------|------------------------------|-----|------|----------|

| TCLCH        | notCS low time               | 50  |      | ns       |

| TCHCL        | time between cycles          | 50  |      | ns       |

| TRHCL        | RnotW setup                  | 5   |      | ns       |

| TCLRL        | RnotW hold                   | 5   |      | ns       |

| <b>TSVCL</b> | Register select setup        | 5   |      | ns       |

| TCLSX        | Register select hold         | 5   |      | ns       |

| TCLDX        | notCS to output active       | 5   |      | ns       |

| TCLDV        | notCS to output valid        |     | 40   | ns       |

| <b>TCLDZ</b> | notCS high to output invalid | 0   | 25   | ns       |

| TCHLV        | notCS high to Ack on link    |     |      |          |

|              | (no byte on link)            | 0.8 | 1.8  | bit time |

|              | (byte on link)               | 0.8 | 12.8 | bit time |

| TCLIL        | notCS low to InputInt low    |     | 25   | ns       |

| TLVIL        | Byte to InputInt high        |     | 12   | bit time |

# Write cycle

| Parameter |                            |     | Max | Unit     |  |  |

|-----------|----------------------------|-----|-----|----------|--|--|

| TCLCH     | notCS low time             | 50  |     | ns       |  |  |

| TCHCL     | time between cycles        | 50  |     | ns       |  |  |

| TRLCL     | RnotW setup                | 5   |     | ns       |  |  |

| TCLRH     | RnotW hold                 | 5   |     | ns       |  |  |

| TSVCL     | Register select setup      | 5   |     | ns       |  |  |

| TCLSX     | Register select hold       | 5   |     | ns       |  |  |

| TDVCH     | Data setup                 | 15  |     | ns       |  |  |

| TCHDX     | Data hold                  | 5   |     | ns       |  |  |

| TCHLV     | notCS high to byte on link |     |     |          |  |  |

|           | (no Ack on link)           | 8.0 | 1.8 | bit time |  |  |

|           | (Ack on link)              | 8.0 | 3.8 | bit time |  |  |

| TCLOL     | notCS low to OutputInt low |     | 25  | ns       |  |  |

| TLVOH     | Ack to OutputInt high      |     | 3   | bit time |  |  |

CapMinus Negative end of decoupling capacitor.

Clockin 5MHz input clock.

Input

**D0-D7** Bi-directional databus.

Input/Output

GND Ground.

HoldToGND Signal reserved for INMOS use. Must be held to GND. Failure to do so may cause

damage to the device.

Input

**Inputint** Input interrupt.

Output

**LinkIn** INMOS serial link input.

Input

**LinkOut** INMOS serial link output.

Output

LinkSpeed Determines the speed of the links. If wired to GND link speed is 10 Mbits/sec, if wired

to VCC speed is 20 Mbits/sec.

Input

**notCS** Chip select input.

Input

Output interrupt.

Output

Reset link adaptor.

Input

**RnotW** Read or write register.

Input

RS0-RS1 Register select lines; used in conjunction with notCS and RnotW to control the

selection of the internal register to be read or written.

Input

VCC Star point for +5 volt supply input and positive end of decoupling capacitor.

The C012 is available in a 24 pin plastic package.