No.999C

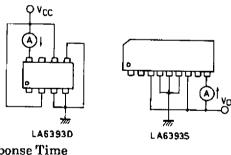

## LA6393D, 6393S

## High-Performance Dual Comparator

The LA6393D,6393S are high-performance dual comparators that are capable of operating from a single power supply voltage over a wide range 2 to 36V.

Because of their excellent input characteristics and low power, they can be very conveniently applied to multisignal parallel comparator circuits that require high-density assembly.

#### **Features**

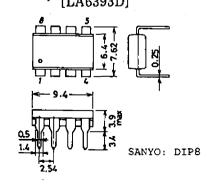

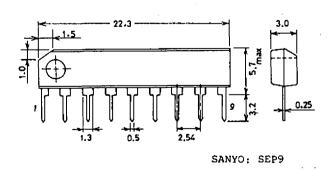

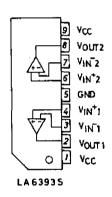

- · LA6393D: DIP-8 pin package, LA6393S: SEP-9 pin package

- · Wide operating power-supply voltage range

- (Single power supply: 2.0 to 36.0V, dual power supplies:  $\pm 1.0$  to  $\pm 18.0$ V)

- Wide common-mode input voltage range (0 to V<sub>CC</sub>-1.5V)

- · Open-collector output enabling wired OR

- · Small current dissipation (0.6mA) and low power.

| Maximum Ratings at Ta = 25°C    |                 |                | unit                 |

|---------------------------------|-----------------|----------------|----------------------|

| Maximum Supply Voltage          | $ m V_{CC}$ max | 36             | V                    |

| Differential Input Voltage      | $V_{ID}$        | 36             | V                    |

| Common-Mode Input Voltage Range | $V_{ICM}$       | -0.3  to  +36  | V                    |

| Allowable Power Dissipation     | Pd max          | 570            | mW                   |

| Operating Temperature           | Topr            | -30  to  +85   | $^{\circ}\mathrm{C}$ |

| Storage Temperature             | Tstg            | -55  to  + 125 | $^{\circ}\mathrm{C}$ |

| )perating Characteristic | esatTa=2         | 5°C, V <sub>CC</sub> =5 V  | Test    |     |                  |             |      |

|--------------------------|------------------|----------------------------|---------|-----|------------------|-------------|------|

|                          |                  |                            | Circuit | min | typ              | max         | unit |

| Input Offset Voltage     | $V_{IO}$         |                            | 1       |     | ±1               | $\pm 5$     | mV   |

| Input Offset Current     | $I_{IO}$         |                            | 2       |     | $\pm 5$          | $\pm 50$    | nA   |

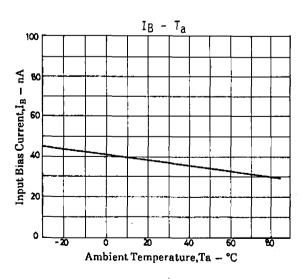

| Input Bias Current       | $I_{\mathbf{B}}$ |                            | 3       |     | 25               | <b>2</b> 50 | nΑ   |

| Common-Mode Input        | $V_{ICM}$        |                            | ,       | 0   | $V_{\mathbf{C}}$ | c - 1.5     | V    |

| Voltage Range            |                  |                            |         |     |                  |             |      |

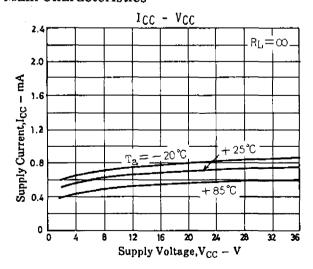

| Supply Current           | $I_{CC}$         | $R_L = \infty$             | 4       |     | 0.6              | 1           | mΑ   |

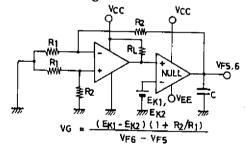

| Voltage Gain             | VG               | $R_L = 15k\Omega$          | 5       |     | 200              | ,           | V/mV |

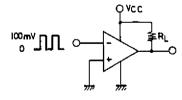

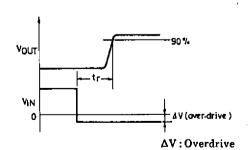

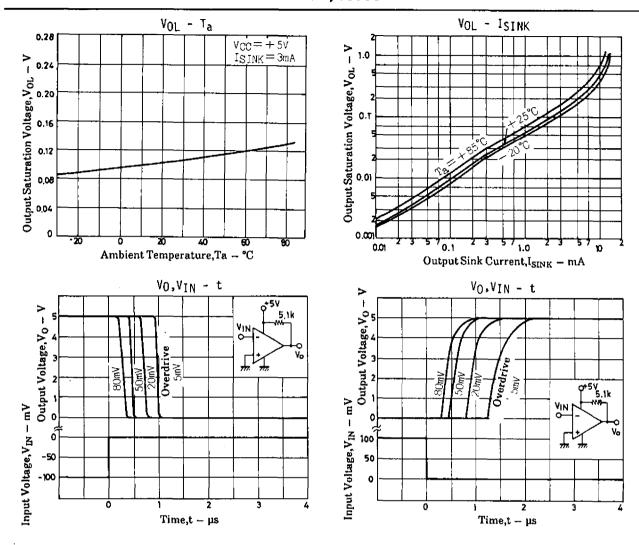

| Response Time            |                  | $V_{RL}=5V,R_L=5.1k\Omega$ | 6       |     | 1.3              |             | μs   |

|                          |                  |                            |         |     |                  |             |      |

Continued on next page.

# Package Dimensions 30018 (unit: mm) [LA6393D]

## $\begin{array}{ll} \textbf{Package Dimensions} & \textbf{3017B} \\ \textbf{(unit: mm)} & [LA6393S] \end{array}$

| Continued from preceding pag | e.                |                                                     | Test    |     |     |     |      |

|------------------------------|-------------------|-----------------------------------------------------|---------|-----|-----|-----|------|

|                              |                   |                                                     | Circuit | min | typ | max | unit |

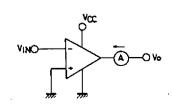

| Output Sink Current          | I <sub>SINK</sub> | $V_{IN} = 1V, V_{IN} + = 0V,$<br>$V_O \le 1.5V$     | 7       | 6   | 16  |     | mA   |

| Output Saturation Voltage    | $V_{OL}$          | $V_{IN} = 1V, V_{IN} + = 0V,$<br>$I_{SINK} \le 3mA$ | 8       |     | 0.2 | 0.4 | V    |

| Output Leakage Current       | I <sub>LEAK</sub> | $V_{IN} = 0V, V_{IN} + = 1V,$<br>$V_{O} = 5V$       | 9       |     | 0.1 |     | nΑ   |

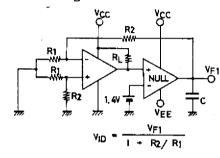

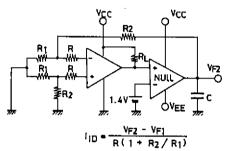

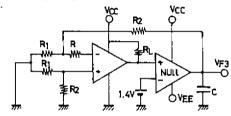

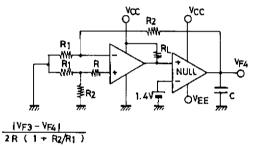

#### **Test Circuits**

#### 1. Input Offset Voltage

#### 2. Input Offset Current

#### 3. Input Bias Current

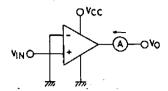

#### 4. Supply Current

#### 5. Voltage Gain

#### 6. Response Time

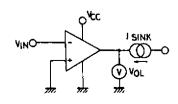

### 7. Output Sink Current

#### 8. Output Saturation Voltage

#### 9. Output Leakage Current

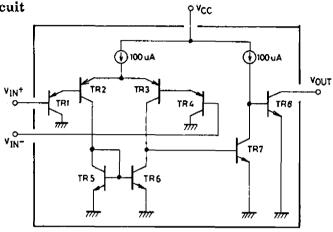

#### **Equivalent** Circuit

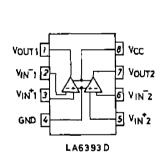

#### Pin Assignment

#### **Main Characteristics**

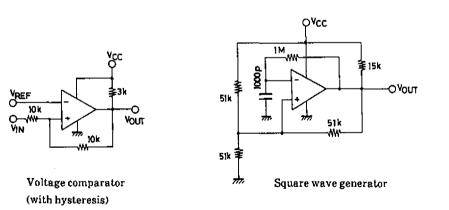

#### Sample Application Circuits

Unit (resistance:  $\Omega$ , capacitance: F)

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production, SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.