# **High-Speed CD-ROM Spindle Motor Driver IC**

#### Overview

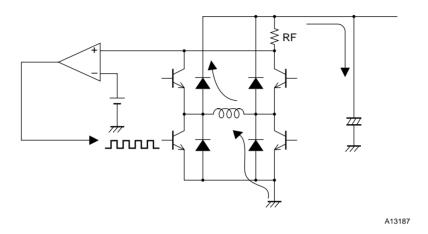

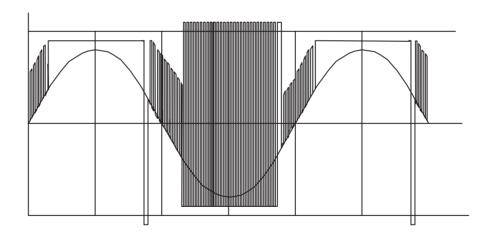

The LB11975 is a monolithic bipolar IC developed for uses as a spindle motor driver for high-speed CD-ROM and DVD-ROM drives. To minimize heat generation during high-speed rotation and braking, the LB11975 adopts direct PWM drive in the output stage. During reverse braking the upper and lower side output transistors are both driven in PWM mode to implement dual PWM controlled braking. The device thus controls the current to remain under a limit value and prevent rapid heat generation. This prevents device destruction due to rapid heating. The absolute maximum voltage rating is 27 V, and the maximum current is 2.5 A.

# **Functions and Features**

- Direct PWM drive (lower side control)

- Built-in upper and lower side output diodes

- Supports the use 3.3 V DSP devices.

- · Power saving function for standby mode

- Hall FG output (1 or 3 Hall device operation)

- · Built-in Hall device power supply

- · Reverse rotation detection output and drive cutoff circuit

- Voltage control amplifier

- Current limiter circuit

- Thermal protection circuit

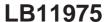

# **Package Dimensions**

unit: mm

#### 3251-HSOP36R

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

# **Specifications** Maximum Ratings at Ta = 25°C

| Parameter                     | Symbol                | Conditions                                                                        | Ratings     | Unit |

|-------------------------------|-----------------------|-----------------------------------------------------------------------------------|-------------|------|

| Supply voltage 1              | V <sub>CC</sub> 1 max |                                                                                   | 7           | V    |

| Supply voltage 2              | V <sub>CC</sub> 2 max |                                                                                   | 27          | V    |

| Supply voltage 3              | V <sub>CC</sub> 3 max |                                                                                   | 27          | V    |

| Output current                | I <sub>O</sub> max    |                                                                                   | 2.5         | А    |

| Output applied voltage        | V <sub>IN</sub> max   |                                                                                   | 30          | V    |

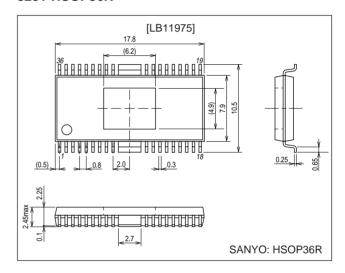

| Allowable power dissipation 1 | Pd max1               | Independent IC                                                                    | 0.9         | W    |

| Allowable power dissipation 2 | Pd max2               | Mounted on the specified circuit board (114.3 × 76.1 × 1.6 mm³ glass epoxy board) | 2.1         | W    |

| Operating temperature         | Topr                  |                                                                                   | -20 to +75  | °C   |

| Storage temperature           | Tstg                  |                                                                                   | -55 to +150 | °C   |

# Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter                    | Symbol            | Conditions                            | Ratings                | Unit |

|------------------------------|-------------------|---------------------------------------|------------------------|------|

| Power-supply voltage range 1 | V <sub>CC</sub> 1 |                                       | 4 to 6                 | V    |

| Power-supply voltage range 2 | V <sub>CC</sub> 2 | V <sub>CC</sub> 2 ≥ V <sub>CC</sub> 1 | 4 to 16                | V    |

| Power-supply voltage range 3 | V <sub>CC</sub> 3 |                                       | 4 to 16                | V    |

| FG pin applied voltage       | VFG               |                                       | 0 to V <sub>CC</sub> 1 | V    |

| FG pin output current        | IFG               |                                       | 0 to 4.0               | mA   |

# Electrical Characteristics at Ta = 25°C, $V_{CC}1$ = 5 V, $V_{CC}2$ = $V_S$ = 12 V

| 5                                     | 0 1 1                  | Conditions                                                                                             | Ratings |      |                       | Unit  |  |

|---------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------|---------|------|-----------------------|-------|--|

| Parameter                             | Symbol                 | Conditions                                                                                             |         | typ  | max                   | Offic |  |

| Complete support 4                    | I <sub>CC</sub> 1-1    | V <sub>CTL</sub> = V <sub>CREF</sub>                                                                   | 5.0     | 8.0  | 11.0                  | mA    |  |

| Supply current 1                      | I <sub>CC</sub> 1-2    | VS/S = 0 V                                                                                             |         | 0    | 200                   | μA    |  |

| Cumbic ourrent 2                      | I <sub>CC</sub> 2-1    | V <sub>CTL</sub> = V <sub>CREF</sub>                                                                   | 5.0     | 6.5  | 8.0                   | mA    |  |

| Supply current 2                      | I <sub>CC</sub> 2-2    | VS/S = 0 V                                                                                             |         | 0    | 200                   | μA    |  |

| Cumply ourrent 2                      | I <sub>CC</sub> 3-1    | V <sub>CTL</sub> = V <sub>CREF</sub>                                                                   |         | 0.3  | 0.7                   | mA    |  |

| Supply current 3                      | I <sub>CC</sub> 3-2    | VS/S = 0 V                                                                                             |         | 0    | 200                   | μA    |  |

| [Output Block]                        |                        |                                                                                                        |         |      |                       |       |  |

| Output acturation valtage 4           | V <sub>O</sub> sat1(L) | $I_{O} = 0.5 \text{ A}, V_{O}(\text{sink}), V_{CC}1 = 5 \text{ V}, V_{CC}2 = V_{CC}3 = 12 \text{ V}$   |         | 0.15 | 0.25                  | V     |  |

| Output saturation voltage 1           | V <sub>O</sub> sat1(H) | $I_{O} = 0.5 \text{ A}, V_{O}(\text{source}), V_{CC}1 = 5 \text{ V}, V_{CC}2 = V_{CC}3 = 12 \text{ V}$ |         | 0.80 | 0.95                  | V     |  |

| Output acturation valtage 2           | V <sub>O</sub> sat2(L) | $I_O = 1.5 \text{ A}, V_O(\text{sink}), V_{CC}1 = 5 \text{ V}, V_{CC}2 = V_{CC}3 = 12 \text{ V}$       |         | 0.40 | 0.60                  | V     |  |

| Output saturation voltage 2           | V <sub>O</sub> sat2(H) | $I_{O} = 1.5 \text{ A}, V_{O}(\text{source}), V_{CC}1 = 5 \text{ V}, V_{CC}2 = V_{CC}3 = 12 \text{ V}$ |         | 1.10 | 1.30                  | V     |  |

| Output leakage current                | I <sub>O</sub> leak(L) |                                                                                                        |         |      | 100                   | μA    |  |

| Output leakage current                | I <sub>O</sub> leak(H) |                                                                                                        | -100    |      |                       | μA    |  |

| Diode forward voltage                 | V <sub>F</sub> H       | Upper side diode, I <sub>O</sub> = 2.0 A                                                               |         | 1.50 | 2.00                  | V     |  |

| Diode forward voltage                 | V <sub>F</sub> L       | Lower side diode, I <sub>O</sub> = 2.0 A                                                               |         | 1.50 | 2.00                  | V     |  |

| [Hall Amplifier Block]                |                        |                                                                                                        |         |      |                       |       |  |

| Input bias current                    | I <sub>HB</sub>        |                                                                                                        | -4      | -1   |                       | μA    |  |

| Common-mode input voltage range       | V <sub>ICM</sub>       |                                                                                                        | 1.5     |      | V <sub>CC</sub> – 1.5 | V     |  |

| Hall input sensitivity                | $V_{HIN}$              |                                                                                                        | 60      |      |                       | mVp-p |  |

| Hysteresis                            | $\Delta V_{IN}(HA)$    |                                                                                                        | 23      | 32   | 39                    | mV    |  |

| Input voltage: low $\rightarrow$ high | V <sub>SL</sub> H      |                                                                                                        | 6       | 16   | 25                    | mV    |  |

| Input voltage: high $\rightarrow$ low | V <sub>SL</sub> L      |                                                                                                        | -25     | -16  | -6                    | mV    |  |

| [Thermal Protection Circuit]          |                        |                                                                                                        |         |      |                       |       |  |

| Operating temperature                 | T-TSD                  | Design target value (junction temperature) *                                                           | 150     | 180  | 210                   | °C    |  |

| Hysteresis                            | ΔTSD                   | Design target value (junction temperature) *                                                           |         | 40   |                       | °C    |  |

Note: \* These are design target values and are not tested.

Continued on next page.

# LB11975

Continued from preceding page.

| Parameter                        | Symbol                | Conditions                                        |       | Ratings |                   |       |

|----------------------------------|-----------------------|---------------------------------------------------|-------|---------|-------------------|-------|

| Parameter                        | Symbol                | Symbol                                            |       | typ     | max               | Unit  |

| [PWM Oscillator]                 |                       |                                                   |       |         |                   | •     |

| High-level output voltage        | V <sub>O</sub> H(OSC) |                                                   | 3.1   | 3.3     | 3.5               | V     |

| Low-level output voltage         | V <sub>O</sub> L(OSC) |                                                   | 1.4   | 1.6     | 1.8               | V     |

| Amplitude                        | V(OSC)                |                                                   | 1.5   | 1.7     | 1.9               | Vp-p  |

| Oscillator frequency             | f(OSC)                | C = 2200 pF                                       |       | 23.0    |                   | kHz   |

| Charge current                   | I <sub>CHG</sub>      |                                                   | -110  | -94     | -83               | μA    |

| Charge resistor value            | R <sub>DCHG</sub>     |                                                   | 1.6   | 2.1     | 2.6               | kΩ    |

| [CTL Amplifier]                  | '                     |                                                   |       |         |                   |       |

| VCTL pin input current           | I <sub>VCTL</sub>     | V <sub>CTL</sub> = V <sub>CREF</sub> = 1.65 V     | -2    |         |                   | μA    |

| VCREF pin input current          | I <sub>VCREF</sub>    | V <sub>CTL</sub> = V <sub>CREF</sub> = 1.65 V     | -2    |         |                   | μΑ    |

| Forward rotation gain            | GDF <sup>+</sup>      | Design target value *                             | 0.20  | 0.25    | 0.30              | times |

| Reverse rotation gain            | GDF <sup>-</sup>      | Design target value *                             | -0.30 | -0.25   | -0.20             | times |

| Forward rotation limiter voltage | V <sub>RF</sub> 1     |                                                   | 0.26  | 0.29    | 0.32              | V     |

| Reverse rotation limiter voltage | V <sub>RF</sub> 2     |                                                   | 0.26  | 0.29    | 0.32              | V     |

| Startup voltage                  | V <sub>CTH</sub>      | V <sub>CREF</sub> = 1.65 V. Design target value * | 1.50  |         | 1.80              | V     |

| Dead zone                        | V <sub>DZ</sub>       | V <sub>CREF</sub> = 1.65 V. Design target value * | 35    | 80      | 140               | mV    |

| [FG Pin] (speed pulse output)    | '                     |                                                   |       |         |                   |       |

| Low-level output voltage         | V <sub>FGL</sub>      | I <sub>FG</sub> = 2 mA                            |       |         | 0.4               | V     |

| Pull-up resistor value           | R <sub>FG</sub>       |                                                   | 7.5   | 10      | 12.5              | kΩ    |

| [RS Pin]                         | '                     |                                                   |       |         |                   |       |

| Low-level output voltage         | V <sub>RSL</sub>      | I <sub>RS</sub> = 2 mA                            |       |         | 0.4               | V     |

| Pull-up resistor value           | R <sub>RS</sub>       |                                                   | 7.5   | 10      | 12.5              | kΩ    |

| [Stop/Start Pin]                 | '                     |                                                   | ,     |         |                   |       |

| Low-level input voltage          | V <sub>SS</sub> L     |                                                   |       | 0       | 0.7               | V     |

| High-level input voltage         | V <sub>SS</sub> H     |                                                   | 2.0   |         | V <sub>CC</sub> 1 | V     |

| Low-level input current          | I <sub>SS</sub> L     | V <sub>SS</sub> = 0 V                             | -1    | 0       |                   | μA    |

| High-level input current         | I <sub>SS</sub> H     | V <sub>SS</sub> = 5.0 V                           |       | 50      | 200               | μA    |

| [Hall Device Power Supply]       |                       |                                                   | '     |         |                   | •     |

| Hall device supply voltage       | V <sub>H</sub>        | I <sub>H</sub> = 5 mA                             | 0.65  | 0.85    | 1.05              | V     |

| Allowable current                | I <sub>H</sub>        |                                                   |       |         | 20                | mA    |

Note: \* These are design target values and are not tested.

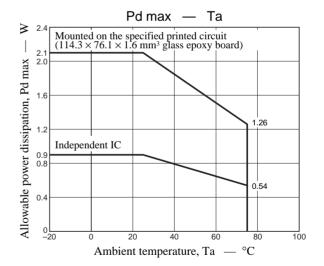

# **Truth Table**

|   | Input |       |     | Control voltage V <sub>CTL</sub> | Output        | FG o | utput |

|---|-------|-------|-----|----------------------------------|---------------|------|-------|

|   | IN1   | IN2   | IN3 |                                  | Source → Sink | FG1  | FG2   |

| 1 | HL    |       | н   | Н                                | OUT2 → OUT1   |      | Н     |

| ' | П     |       |     | L                                | OUT1 → OUT2   | _    | П     |

| 2 | Н     | L     | L   | Н                                | OUT3 → OUT1   |      | _     |

|   | П     |       | _   | L                                | OUT1 → OUT3   | _    | _     |

| 3 | н     | Н     | H L | Н                                | OUT3 → OUT2   |      | Н     |

| 3 | П     |       | _   | L                                | OUT2 → OUT3   | _    | П     |

| 4 | L     | Н     |     | Н                                | OUT1 → OUT2   | Н    | -     |

| 4 | L     |       | _   | L                                | OUT2 → OUT1   |      | _     |

| 5 | L     | Н     | н   | Н                                | OUT1 → OUT3   | Н    | Н     |

| ) |       |       |     | L                                | OUT3 → OUT1   |      |       |

| 6 |       | L L H | Н   | OUT2 → OUT3                      | Н             |      |       |

| 0 | L     | _     | П   | L                                | OUT3 → OUT2   |      | L     |

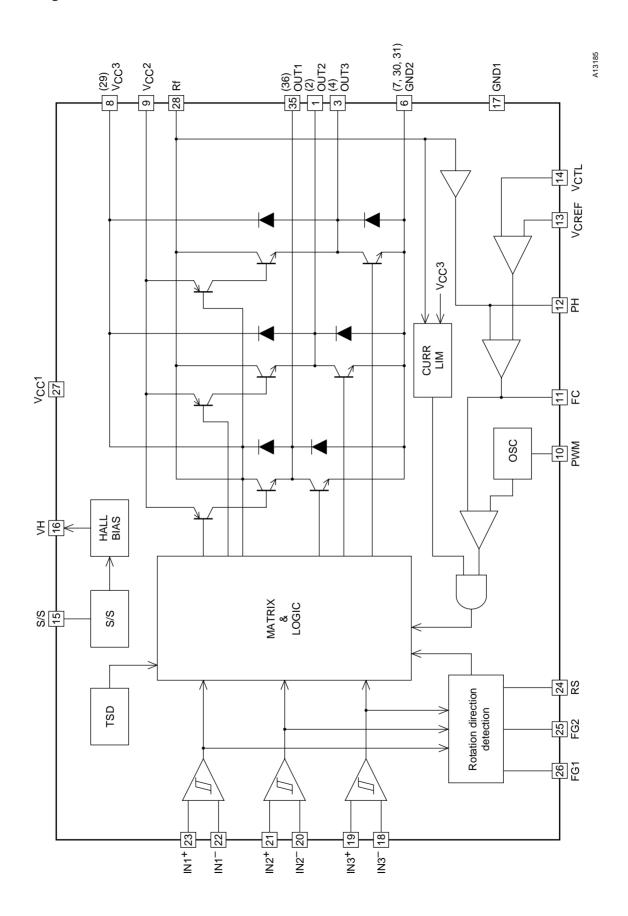

# **Block Diagram**

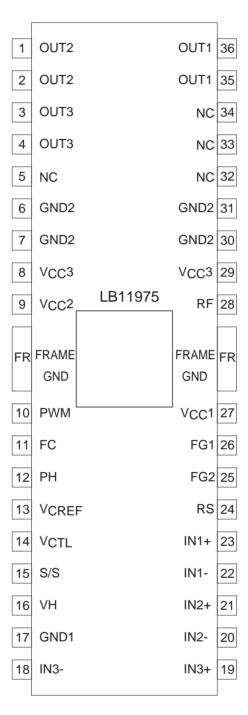

# **Pin Assignment**

Top view

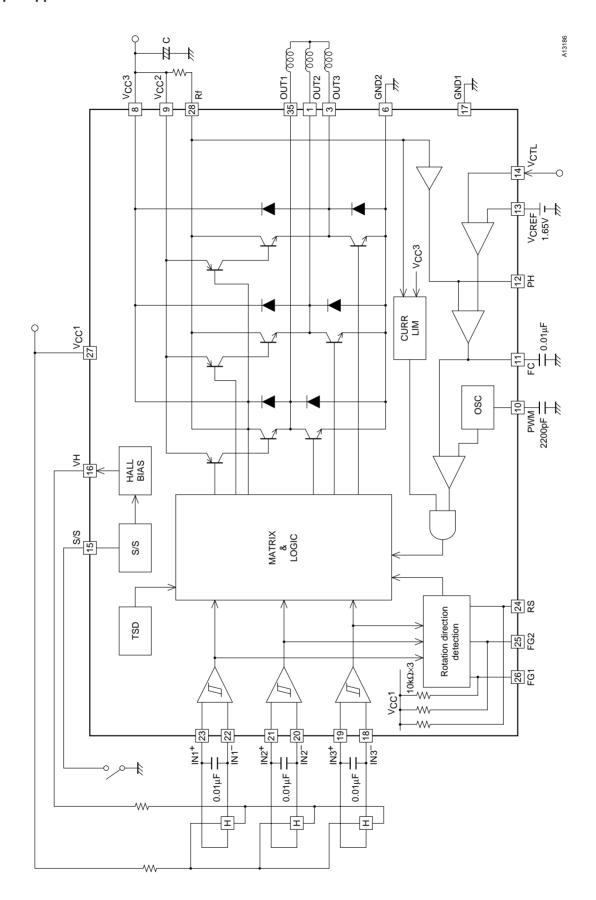

# **Sample Application Circuit**

# LB11975

# **Pin Functions**

| Pin No. | Pin               | Pin voltage                           | Function                                                                                                                                                               | Equivalent circuit                                               |                                                                                  |            |

|---------|-------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------|------------|

| 9       | V <sub>CC</sub> 2 | 4 V to 16 V                           | Supplies the source side pre-drive voltage.                                                                                                                            |                                                                  |                                                                                  |            |

| 8<br>29 | V <sub>CC</sub> 3 | 4 V to 16 V                           | Supplies the motor drive voltage.                                                                                                                                      |                                                                  |                                                                                  |            |

| 27      | V <sub>CC</sub> 1 | 4 V to 16 V                           | Supply voltage for all circuits other than the output transistors and the source side pre-drive voltage                                                                |                                                                  |                                                                                  |            |

| 24      | RS                |                                       | Reverse rotation detection High-level output: Forward rotation Low-level output: Reverse rotation                                                                      |                                                                  |                                                                                  |            |

| 26      | FG1               |                                       | Single Hall device waveform Schmitt comparator synthesized output                                                                                                      | 24 (25) (26)                                                     |                                                                                  |            |

| 25      | FG2               |                                       | Three Hall device waveform Schmitt comparator synthesized output                                                                                                       |                                                                  |                                                                                  |            |

| 23      | IN1 <sup>+</sup>  |                                       | U phase Hall device input. Logic high refers to the state where IN1 <sup>+</sup>                                                                                       |                                                                  |                                                                                  |            |

| 22      | IN1 <sup>-</sup>  |                                       | > IN1 <sup>-</sup> .                                                                                                                                                   |                                                                  |                                                                                  |            |

| 21      | IN2 <sup>+</sup>  | 1.5 V to<br>V <sub>CC</sub> 1 – 1.5 V | V phase Hall device input. Logic high refers to the state where IN2 <sup>+</sup>                                                                                       | (19)                                                             |                                                                                  |            |

| 20      | IN2 <sup>-</sup>  | V <sub>CC</sub> 1 – 1.5 V             | > IN2 <sup>-</sup> .                                                                                                                                                   | $ \begin{array}{c c} \hline (21) & \\ \hline  & \\ \end{array} $ |                                                                                  |            |

| 19      | IN3 <sup>+</sup>  |                                       |                                                                                                                                                                        |                                                                  | W phase Hall device input. Logic high refers to the state where IN3 <sup>+</sup> | 23) 1 (22) |

| 18      | IN3 <sup>-</sup>  |                                       | > IN3 <sup>-</sup> .                                                                                                                                                   | # #                                                              |                                                                                  |            |

| 16      | VH                |                                       | Provides the Hall device lower side bias voltage.                                                                                                                      | Vcc1<br>30kΩ<br>2kΩ<br>/// // // // // // // // // // // // //   |                                                                                  |            |

| 15      | S/S               | 0 V to V <sub>CC</sub> 1              | All circuits can be set to the non-operating state by setting this pin to 0.7 V or under, or by setting it to the open state.  This pin must be held at 2 V or higher. | V <sub>CC</sub> 1  75kΩ  W  50kΩ ₹  //// /// /// /// ///         |                                                                                  |            |

| 17      | GND1              |                                       | Ground for all circuits except the output                                                                                                                              |                                                                  |                                                                                  |            |

Continued on next page.

# Continued from preceding page.

| Pin No.        | Pin                | Pin voltage                         | Function                                                                                                                                                                                                                                                                          | Equivalent circuit                                                                                                                                                                |

|----------------|--------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11             | FC                 |                                     | Control loop frequency characteristics correction  Closed loop oscillation in the current control system can be stopped by connecting a capacitor between this pin and ground.                                                                                                    | V <sub>CC</sub> 1<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2)<br>(3)<br>(4)<br>(5)<br>(6)<br>(6)<br>(7)<br>(7)<br>(8)<br>(8)<br>(9)<br>(9)<br>(9)<br>(9)<br>(9)<br>(9)<br>(9)<br>(9 |

| 10             | PWM                |                                     | PWM oscillator capacitor connection                                                                                                                                                                                                                                               | 65kΩ                                                                                                                                                                              |

| 13             | V <sub>CRE</sub> F | 0 V to<br>V <sub>CC</sub> 1 – 1.5 V | Control reference voltage input The control start voltage is determined by this voltage.                                                                                                                                                                                          | Vcc1                                                                                                                                                                              |

| 14             | VстL               | 0 V to<br>V <sub>CC</sub> 1 – 1.5 V | Speed control voltage input This IC implements a voltage control system in which VC > V <sub>CREF</sub> means forward rotation and VC < V <sub>CREF</sub> means slow foward rotation. (This IC includes reverse rotation prevention circuit, so reverse rotation will not occur.) | 500Ω<br>14<br>500Ω<br>13                                                                                                                                                          |

| 3, 4           | OUT3               |                                     | W phase output                                                                                                                                                                                                                                                                    |                                                                                                                                                                                   |

| 6, 7<br>30, 31 | GND2               |                                     | Ground for the output transistors                                                                                                                                                                                                                                                 | V <sub>CC</sub> <sup>3</sup> V <sub>CC</sub> <sup>2</sup>                                                                                                                         |

| 1, 2           | OUT2               |                                     | V phase output                                                                                                                                                                                                                                                                    |                                                                                                                                                                                   |

| 35, 36         | OUT1               |                                     | U phase output                                                                                                                                                                                                                                                                    | 2kΩ \$                                                                                                                                                                            |

| 28             | RF                 |                                     | Upper side npn transistor collector (shared by all three phases)  Connect a resistor between V <sub>CC</sub> 3 and the RF pin for current detection. The fixed current control system and the current limiter operate by detecting this voltage.                                  | 1 2 3 4<br>35 36<br>2kΩ \$ 6 7 30 31                                                                                                                                              |

| 12             | РН                 |                                     | Peak hold circuit capacitor connection.  Connect a capacitor to this pin to smooth the voltage detected by the resistor RF.                                                                                                                                                       | V <sub>CC</sub> 1  300Ω  12  311kΩ  11 kΩ                                                                                                                                         |

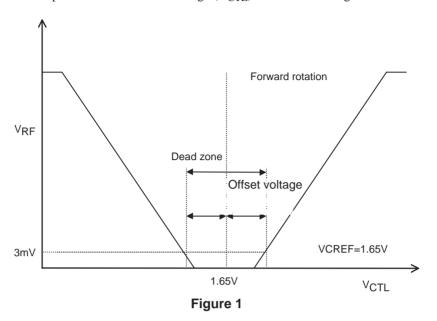

#### **Torque Command**

Figure 1 shows the relationship between the control voltage (V<sub>CTL</sub>) and the RF voltage.

**Truth Table**

|                                      | Operation                |

|--------------------------------------|--------------------------|

| V <sub>CTL</sub> > V <sub>CREF</sub> | Forward rotation         |

| V <sub>CRFF</sub> > V <sub>CTI</sub> | Reverse torque braking * |

Note: \* Since this IC includes a reverse rotation prevention circuit, although the IC will brake the motor if the motor is rotating and V<sub>CTL</sub> < V<sub>CREF</sub>, when reverse rotation is detected, the IC will turn the output off, thus stopping motor rotation.

### **Reverse Rotation Detection Circuit Truth Table**

|                  | RS pin |

|------------------|--------|

| Forward rotation | HIGH   |

| Reverse rotation | LOW    |

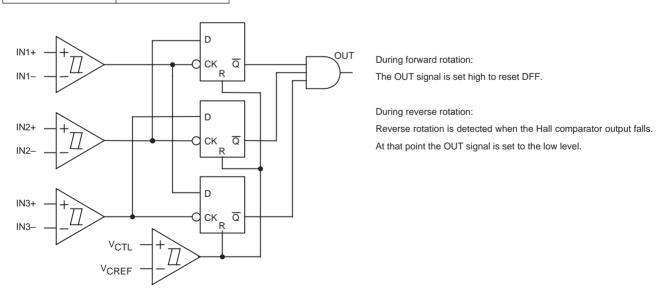

Figure 2 Reverse Rotation Detection Circuit Block Diagram

**Figure 3 Reverse Rotation Timing Chart**

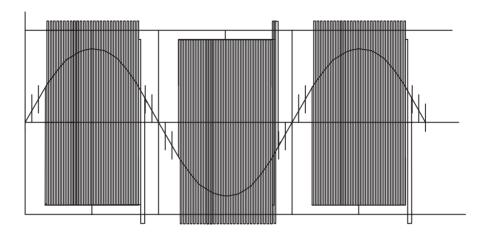

#### **Overview of Reverse Torque Braking**

(This circuit uses a direct PWM drive technique and allows the current limiter to operate during reverse torque braking.)

In earlier direct PWM motor drivers, speed control was implemented by applying PWM to only one (either the upper or lower) output transistor. With this type of driver, the regenerative current formed during reverse torque braking operated as a short-circuit braking. As a result problems such as the coil current exceeding the limit value and I<sub>O</sub>max being exceeded, would occur. To prevent these problems, the LB11975 switches both the upper and lower side output transistors during reverse torque braking to suppress the generation of overcurrents due to regenerative currents when the PWM is off and allows the optimal design of drive currents.

#### **Supplementary Documentation**

Coil current during reverse torque braking

(1) Earlier ICs, with the lower side transistor was switched and the upper side transistor used for current detection (RF)

During reverse torque braking, when the coil current increases and the limit is reached, the lower side output

transistor is turned off. At this time the regenerative current flows through the upper side transistor. The circuit path is

as follows:

$Coil \rightarrow upper \ side \ diode \rightarrow V_{CC} \rightarrow RF \rightarrow upper \ side \ transistor \rightarrow coil$

During regeneration, the upper side transistor is on and the back EMF that occurs at the upper side transistor's emitter pin has a low potential, and since the upper side transistor is fully on at that point, the circuit functions as short-circuit braking.

Even if the regenerative current results in the RF voltage reaching the limit voltage, since the upper side transistor cannot be turned off, the limit circuit will not operate and a coil current in excess of I<sub>O</sub>max may occur.

(2) Earlier ICs, with the upper side transistor was switched and the upper side transistor used for current detection (RF) During reverse torque braking, when the coil current increases and the limit is reached, the upper side output transistor is turned off. At this time the regenerative current flows through the lower side transistor. The circuit path is as follows:

$Coil \rightarrow lower side transistor \rightarrow ground \rightarrow lower side diode \rightarrow coil$

During regeneration, the lower side transistor is on and the back EMF that occurs at the lower side transistor's collector pin has a high potential, and since the lower side transistor is fully on at that point, the circuit functions as short-circuit braking.

Since the regenerative current does not flow through the RF pin, the current limiter circuit does not operate, and a current in excess of  $I_{O}$ max may occur in the lower side transistor.

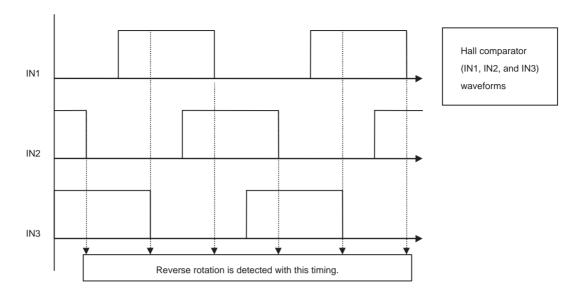

(3) When both the upper and lower side transistors are switched and current detection (RF) is performed in the upper side transistor

During reverse torque braking, when the coil current increases and the limit is reached, both the upper and lower side transistors are turned off. The motor current circuit path at this point is as follows:

$Coil \rightarrow upper side diode \rightarrow V_{CC} \rightarrow power supply line capacitor \rightarrow ground \rightarrow lower side diode \rightarrow coil$  When the limiter circuit operates, both the upper and lower side transistors are turned off, so short-circuit breaking does not occur, and coil current attenuation is all that occurs. Thus this technique allows current control at the set (limiter) current to be performed even during reverse torque braking.

#### **Regenerative Current Path**

#### **Drive Mode**

#### **Braking Mode**

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of January, 2001. Specifications and information herein are subject to change without notice.