LB1825

Three-Phase Brushless Motor Driver

## Overview

The LB1825 is a three-phase brushless motor driver IC optimal for LBP polygon mirror and magneto-optical disk spindle motor drive.

## **Functions and Features**

- Three-phase full-wave current control drive

- PLL speed control

- Internal 24-mode clock divisor switching

- Phase lock detector output

- FG/Hall FG selection

- Current limiter circuit

- 7 V stabilized power supply output pin

- · Reverse torque braking

- · Crystal oscillator circuit

- Internal/external reference frequency selection

- Built-in FG amplifier and FG pulse output

- · Forward/reverse rotation switching

- · Low power supply voltage protection circuit

- Thermal protection circuit

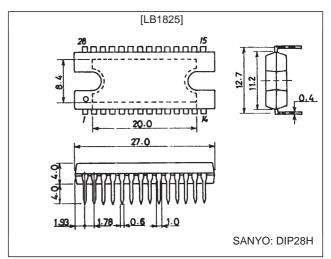

# **Package Dimensions**

unit: mm

#### 3147A-DIP28H

# **Specifications**

Absolute Maximum Ratings at  $Ta = 25^{\circ}C$

| Parameter                   | Symbol Conditions   |                                     | Ratings     | Unit |

|-----------------------------|---------------------|-------------------------------------|-------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max |                                     | 30          | V    |

| Maximum output current      | I <sub>O</sub> max  | t < 0.1 s                           | 2.0         | A    |

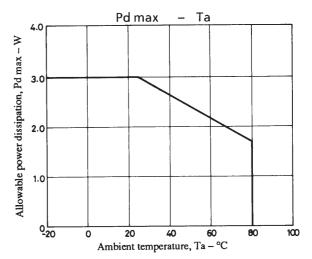

|                             | Pd max1             | Independent IC                      | 3           | W    |

| Allowable power dissipation | Pd max2             | With an arbitrarily large heat sink | 20          | W    |

| Operating temperature       | Topr                |                                     | -20 to +80  | °C   |

| Storage temperature         | Tstg                |                                     | -55 to +150 | °C   |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

# Allowable Operating Ranges at $Ta=25^{\circ}C$

| Parameter      | Symbol          | Conditions | Ratings  | Unit |

|----------------|-----------------|------------|----------|------|

| Supply voltage | V <sub>CC</sub> |            | 10 to 28 | V    |

# Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 24 V

| F                                     | Parameter                     | Symbol                 | Conditions                            | min                    | typ  | max                   | Unit    |

|---------------------------------------|-------------------------------|------------------------|---------------------------------------|------------------------|------|-----------------------|---------|

|                                       |                               | I <sub>CC</sub> 1      | Braking stopped mode                  |                        | 35   | 47                    | mA      |

| Current drai                          | n                             | I <sub>CC</sub> 2      | FG <sub>OUT</sub> 1 stopped mode      |                        | 35   | 47                    | mA      |

|                                       |                               | I <sub>CC</sub> 3      | External clock, braking stopped mode  |                        | 28   | 40                    | mA      |

|                                       | Upper transistor (1)          | V <sub>O</sub> (sat)1  | I <sub>O</sub> = 1.0 A                |                        | 1.0  | 1.6                   | V       |

| Output                                | Upper transistor (2)          | V <sub>O</sub> (sat)2  | I <sub>O</sub> = 1.5 A                |                        | 1.25 | 2.1                   | V       |

| saturation voltage                    | Lower transistor (1)          | V <sub>O</sub> (sat)1  | I <sub>O</sub> = 1.0 A                |                        | 0.6  | 1.0                   | V       |

| g .                                   | Lower transistor (2)          | V <sub>O</sub> (sat)2  | I <sub>O</sub> = 1.5 A                |                        | 0.9  | 1.6                   | V       |

| Output leaka                          | age current                   | I <sub>O LEAK</sub>    |                                       |                        |      | 100                   | μA      |

| [Fixed voltag                         | ge block]                     |                        | 1                                     | I                      |      |                       |         |

| Output volta                          | ge                            | V <sub>REG</sub>       | I <sub>REG</sub> = 20 mA              | 6.3                    | 7.0  | 7.8                   | V       |

| Output curre                          | ent                           | I <sub>REG</sub>       | -                                     | 20                     |      |                       | mA      |

| Load variation                        | on                            | ΔV <sub>REG</sub>      | I <sub>REG</sub> = 0 to 20 mA         |                        |      | 0.25                  | V       |

| Temperature                           | e coefficient                 | αV <sub>REG</sub>      | Design target value                   |                        | -2.0 |                       | mV/°C   |

| [Hall input bl                        | lock]                         |                        |                                       |                        |      |                       |         |

| Input bias cu                         | -                             | I <sub>B</sub> (HA)    |                                       |                        | 1    | 4                     | μA      |

| Common-mo                             | ode input range               |                        |                                       | 1.5                    |      | V <sub>CC</sub> – 1.8 | V       |

| Input sensiti                         |                               | DV <sub>H</sub>        |                                       |                        |      | 20                    | mV      |

| Input offset                          | -                             | V <sub>IOH</sub>       |                                       |                        |      | 20                    | mV      |

| [Drive block]                         | -                             | юп                     | 1                                     | I                      |      |                       |         |

| Dead zone v                           |                               | V <sub>DZ</sub>        |                                       | 50                     |      | 200                   | mV      |

| Output idling                         |                               | V <sub>ID</sub>        |                                       |                        |      | 6                     | mV      |

| Forward gai                           |                               | G <sub>DF</sub> +      |                                       | 0.4                    | 0.5  | 0.6                   |         |

| Reverse gai                           |                               | G <sub>DF</sub>        |                                       | -0.6                   | -0.5 | -0.4                  |         |

|                                       | command voltage               | V <sub>STA</sub>       |                                       | 6.0                    | 6.3  | 0.1                   | V       |

|                                       | command voltage               | V <sub>STO</sub>       |                                       | 0.0                    | 0.8  | 1.5                   | V       |

| Forward limi                          | -                             | VL+                    | $R_f = 1.8 \Omega$                    | 0.45                   | 0.53 | 0.61                  | V       |

| Reverse limi                          | 0                             | VL<br>VL-              | $R_f = 1.8 \Omega$                    | 0.45                   | 0.53 | 0.61                  | V       |

|                                       | parator block]                | •L                     |                                       | 0.10                   | 0.00 | 0.01                  |         |

|                                       | level voltage                 | V <sub>PDH</sub>       | No external load                      | V <sub>REG</sub> - 0.4 |      |                       | V       |

| Output low le                         | -                             | V <sub>PDL</sub>       | No external load                      | VREG 0.4               |      | 0.4                   | V       |

| Output source                         | -                             | IPDL                   |                                       | 0.4                    |      | 0.4                   | mA      |

| Output source                         |                               |                        |                                       | 2.5                    |      |                       | mA      |

| [Error amplif                         |                               | I <sub>PD</sub> -      |                                       | 2.3                    |      |                       | IIIA    |

| Input bias cu                         | -                             |                        |                                       |                        |      | 1                     |         |

|                                       |                               | I <sub>B</sub> (ER)    |                                       | -10                    |      | +10                   | μA      |

| Input offset                          | -                             | V <sub>IO</sub> (ER)   | No external load                      | 5.5                    |      | +10                   | mV<br>V |

|                                       | level voltage                 | VERH                   | No external load                      | 5.5                    |      | 1.0                   | V       |

| Output low lo                         | -                             | V <sub>ERL</sub>       | No external load                      |                        |      | 1.0                   | V       |

| [Lock detect                          | -                             | ) ( t)                 | 40                                    |                        |      | 0.4                   | N       |

| · · · · · · · · · · · · · · · · · · · | ration voltage                | V <sub>LD</sub> (sat)  | I <sub>LD</sub> = 10 mA               |                        |      | 0.4                   | V       |

| [FG amplifie                          | -                             | . (50)                 |                                       |                        |      |                       |         |

| Input bias cu                         |                               | I <sub>B</sub> (FG)    |                                       |                        |      | 1                     | μA      |

| Input offset                          | -                             | V <sub>IO</sub> (FG)   |                                       | -10                    |      | +10                   | mV      |

|                                       | level voltage                 | V <sub>FGH</sub>       | No external load                      | 5.0                    |      |                       | V       |

| Output low le                         | ũ                             | V <sub>FGL</sub>       | No external load                      |                        |      | 2.0                   | V       |

| [FG Schmitt                           | -                             |                        |                                       |                        |      | 1                     |         |

| Input operat                          | -                             | V <sub>IS</sub>        | FG <sub>OUT</sub> 1 generation signal | 160                    |      |                       | mVp-p   |

| · ·                                   | esis (high $ ightarrow$ low)  | V <sub>SHL</sub>       | External clock, braking stopped mode  |                        | 0    |                       | mV      |

| Input hystere                         | esis (low $\rightarrow$ high) | V <sub>SLH</sub>       | External clock, braking stopped mode  |                        | 36   |                       | mV      |

| Hysteresis                            |                               | V <sub>FGS</sub>       |                                       | 18                     | 36   | 60                    | mV      |

|                                       | ration voltage                | V <sub>FG2</sub> (sat) | I <sub>FG2</sub> = 10 mA              |                        |      | 0.4                   | V       |

Continued from preceding page.

| Parameter                             | Symbol                  | Conditions                            | min                    | typ  | max              | Unit |

|---------------------------------------|-------------------------|---------------------------------------|------------------------|------|------------------|------|

| [FG switching setting]                |                         |                                       |                        |      |                  |      |

| Single Hall FG operating level        | V <sub>FGIH</sub>       | FG <sub>IN</sub> pin voltage          | V <sub>REG</sub> – 0.1 |      | V <sub>REG</sub> | V    |

| Triple Hall FG operating level        | V <sub>FGIL</sub>       | FG <sub>IN</sub> pin voltage          | 0                      |      | 0.1              | V    |

| [Stop mode setting]                   |                         |                                       |                        |      |                  |      |

| FG <sub>OUT</sub> 1 low level voltage | V <sub>FG1</sub> L      |                                       |                        |      | 0.4              | V    |

| FG <sub>OUT</sub> 1 low level current | I <sub>FG1</sub> L      | FG <sub>OUT</sub> 1 pin voltage = 0 V |                        | 0.6  | 2.4              | mA   |

| [Current limiter]                     |                         |                                       |                        |      |                  |      |

| Reference voltage                     | V <sub>CS</sub>         | R = 47 kΩ                             | 0.51                   | 0.58 | 0.65             | V    |

| External supply range                 | V <sub>CS</sub> (EX)    |                                       | 0.7                    |      | 3.0              | V    |

| Offset voltage                        | V <sub>CSO</sub>        | R = 47 kΩ, R <sub>f</sub> = 1.8 Ω     | 25                     | 50   | 90               | mV   |

| [Signal block]                        |                         |                                       |                        |      |                  |      |

| Internal oscillator frequency         | fosc                    | Crystal oscillator mode               | 1                      |      | 12               | MHz  |

| External input frequency              | f <sub>REF</sub>        | External clock mode                   | 30                     |      | 5000             | Hz   |

| Low level pin voltage                 | V <sub>OSCL</sub>       |                                       | 4.0                    | 4.5  | 5.0              | V    |

| High level pin current                | IOSCH                   |                                       | 0.3                    | 0.5  | 0.75             | mA   |

| [Divisor switching]                   |                         |                                       |                        |      |                  |      |

| Input high level voltage              | V <sub>N1 to 3</sub> H  |                                       | 4.2                    |      | V <sub>REG</sub> | V    |

| Input middle level voltage            | V <sub>N1 to 3</sub> M  |                                       | 2.1                    |      | 2.9              | V    |

| Input low level voltage               | V <sub>N1 to 3</sub> L  |                                       | 0                      |      | 0.8              | V    |

| [F/R switching]                       |                         |                                       |                        |      |                  |      |

| Input high level voltage              | V <sub>FRH</sub>        |                                       | 2.4                    |      | V <sub>REG</sub> | V    |

| Input low level voltage               | V <sub>FRL</sub>        |                                       | 0                      |      | 1.5              | V    |

| High level input current              | I <sub>FRH</sub>        | F/R pin voltage = V <sub>REG</sub>    |                        |      | 0.22             | mA   |

| [S/B switching]                       |                         |                                       |                        |      |                  |      |

| Input high level voltage              | V <sub>SBH</sub>        |                                       | 2.4                    |      | V <sub>REG</sub> | V    |

| Input low level voltage               | V <sub>SBL</sub>        |                                       |                        |      | 1.5              | V    |

| Hysteresis (high $\rightarrow$ low)   | DV <sub>SB</sub>        |                                       | 0.15                   | 0.25 | 0.35             | V    |

| [Stop detection]                      |                         |                                       |                        |      |                  |      |

|                                       | S <sub>CT</sub> 1       | FG mode                               |                        | 32   |                  |      |

| Count setting                         | S <sub>CT</sub> 2       | Triple Hall FG mode                   |                        | 8    |                  |      |

|                                       | S <sub>CT</sub> 3       | Single Hall FG mode                   |                        | 2    |                  |      |

| [Undervoltage protection]             |                         |                                       |                        |      |                  |      |

| Operating voltage                     | V <sub>SD</sub>         |                                       | 8.4                    | 8.8  | 9.2              | V    |

| Hysteresis                            | DV <sub>SD</sub>        |                                       | 0.2                    | 0.4  | 0.6              | V    |

| [Thermal protection]                  |                         |                                       |                        |      |                  |      |

| Operating temperature                 | T <sub>SD</sub>         | Design target value                   | 150                    | 180  |                  | °C   |

| Recovery temperature                  | T <sub>SDR</sub>        | Design target value                   |                        | 140  |                  | °C   |

| [Pin leakage currents]                |                         |                                       |                        |      |                  |      |

| LD pin                                | I <sub>LD (LEAK)</sub>  | Pin voltage = 30 V                    |                        |      | 10               | μA   |

| FG <sub>OUT</sub> 2 pin               | I <sub>FG2 (LEAK)</sub> | Pin voltage = 30 V                    |                        |      | 10               | μA   |

| [GND pin-heat sink]                   |                         |                                       |                        |      |                  |      |

| Resistance                            |                         | Design target value.                  |                        |      | 30               | Ω    |

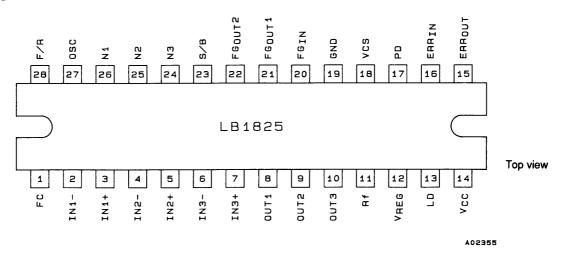

#### **Pin Assignment**

#### **Pin Functions**

| Pin No.  | Symbol                                                                         | Function                                     | Notes                                                                        |

|----------|--------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------|

| 1        | FC                                                                             | Frequency characteristics correction         | A capacitor must be inserted between pin 1 and ground.                       |

| 2 to 7   | IN1 <sup>+</sup> to IN3 <sup>+</sup> ,<br>IN1 <sup>-</sup> to IN3 <sup>-</sup> | Hall element inputs                          | Taken as high when IN <sup>+</sup> > IN <sup>−</sup> , and as low otherwise. |

| 8 to 10  | OUT1 to OUT3                                                                   | Outputs                                      |                                                                              |

| 11       | R <sub>f</sub>                                                                 | Output current detector                      | A capacitor must be inserted between pin 11 and ground.                      |

| 12       | V <sub>REG</sub>                                                               | Stabilized power supply output               |                                                                              |

| 13       | LD                                                                             | Phase lock detector output                   | On when the phase is locked. This pin is an open-collector output.           |

| 14       | V <sub>CC</sub>                                                                | Power supply                                 |                                                                              |

| 15       | ERR <sub>OUT</sub>                                                             | Error amplifier output                       |                                                                              |

| 16       | ERRIN                                                                          | Error amplifier input                        |                                                                              |

| 17       | PD                                                                             | Phase comparator output                      |                                                                              |

| 18       | V <sub>CS</sub>                                                                | Current limiter reference voltage generation |                                                                              |

| 19       | GND                                                                            | Ground                                       |                                                                              |

| 20       | FG <sub>IN</sub>                                                               | FG amplifier input                           | Also functions as the Hall FG switching pin.                                 |

| 21       | FG <sub>OUT</sub> 1                                                            | FG amplifier output                          | The LB1825 goes to stop mode when pin 21 is set low.                         |

| 22       | FG <sub>OUT</sub> 2                                                            | FG/Hall FG output                            | This pin is an open-collector output.                                        |

| 23       | S/B                                                                            | Brake command input                          | Braking is applied when pin 23 is set high.                                  |

| 24 to 26 | N1 to N3                                                                       | Reference frequency divisor switching        | The clock divisor is set by the states of pins 24 to 26.                     |

| 27       | OSC                                                                            | Crystal oscillator/external clock input      |                                                                              |

| 28       | F/R                                                                            | Forward/reverse switching                    |                                                                              |

#### **Clock Divisor Switching**

| Pin N1 | Pin N2 | Divisor $(1)^{*I}$ |

|--------|--------|--------------------|

| L      | L      | *II                |

| L      | М      | 128                |

| L      | Н      | 256                |

| М      | L      | 512                |

| М      | М      | 1024               |

| М      | Н      | 2048               |

| Н      | L      | 4096               |

| Н      | М      | 8192               |

| Н      | Н      | 16384              |

| Pin N3 | Divisor (2) $^{*I}$ |

|--------|---------------------|

| L      | 5                   |

| М      | 4                   |

| Н      | 3                   |

Note: I. Total divisor = (divisor (1)  $\times$  divisor (2))

PLL servo frequency = (crystal oscillator frequency)/(total divisor) II. External clock mode

The PLL servo frequency = external input frequency

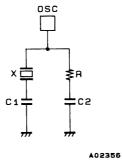

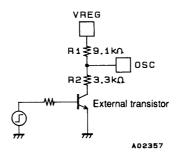

Figure 1 Pin Circuit for Internal Clock Mode

#### Table 1: External Component Values (reference values)

| Crystal (MHz) | C1 (pF) | C2 (pF) | R (kΩ) |

|---------------|---------|---------|--------|

| 3 to 4        | 39      | 82      | 0.82   |

| 4 to 5        | 39      | 82      | 1.0    |

| 5 to 7        | 39      | 47      | 1.5    |

| 7 to 10       | 39      | 27      | 2.0    |

Use a crystal that has a ratio of at least 1:5 between the fundamental f0 impedance and the 3f0 impedance.

### F/R Switching and Phase Selection

| F/R | IN1 | IN2 | IN3 | OUT1 | OUT2 | OUT3 |

|-----|-----|-----|-----|------|------|------|

|     | н   | Н   | L   | М    | Н    | L    |

|     | н   | L   | L   | Н    | М    | L    |

| L   | н   | L   | Н   | Н    | L    | М    |

|     | L   | L   | Н   | М    | L    | Н    |

|     | L   | Н   | Н   | L    | М    | Н    |

|     | L   | Н   | L   | L    | Н    | М    |

|     | н   | Н   | L   | М    | L    | Н    |

|     | н   | L   | L   | L    | М    | Н    |

| н   | н   | L   | Н   | L    | Н    | М    |

|     | L   | L   | Н   | М    | Н    | L    |

|     | L   | Н   | Н   | Н    | М    | L    |

|     | L   | Н   | L   | Н    | L    | М    |

Columns OUT1 to OUT3

H: Source L: Sink

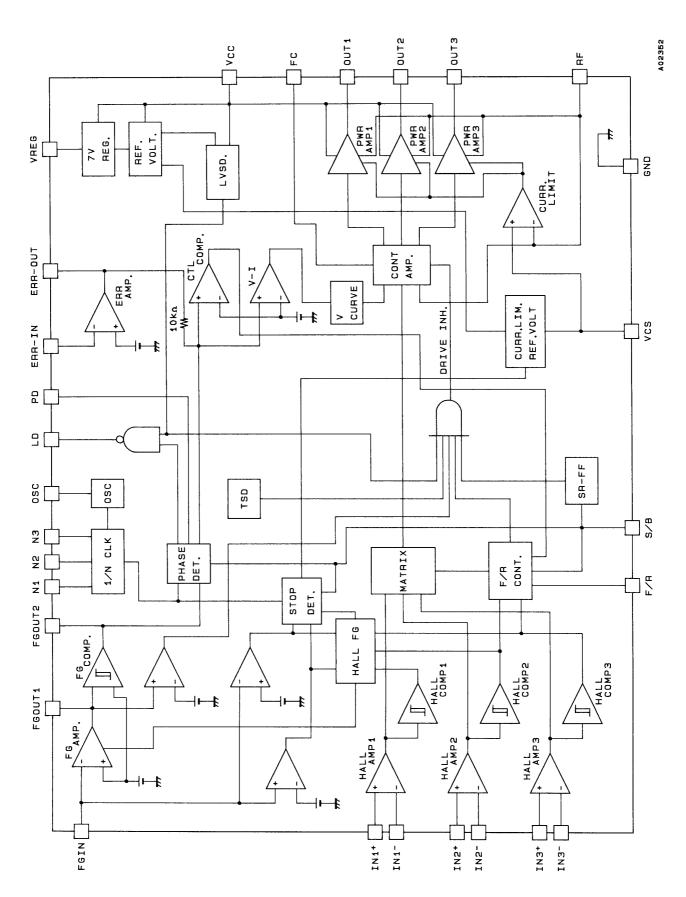

# Equivalent Circuit Block Diagram

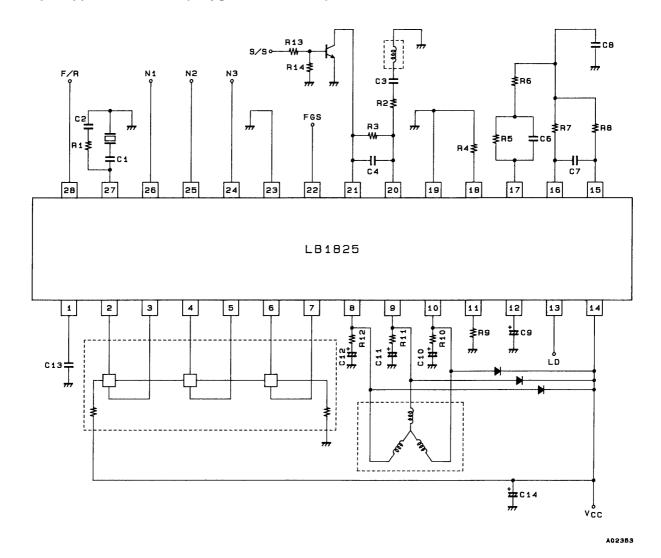

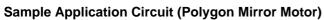

#### Sample Application Circuit (Optical Disk Spindle Motor)

#### **Usage Notes**

1. Position detector circuit (Hall element input circuit)

The position detection circuit consists of a differential amplifier, and will operate if a differential input of 40 mVp-p (minimum) is provided. However, an input of 100 mVp-p is desirable from the standpoint of noise and other problems.

The input DC level must be within the common mode input voltage range (1.5 to ( $V_{CC} - 1.8$ ) V).

2. Current limiter circuit

The output current limiter operates by holding the sink side output transistor in an unsaturated state. The current limit value can be calculated from the following formula.

$I = V_{CS}/R_f$

Where:  $V_{CS} = 0.58$  V typical,  $R_f$  = The value of the resistor between pin 11 and ground.

3. FG input

The following three methods can be used to input the speed signal FG from the motor.

- The signal can be input to  $FG_{IN}$  through an amplifier. (FG mode)

- The Hall input IN1 can be used as the FG input. (single Hall FG mode) This is set up by connecting  $FG_{IN}$  to  $V_{REG}$ .

- The composite signal from the IN1, IN2 and IN3 Hall inputs can be used as the FG input. (triple Hall FG mode) This is set up by connecting FG<sub>IN</sub> to ground.

#### 4. Reference signal input circuit

• Internal clock mode (crystal oscillator)

The values of the external components associated with the crystal oscillator must be set up according to the frequency of the oscillator. (See Table 1.) To avoid trouble with the oscillator circuit, confirm the component values used with the oscillator's manufacturer.

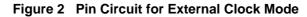

- External clock mode Use the external circuit shown in Figure 2 to input the clock signal when controlling the motor speed using a reference signal with the same frequency as FG.

- 5. Start/stop

When driving motors such as polygon mirror motors, the motor is normally stopped by turning off motor drive and putting the motor in the free-running state. For this type of motor, set the S/B pin low and attach an external transistor at  $FG_{OUT}1$  as shown in the Sample Application Circuit (Optical Disk Spindle Motor) figure to start and stop the drive. (Motor drive is turned off when  $FG_{OUT}1$  is low.)

6. Start/brake

When driving motors such as optical disk spindle motors, stopping is performed by applying some form of braking. In these applications it is necessary for the motor to decelerate briefly and come to a complete stop. See the Sample Application Circuit (Optical Disk Spindle Motor) figure for a sample circuit for this case. (The difference between this circuit and the circuit shown in the Sample Application Circuit (Optical Disk Spindle Motor) figure is the addition of the capacitor C5 to the S/B pin start/brake circuit.)

#### **Braking Operation**

This braking circuit applies full torque reverse rotation braking (in the current limited state) directly after the S/B pin is set low while the motor is turning. After that, the reverse torque is gradually decreased (according to the time constant determined by R4 and C5) at the points where the speed falls below the values listed below. This operation brings the disk to a full stop.

```

f3H = fFG/32 (FG mode)

f3H = fFG/8 (Triple Hall FG mode) f3H: Triple Hall input composite frequency.

f3H = fFG/2 (Single Hall FG mode) fFG: The FG frequency when locked

```

Depending on the size of the disk and the motor torque the following adjustments may be required to improve the disk stopping characteristics.

- 1. Increase the time constant if the motor continues to rotate in the forward direction after the braking torque has gone to zero.

- 2. Decrease the time constant if the motor is observed to rotate in the reverse direction due to the braking operation.

- 3. A value of about 51 k  $\!\Omega$  is recommended for R4. In particular, it should be under 100 k  $\!\Omega$ .

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of August, 1997. Specifications and information herein are subject to change without notice.