# SANYO Semiconductors DATA SHEET

An ON Semiconductor Company

# LC709006A — I/O-Expander for Microcontroller

#### Overview

The LC709006A is a peripheral IC dedicated for expanding the capability of the microcontroller (MCU) I/O ports. It interfaces with the microcontroller through synchronous serial communication. Communication with the extended I/O ports is accomplished through 24-bit parallel I/O. The extended port features include the capabilities to specify the I/O direction on a bit basis, to specify the output type (CMOS or N-channel open drain), and to specify the I/O voltage level on a port basis according to the power level of the peripheral equipment. These features make allow the LC709004A to be used in a wide variety of applications.

#### **Features**

- 4-/5-wire synchronous serial transmission and reception, and 24-bit parallel I/O

- Wide operating voltage range (2.0V to 6.0V)

- Multifunction I/O ports

- I/O direction specification: Bit units

- CMOS or Nch-OD output type specification: Bit units

- Output voltage adjustment: Port (8 bits) units

- Output current: 12mA max. (capable of driving a green LED directly)

- Data transmission and reception: Can control reception of input data and transmission of output data in parallel.

- Cascaded configuration: Ports can be expanded in units of 24 bits × n (n is the number of LSI chips).

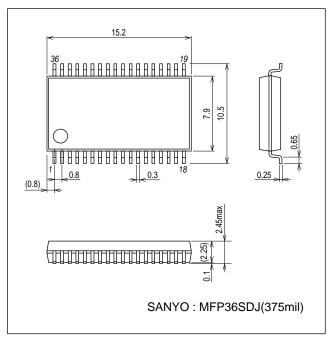

- Packaging from: MFP36SDJ (375mil): lead-free type

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment. The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for new introduction or other application different from current conditions on the usage of automotive device, communication device, office equipment, industrial equipment etc., please consult with us about usage condition (temperature, operation time etc.) prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

http://www.sanyosemi.com/en/network/

# **Specifications**

Absolute Maximum Ratings at  $Ta=25^{\circ}C,\ V_{SS}=V_{SS}\ P0=V_{SS}P2=0V$

| Darameter                 | Cumbal              | Din/Domorko                                                                     | Conditions                             |                     |      | Ratings |                            | Llois |

|---------------------------|---------------------|---------------------------------------------------------------------------------|----------------------------------------|---------------------|------|---------|----------------------------|-------|

| Parameter                 | Symbol              | Pin/Remarks                                                                     | Conditions                             | V <sub>DD</sub> [V] | min  | typ     | max                        | Unit  |

| Maximum supply voltage    | V <sub>DD</sub> max | V <sub>DD</sub> , V <sub>DD</sub> P0,<br>V <sub>DD</sub> P1, V <sub>DD</sub> P2 | $V_{DD}=V_{DD}P0=$ $V_{DD}P1=V_{DD}P2$ |                     | -0.3 |         | +7.0                       |       |

| Input voltage             | VI                  | RES, CS, DIN,                                                                   |                                        |                     | -0.3 |         | V <sub>DD</sub> +0.3       |       |

| Output voltage            | V <sub>O</sub>      | DOUT                                                                            |                                        |                     | -0.3 |         | V <sub>DD</sub> +0.3       |       |

| Input/output voltage      | V <sub>IO</sub> (1) | Port 0                                                                          |                                        |                     | -0.3 |         | V <sub>DD</sub> P0<br>+0.3 | V     |

|                           | V <sub>IO</sub> (2) | Port 1                                                                          |                                        |                     | -0.3 |         | V <sub>DD</sub> P1<br>+0.3 |       |

|                           | V <sub>IO</sub> (3) | Port 2                                                                          |                                        |                     | -0.3 |         | V <sub>DD</sub> P2<br>+0.3 |       |

| High level output current |                     |                                                                                 |                                        |                     |      |         |                            |       |

| Peak output current       | IOPH(1)             | Ports 0 to 2                                                                    | CMOS output                            |                     | -7   |         |                            |       |

|                           | IOPH(2)             | DOUT                                                                            | selected Per 1 applicable pin          |                     | -13  |         |                            |       |

| Mean output current       | IOMH(1)             | Ports 0 to 2                                                                    | CMOS output                            |                     | -3   |         |                            |       |

| (Note 1)                  | IOMH(2)             | DOUT                                                                            | selected Per 1 applicable pin          |                     | -6   |         |                            |       |

| Total output current      | ∑IOP0H              | Port 0                                                                          | Total of all applicable pins           |                     | -32  |         |                            | mA    |

|                           | ∑IOP1H              | Port 1                                                                          | Total of all applicable pins           |                     | -32  |         |                            |       |

|                           | ∑IOP2H              | Port 2                                                                          | Total of all applicable pins           |                     | -32  |         |                            |       |

|                           | ∑IOAH               | DOUT, ports 0 to 1                                                              | Total of all applicable pins           |                     | -105 |         |                            |       |

| Low level output current  |                     |                                                                                 |                                        |                     |      |         |                            |       |

| Peak output current       | IOPL(1)             | Ports 0 to 2                                                                    | Per 1 applicable                       |                     |      |         | 16                         |       |

|                           | IOPL(2)             | DOUT                                                                            | pin                                    |                     |      |         | 13                         |       |

| Mean output current       | IOML(1)             | ports 0 to 2                                                                    | Per 1 applicable                       |                     |      |         | 7                          |       |

| (Note 1)                  | IOML(2)             | DOUT                                                                            | pin                                    |                     |      |         | 6                          |       |

| Total output current      | ∑IOP0L              | Port 0                                                                          | Total of all applicable pins           |                     |      |         | 32                         | mA    |

|                           | ∑IOP1L              | Port 1                                                                          | Total of all applicable pins           |                     |      |         | 32                         |       |

|                           | ∑IOP2L              | Port 2                                                                          | Total of all applicable pins           |                     |      |         | 32                         |       |

|                           | ΣIOAL               | DOUT, ports 0 to 2                                                              | Total of all applicable pins           |                     |      |         | 105                        |       |

| Power dissipation         | Pd max              | MFP36SDJ                                                                        | Ta=-30 to +70°C                        |                     |      |         | 330                        |       |

|                           |                     |                                                                                 | Ta=-40 to +85°C                        |                     |      |         | 250                        | mW    |

| Operating temperature     | Topr                |                                                                                 |                                        |                     | -40  |         | 85                         | °C    |

| Storage temperature       | Tstg                |                                                                                 |                                        |                     | -55  |         | 125                        |       |

Note 1: The mean output current is a mean value measured over 100ms.

# Allowable Operating Conditions at $Ta=-40\ to\ +85^{\circ}C,\ V_{SS}=V_{SS}\ P0=V_{SS}P2=0V$

| D                        | 0                   | D: /D                                  | 0 - 100                                                            |                     | Spec                        | cification (No | ote 3)                  | Unit |  |

|--------------------------|---------------------|----------------------------------------|--------------------------------------------------------------------|---------------------|-----------------------------|----------------|-------------------------|------|--|

| Parameter                | Symbol              | Pin/Remarks                            | Conditions                                                         | V <sub>DD</sub> [V] | V <sub>DD</sub> [V] min typ |                | max                     | Uill |  |

| Operating supply voltage | V <sub>DD</sub> (1) | $V_{DD}$                               |                                                                    |                     | 2.0                         |                | 6.0                     |      |  |

|                          | V <sub>DD</sub> (2) | V <sub>DD</sub> P0                     | Supply voltage must be within V <sub>DD</sub> (1)'s specification. |                     | V <sub>DD</sub> -3.0        |                | V <sub>DD</sub>         |      |  |

|                          | V <sub>DD</sub> (3) | V <sub>DD</sub> P1, V <sub>DD</sub> P2 | Supply voltage must be within V <sub>DD</sub> (1)'s specification. |                     | V <sub>DD</sub>             |                | V <sub>DD</sub> +3.0    |      |  |

| High level input voltage | V <sub>IH</sub> (1) | DIN, ports 0 to 2                      |                                                                    | 4.5 to 6.0          | 0.3V <sub>DD</sub> +0.7     |                | $V_{DD}Px$              | V    |  |

|                          | V <sub>IH</sub> (2) | DIN, ports 0 to 2                      |                                                                    | 2.0 to 6.0          | 0.3V <sub>DD</sub> +0.7     |                | $V_{DD}Px$              | V    |  |

|                          | V <sub>IH</sub> (3) | RES, CS, CLK                           |                                                                    | 4.5 to 6.0          | 0.4V <sub>DD</sub> +0.7     |                | V <sub>DD</sub>         |      |  |

|                          | V <sub>IH</sub> (4) | RES, CS, CLK                           |                                                                    | 2.0 to 6.0          | 0.4V <sub>DD</sub> +0.7     |                | V <sub>DD</sub>         |      |  |

| Low level input voltage  | V <sub>IL</sub> (1) | DIN, ports 0 to 2                      |                                                                    | 4.5 to 6.0          | V <sub>SS</sub>             |                | 0.2V <sub>DD</sub> +0.1 |      |  |

|                          | V <sub>IL</sub> (2) | DIN, ports 0 to 2                      |                                                                    | 2.0 to 6.0          | V <sub>SS</sub>             |                | 0.2V <sub>DD</sub> +0.1 |      |  |

|                          | V <sub>IL</sub> (3) | RES, CS, CLK                           |                                                                    | 4.5 to 6.0          | V <sub>SS</sub>             |                | 0.1V <sub>DD</sub> +0.2 |      |  |

|                          | V <sub>IL</sub> (4) | RES, CS, CLK                           |                                                                    | 2.0 to 6.0          | V <sub>SS</sub>             |                | 0.1V <sub>DD</sub> +0.2 |      |  |

Note 3: V<sub>DD</sub>Px denote the power supply pin (V<sub>DD</sub>P0,V<sub>DD</sub>P1,V<sub>DD</sub>P2) for port pins.

# **Electrical Characteristics** at Ta = -40 to $+85^{\circ}C$ , $V_{SS} = V_{SS}$ $P0 = V_{SS}$ P2 = 0V

| Danasatas                               | O: male al          | Dia/Damanta                                                                   | 0                                                                                 | (No                 | te 3)                 | Spe                    | cification         |     | 1.1-24 |

|-----------------------------------------|---------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------|-----------------------|------------------------|--------------------|-----|--------|

| Parameter                               | Symbol              | Pin/Remarks                                                                   | Conditions                                                                        | V <sub>DD</sub> [V] | V <sub>DD</sub> Px[V] | min                    | typ                | max | Unit   |

| High level input current                | lН                  | RES, CS, CLK, Ports 0 to 2                                                    | V <sub>IN</sub> =V <sub>DD</sub><br>(including output Tr.<br>off leakage current) | 2.0 to 6.0          |                       |                        |                    | 10  |        |

| Lower level input current               | ημ                  | RES, CS, CLK,<br>Ports 0 to 2                                                 | VIN=VSS<br>(including output Tr.<br>off leakage current)                          | 2.0 to 6.0          |                       | -10                    |                    |     | μА     |

| High level output                       | V <sub>OH</sub> (1) | Ports 0                                                                       | I <sub>OH</sub> =-2mA                                                             | 2.0 to 6.0          | 4.5 to 6.0            | V <sub>DD</sub> Px-0.5 |                    |     |        |

| voltage                                 | V <sub>OH</sub> (2) |                                                                               | I <sub>OH</sub> =-5mA                                                             | 2.0 to 6.0          | 4.5 to 6.0            | V <sub>DD</sub> Px-1.0 |                    |     |        |

|                                         | V <sub>OH</sub> (3) |                                                                               | I <sub>OH</sub> =-1mA                                                             | 2.0 to 6.0          | 2.0 to 6.0            | V <sub>DD</sub> Px-0.5 |                    |     |        |

|                                         | V <sub>OH</sub> (4) | Ports 1                                                                       | I <sub>OH</sub> =-2mA                                                             | 2.0 to 6.0          | 4.5 to 6.0            | V <sub>DD</sub> Px-0.5 |                    |     |        |

|                                         | V <sub>OH</sub> (5) |                                                                               | I <sub>OH</sub> =-5mA                                                             | 2.0 to 6.0          | 4.5 to 6.0            | V <sub>DD</sub> Px-1.0 |                    |     |        |

|                                         | V <sub>OH</sub> (6) |                                                                               | I <sub>OH</sub> =-1mA                                                             | 2.0 to 6.0          | 2.0 to 6.0            | V <sub>DD</sub> Px-0.5 |                    |     |        |

|                                         | V <sub>OH</sub> (7) | DOUT                                                                          | I <sub>OH</sub> =-5mA                                                             | 4.5 to 6.0          |                       | V <sub>DD</sub> Px-0.5 |                    |     |        |

|                                         | V <sub>OH</sub> (8) |                                                                               | I <sub>OH</sub> =-10mA                                                            | 4.5 to 6.0          |                       | V <sub>DD</sub> Px-1.0 |                    |     |        |

|                                         | V <sub>OH</sub> (9) |                                                                               | I <sub>OH</sub> =-2mA                                                             | 2.0 to 6.0          |                       | V <sub>DD</sub> Px-0.5 |                    |     |        |

| Lower level output                      | V <sub>OL</sub> (1) | Ports 0                                                                       | I <sub>OL</sub> =5mA                                                              | 4.5 to 6.0          | 2.0 to 6.0            |                        |                    | 0.4 | V      |

| voltage                                 | V <sub>OL</sub> (2) | 1                                                                             | I <sub>OL</sub> =12mA                                                             | 4.5 to 6.0          | 2.0 to 6.0            |                        |                    | 1   |        |

|                                         | V <sub>OL</sub> (3) |                                                                               | I <sub>OL</sub> =2mA                                                              | 2.0 to 6.0          | 2.0 to 6.0            |                        |                    | 0.4 |        |

|                                         | V <sub>OL</sub> (4) | Ports 1,2                                                                     | I <sub>OL</sub> =5mA                                                              | 4.5 to 6.0          | 4.5 to 6.0            |                        |                    | 0.4 |        |

|                                         | V <sub>OL</sub> (5) |                                                                               | I <sub>OL</sub> =12mA                                                             | 4.5 to 6.0          | 4.5 to 6.0            |                        |                    | 1   |        |

|                                         | V <sub>OL</sub> (6) |                                                                               | I <sub>OL</sub> =2mA                                                              | 2.0 to 6.0          | 2.0 to 6.0            |                        |                    | 0.4 |        |

|                                         | V <sub>OL</sub> (7) | DOUT                                                                          | I <sub>OL</sub> =5mA                                                              | 4.5 to 6.0          |                       |                        |                    | 0.4 |        |

|                                         | V <sub>OL</sub> (8) |                                                                               | I <sub>OL</sub> =10mA                                                             | 4.5 to 6.0          |                       |                        |                    | 1   |        |

|                                         | V <sub>OL</sub> (9) |                                                                               | I <sub>OL</sub> =2mA                                                              | 2.0 to 6.0          |                       |                        |                    | 0.4 |        |

| Pull-up resistance                      | Rpu(1)              | CS                                                                            | V <sub>OH</sub> =V <sub>SS</sub>                                                  | 4.5 to 6.0          |                       | 100                    | 230                | 650 | kΩ     |

| Voltage hysteresis                      | VHIS                | RES, CS, CLK                                                                  |                                                                                   | 2.0 to 6.0          |                       |                        | 0.1V <sub>DD</sub> |     | V      |

| Consumption current (operation stopped) | IDDSP               | V <sub>DD</sub> =V <sub>DD</sub> P0=<br>V <sub>DD</sub> P1=V <sub>DD</sub> P2 | RES=CS=VDD  CLK=DIN=VDD or VSS  DOUT=open P0 to P2=open or VDD  or VSS (Note 2)   | 2.0 to 6.0          |                       |                        |                    | 20  | μА     |

| Pin capacity                            | CP                  | All pins                                                                      | Other than test pin VIN=VSS f=1MHz Ta=25°C                                        | 2.0 to 6.0          |                       |                        | 10                 |     | pF     |

Note 2: The consumption current does not include the current flowing into the port's output transistor.

Note 3:  $V_{DD}Px$  denote the power supply pin  $(V_{DD}P0, V_{DD}P1, V_{DD}P2)$  for port pins.

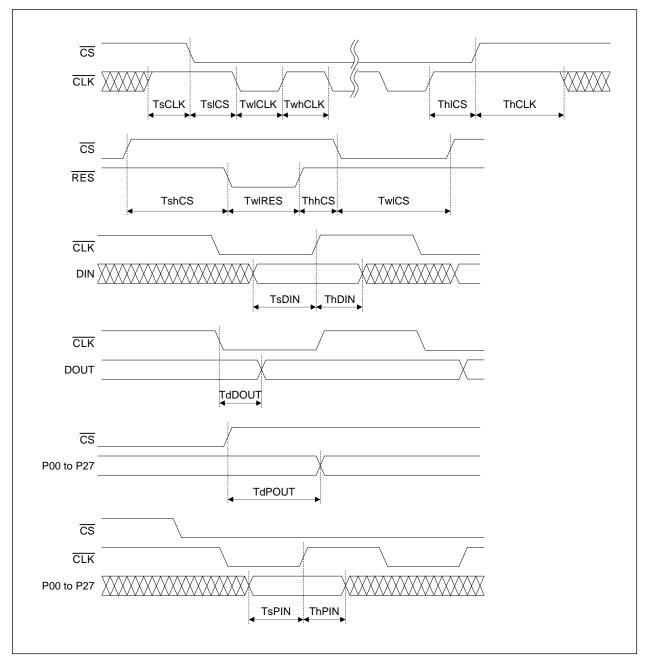

# $\textbf{Switching I/O Characteristics} \text{ at } Ta=-40 \text{ to } +85^{\circ}\text{C}, V_{DD}=V_{DD}P0=V_{DD}P1=V_{DD}P2, V_{SS}=V_{SS}P0=V_{SS}P1=V_{SS}P2, V_{SS}=0V_{SS}P1=V_{SS}P2, V_{SS}=0V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P1=V_{SS}P$

| Parameter                         | Symbol | Pin/Remarks | Conditions                         |                     |      | pecification |     | Unit |

|-----------------------------------|--------|-------------|------------------------------------|---------------------|------|--------------|-----|------|

|                                   | -,     |             |                                    | V <sub>DD</sub> [V] | min  | typ          | max |      |

| Clock setup time                  | TsCLK  | CS, CLK     | <ul> <li>Specified with</li> </ul> |                     |      |              |     |      |

|                                   |        |             | respect to falling                 | 2.0 to 6.0          | 100  |              |     |      |

|                                   |        |             | edge of $\overline{\text{CS}}$ .   |                     |      |              |     |      |

|                                   |        |             | •See Fig. 9.                       |                     |      |              |     |      |

| Chip select low level setup       | TsICS  | CS, CLK     | •Specified with                    |                     |      |              |     |      |

| time                              |        |             | respect to falling                 | 2.0 to 6.0          | 100  |              |     |      |

|                                   |        |             | edge of CS.                        |                     |      |              |     |      |

|                                   |        | <del></del> | •See Fig. 9.                       |                     |      |              |     |      |

| Chip select low level hold        | ThICS  | CS, CLK     | <ul> <li>Specified with</li> </ul> |                     |      |              |     |      |

| time                              |        |             | respect to falling                 | 2.0 to 6.0          | 100  |              |     |      |

|                                   |        |             | edge of $\overline{\text{CS}}$ .   |                     |      |              |     |      |

|                                   |        |             | •See Fig. 9.                       |                     |      |              |     |      |

| Clock hold time                   | ThCLK  | CS, CLK     | <ul> <li>Specified with</li> </ul> |                     |      |              |     |      |

|                                   |        |             | respect to falling                 | 2.0 to 6.0          | 200  |              |     |      |

|                                   |        |             | edge of CS.                        | 2.0 10 0.0          | 200  |              |     |      |

|                                   |        |             | ∙See Fig. 9.                       |                     |      |              |     |      |

| Clock low level pulse width       | TwlCLK | CLK         | ∙See Fig. 9.                       | 4.5 to 6.0          | 250  |              |     |      |

|                                   |        |             |                                    | 2.7 to 6.0          | 500  |              |     |      |

|                                   |        |             |                                    | 2.0 to 6.0          | 1000 |              |     |      |

| Clock high level pulse            | TwhCLK | CLK         | •See Fig. 9.                       | 4.5 to 6.0          | 250  |              |     |      |

| width                             |        |             |                                    | 2.7 to 6.0          | 500  |              |     |      |

|                                   |        |             |                                    | 2.0 to 6.0          | 1000 |              |     |      |

| Chip select high level setup time | TshCS  | CS, RES     | •See Fig. 9.                       | 2.0 to 6.0          | 200  |              |     |      |

| Chip select high level hold       | ThhCS  | CS, RES     | •See Fig. 9.                       | 001.00              | 400  |              |     |      |

| time                              |        |             |                                    | 2.0 to 6.0          | 100  |              |     | ns   |

| Chip select low level pulse width | TwlCS  | CS, RES     | •See Fig. 9.                       | 2.0 to 6.0          | 200  |              |     | 113  |

| Reset low level pulse width       | TwiRES | CS, RES     | •See Fig. 9.                       | 2.0 to 6.0          | 150  |              |     |      |

| Data setup time                   | TsDIN  | DIN         | •Specified with                    | 4.5 to 6.0          | 30   |              |     |      |

|                                   |        |             | respect to falling                 | 4.5 10 6.0          | 30   |              |     |      |

|                                   |        |             | edge of CLK. •See Fig. 9.          | 2.0 to 6.0          | 50   |              |     |      |

| Data hold time                    | ThDIN  | DIN         | Specified with                     | 4.5 to 6.0          | 50   |              |     |      |

|                                   |        |             | respect to falling edge of CLK.    | 2.7 to 6.0          | 150  |              |     |      |

|                                   |        |             | •See Fig. 9.                       | 2.0 to 6.0          | 300  |              |     |      |

| Serial data output delay          | TdD0UT | DOUT        | •Specified with                    | 4.5 to 6.0          |      |              | 200 |      |

| time                              |        |             | respect to falling                 | 2.7 to 6.0          |      |              | 400 |      |

| (Note 4)                          |        |             | edge of CLK. •See Fig. 9.          | 2.0 to 6.0          |      |              | 800 |      |

| Port data output delay time       | TdPOUT | Port 0 to 2 | Specified with                     | 4.5 to 6.0          |      |              | 200 |      |

|                                   |        |             | respect to rising                  | 2.7 to 6.0          |      |              | 400 |      |

|                                   |        |             | edge of CS.                        |                     |      |              |     |      |

|                                   |        |             | •See Fig. 9.                       | 2.0 to 6.0          |      |              | 800 |      |

| Port data input setup time        | TsPIN  | Port 0 to 2 | •Specified with respect to rising  | 4.5 to 6.0          | 30   |              |     |      |

|                                   |        |             | edge of CLK. •See Fig. 9.          | 2.0 to 6.0          | 50   |              |     |      |

| Port data input hold time         | ThPIN  | Port 0 to 2 | •Specified with                    | 4.5 to 6.0          | 50   |              |     |      |

|                                   |        |             | respect to rising edge of CLK.     | 2.7 to 6.0          | 150  |              |     |      |

|                                   | i      | 1           | Leage of CLK                       | 1                   |      |              |     | i    |

Note 4: The input data of P00 will be out from DOUT terminal at the first negative edge of  $\overline{\text{CLK}}$  signal. Because of this, Serial data output delay time of the first clock will be the time measured from the negative edge of the  $\overline{\text{CLK}}$  or the time at the input data (P00) is settled.

# **Package Dimensions**

unit: mm (typ)

3263

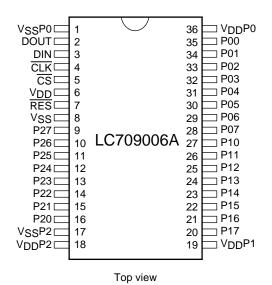

# **Pin Assignment**

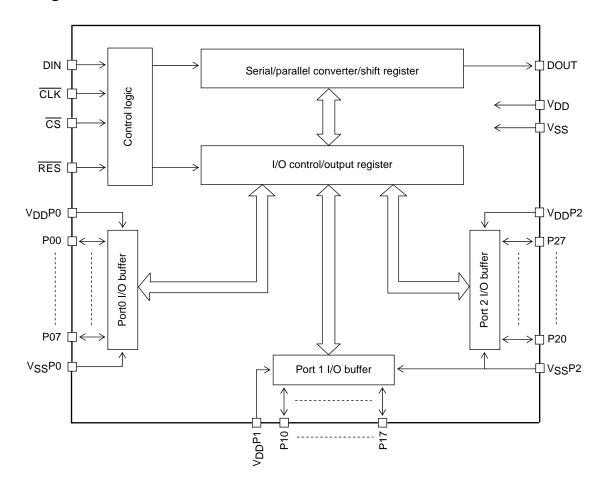

# **Block Diagram**

## **Pin Description**

| Pin Name           | I/O | Description                                                                                                          | I/O Type    | Reset Time |

|--------------------|-----|----------------------------------------------------------------------------------------------------------------------|-------------|------------|

| V <sub>SS</sub>    | -   | • - power supply pin                                                                                                 |             |            |

| V <sub>SS</sub> P0 |     | V <sub>SS</sub> is the power supply pin for blocks other than I/O ports (P00 to P27).                                |             |            |

| $V_{SS}P2$         |     | V <sub>SS</sub> P0 is the power supply pin for port pins P00 to P07.                                                 |             |            |

|                    |     | V <sub>SS</sub> P2 is the power supply pin for port pins P10 to P17 and P20 to P27.                                  |             |            |

| $V_{DD}$           | -   | • + power supply pin                                                                                                 |             |            |

| $V_{DD}P0$         |     | • V <sub>DD</sub> is the power supply pin for blocks other than I/O ports (P00 to P27).                              |             |            |

| V <sub>DD</sub> P1 |     | V <sub>DD</sub> P0 is the power supply pin for port pins P00 to P07.                                                 |             |            |

| $V_{DD}P2$         |     | V <sub>DD</sub> P1 is the power supply pin for port pins P10 to P17.                                                 |             |            |

|                    |     | V <sub>DD</sub> P2 is the power supply pin for port pins P20 to P27.                                                 |             |            |

|                    |     | (Notes)                                                                                                              |             |            |

|                    |     | <ul> <li>V<sub>DD</sub>P0 must not be set higher than V<sub>DD</sub> I (V<sub>DD</sub>P0≤V<sub>DD</sub>).</li> </ul> |             |            |

|                    |     | <ul> <li>V<sub>DD</sub>P1 must not be set lower than V<sub>DD</sub> (V<sub>DD</sub>P1≥V<sub>DD</sub>).</li> </ul>    |             |            |

|                    |     | <ul> <li>V<sub>DD</sub>P2 must not be set lower than V<sub>DD</sub> (V<sub>DD</sub>P2≥V<sub>DD</sub>).</li> </ul>    |             |            |

| Port 0             | I/O | 8-bit I/O port                                                                                                       | Output:     | Hi-Z       |

| P00 to P07         |     | I/O specifiable in 1 bit units.                                                                                      | CMOS/Nch-OD |            |

|                    |     | CMOS/Nch-open drain specifiable in 1 bit units.                                                                      | Input: TTL  |            |

|                    |     | Output voltage variable in 1 port units according to V <sub>DD</sub> P0 voltage.                                     |             |            |

| Port 1             | I/O | • 8-bit I/O port                                                                                                     | Output:     | Hi-Z       |

| P10 to P17         |     | I/O specifiable in 1 bit units.                                                                                      | CMOS/Nch-OD |            |

|                    |     | CMOS/Nch-open drain specifiable in 1 bit units.                                                                      | Input: TTL  |            |

|                    |     | Output voltage variable in 1 port units according to V <sub>DD</sub> P1 voltage.                                     |             |            |

| Port 2             | I/O | 8-bit I/O port                                                                                                       | Output:     | Hi-Z       |

| P20 to P27         |     | I/O specifiable in 1 bit units.                                                                                      | CMOS/Nch-OD |            |

|                    |     | CMOS/Nch-open drain specifiable in 1 bit units.                                                                      | Input: TTL  |            |

|                    |     | <ul> <li>Output voltage variable in 1 port units according to V<sub>DD</sub>P2 voltage.</li> </ul>                   |             |            |

Continued on next page.

Continued from preceding page.

| Pin Name | I/O | Description                                                                                  | I/O Type     | Reset Time |

|----------|-----|----------------------------------------------------------------------------------------------|--------------|------------|

| DIN      | - 1 | Serial data input pin                                                                        | Input: TTL   |            |

| DOUT     | 0   | Serial data output pin                                                                       | Output: CMOS | High       |

| CLK      |     | Serial clock input pin                                                                       | Input: TTL   |            |

|          | I   | Port data is placed on DOUT on the falling edge of this clock.                               | Schmidt      |            |

|          |     | The data from DIN is latched on the negative-to-positive transition of this clock.           |              |            |

| CS       | - 1 | Chip select input pin                                                                        | Input: TTL   |            |

|          |     | Setting this pin to the low level enables serial data to be input or output.                 | Schmidt      |            |

|          |     |                                                                                              |              |            |

| RES      | - 1 | Device's system reset input pin                                                              | Input: TTL   |            |

|          |     | Setting this pin to the low level initializes the internal control circuit and registers and | Schmidt      |            |

|          |     | puts DOUT in the high level and all data port pins (P00 to P27) into the Hi-Z state.         |              |            |

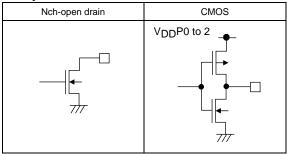

### Port Output Types and I/O States

The output type and I/O states of the LC709006A's ports can be selected by configuring the data direction register (DDR) and data register (DTR). Port data can be taken into the LC709006A only when DDR is set to 0 (Nch-open drain) and DTR is set to 1 (Nch-Tr OFF). The ports are held high for the other settings of DDR and DTR.

| Deat Name                | DDD | DTD | Port           |                 |        |  |  |

|--------------------------|-----|-----|----------------|-----------------|--------|--|--|

| Port Name                | DDR | DTR | Output Type    | Input           | Output |  |  |

|                          | 0   | 1   | Nch-open drain | Enabled         | Hi-Z   |  |  |

| P00 to P07               | 0   | 0   | Nch-open drain | Disabled (High) | Low    |  |  |

| P10 to P17<br>P20 to P27 | 1   | 1   | CMOS           | Disabled (High) | High   |  |  |

| 1 20 10 1 21             | 1   | 0   | CMOS           | Disabled (High) | Low    |  |  |

**Port Output Circuit**

### **Principles of Operation**

The LC709006A accomplishes data transmission and reception to and from the MCU through synchronous serial communication and performs I/O operations on the extended ports in parallel mode. Its communication modes (MCU to LC709006A by serial to parallel conversion and LC709006A to MCU by parallel to serial conversion) include the initial communication modes (modes 0 and 1) in which the LC709006A initializes itself and the data communication mode in which the LC709006A sends and receives port data. The initial communication modes are used for various communication control purposes for the first time in system operation after a power-on or system reset. In these modes, the LC709006A sets up the I/O mode and output type of the ports. The data communication mode is used for communication control after the end of the initial communication modes. In this mode, the LC709006A carries out actual port I/O operations. The port I/O mode and output type settings are stored in the data direction register (DDR). The data output state settings ("High" output, "Hi-Z" output, or "Low" output) are stored in the data register (DTR). The LC709006A's operating modes are summarized below, followed by detailed mode descriptions.

| Communication Mode         |        | Description                                                                                               |

|----------------------------|--------|-----------------------------------------------------------------------------------------------------------|

| Mode 0                     |        | Sets the output type of all ports to "N-ch-open drain."                                                   |

| Initial communication mode | Mode 1 | Sets the I/O direction of the ports and the their output type to CMOS or "Nch-open-drain" on a bit basis. |

| Data communication mode    |        | Sends and receives port data.                                                                             |

#### (1) Initial communication modes

- Mode 0

- 1) Setting the  $\overline{RES}$  pin to the low level initializes the system, sets the DOUT pin to the high level, and sets the DDR register of all ports to 0 and the DTR register to 1. The output type of the ports is set to Nch-open drain and their I/O state (Nch-Tr=OFF) to the "Hi-Z" (input mode) state.

- 2) When the  $\overline{RES}$  pin is set high (reset) and the  $\overline{CS}$  pin is set and held low for a certain period (TwlCS), the DDR is fixed at 0. Subsequently, the LC709006A is placed in the data communication mode.

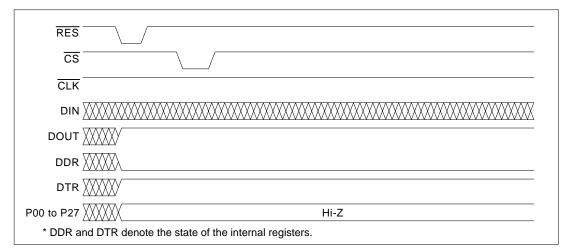

Fig. 1

- Mode 1

- 1) When the RES pin is set to the low level, the LC709006A initializes the system, sets the DOUT pin to the high level, and sets the DDR register of all ports to 0 and the DTR register to 1. The output type of the ports is set to Nch-open drain and their I/O state (Nch-Tr=OFF) to the "Hi-Z" (input mode) state.

- 2) When the RES pins is set high (reset) and the CS pin is set low, the LC709006A gets ready for serial communication.

- 3) The input data at P00 is sent directly to the DOUT pin on the first falling edge of the transmission clock signal CLK. The data at pins P01 to P27 is loaded into the shift register on the rising edge of the next clock.

- 4) Subsequently, the ports' input data, which is loaded into the shift register on the falling edge of CLK, is placed at the DOUT pin sequentially (P00→P07, P20→P27) in synchronization with the falling edges of CLK, starting at port pin P00. In parallel with this operation, when data to be placed at the ports is supplied to the DIN pin sequentially starting at the port pin P00 (P00→P07, P10→P17, P20→P27), it is loaded into the internal shift register in synchronization with the rising edges of CLK.

- 5) When the  $\overline{\text{CS}}$  pin is set high after the rising edge of the 24th clock, the data loaded in the shift register is loaded into the DDR register which determines the I/O mode and output type of the data (serial data is loaded into the DDR register after a reset is effected). Subsequently, the LC709006A controls serial data transmission and reception in the data communication mode.

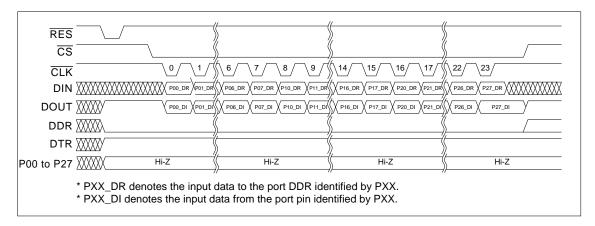

Fig. 2

- (2) Data communication mode

- 1) When the  $\overline{\text{CS}}$  pin is set low with the  $\overline{\text{RES}}$  pin held high, the LC709006A gets ready for serial communication. (Subsequently, processing in steps 2) and 3) are identical to steps 2) and 3) in paragraph (1)-2).

- 2) The input data at P00 is sent directly to the DOUT pin on the first falling edge of the CLK signal. Data at pins P01 to P27 is loaded into the shift register on the next rising edge of the clock.

- 3) Subsequently, the ports' input data, which is loaded into the shift register on the falling edge of CLK, is placed at the DOUT pin sequentially (P00→P07, P10→P17, P20→P27) in synchronization with the falling edges of CLK, starting at port pin P00. In parallel with this operation, when data to be placed at the ports is supplied to the DIN pin sequentially starting at the port pin P00 (P00→P07, P10→P17, P20→P27), it is loaded into the internal shift register in synchronization with the rising edges of CLK.

- 4) When the CS pin is set high after the rising edge of the 24th clock, the data loaded in the shift register is loaded into the DDR register which determines the output state of the ports and the states of all port pins (P00 to P27) are then changed (output) according to the conditions established in the DDR and DTR registers. Serial data that occurs following the initial communication mode processing is always loaded into the DTR register.

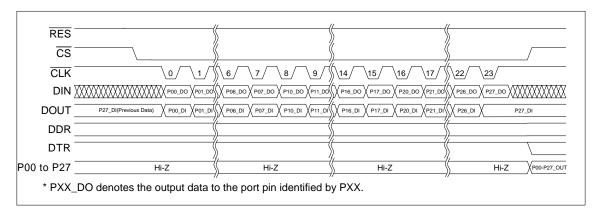

Fig. 3

5) Subsequently, the state of all port pins (P00 to P27) is updated each time the set of steps 1) to 4) described in paragraph (2) are performed.

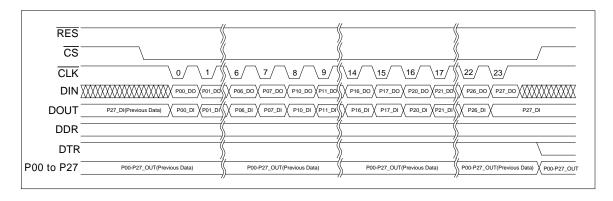

Fig. 4

Note: Connect a Pull-up resister (about  $100k\Omega$ ) to  $\overline{CS}$  using MCU VDD.

#### **Application Examples**

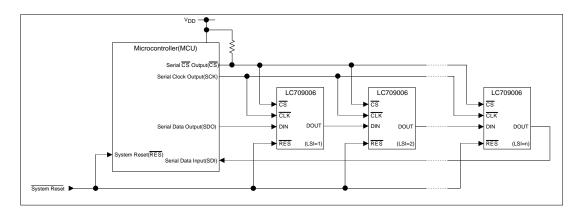

#### (1) Example of a cascade configuration

Two or more LC709006A LSI chips can be cascaded to realize port expansion beyond 24 bits. Port expansion, however, need to be made in units of 24 bits  $\times$  n (n denotes the number of LSI chips).

Fig. 5

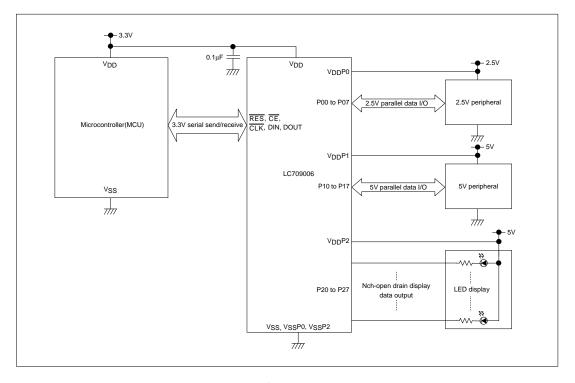

#### (2) Variable port power level example

When controlling the level of I/O ports according to the power voltage level of the peripheral equipment, the user can connect the output from the power supply of the peripheral equipment directly to the power supply pins for the I/O ports. The LC709006A dispenses with the need to add an external level shifter circuit. Note the following when configuring the LC709006A in this way:

#### Note 5:

- V<sub>DD</sub>P0: The voltage level of V<sub>DD</sub>P0 must not be higher than that of V<sub>DD</sub> (V<sub>DD</sub>P0≤V<sub>DD</sub>).

- VDDP1: The voltage level of VDDP1 must not be lower than that of VDD (VDDP1≥VDD).

- VDDP2: The voltage level of VDDP2 must not be lower than that of VDD (VDDP2≥VDD).

- The input level of all ports (P00 to P27) is dependent on the V<sub>DD</sub> power source; it depends on none of the power sources V<sub>DD</sub>P0 to V<sub>DD</sub>P2.

- \* Be sure to check the electrical characteristics of the LC709006A.

Fig. 6

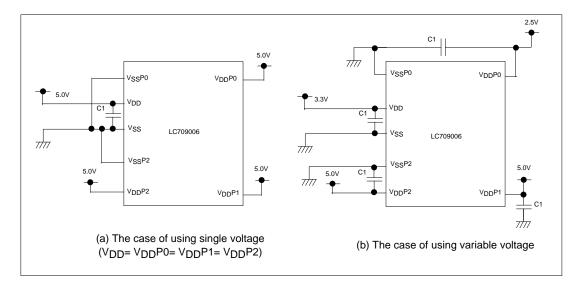

## Example of Placing Bypass Capacitors between VDD and VSS Terminals

Fig. 7

In the case of using single voltage source as showing in the Fig.7 (a), you must connect a bypass capacitor (C1, about  $0.1\mu F$ ) between  $V_{DD}$  and  $V_{SS}$ . When connecting the capacitor (C1) and  $V_{DD}$ - $V_{SS}$ , use a thick wire, and try to make its length as short as possible: moreover, try to make the impedance of  $V_{DD}$ -C1 and  $V_{SS}$ -C1 equal. In addition, when using several voltage sources as showing in the Fig.7 (b), it is suggested to connect the bypass capacitor to each set of the voltage terminals.

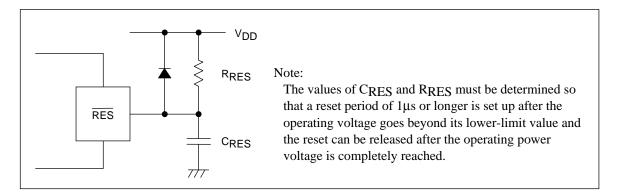

Fig. 8: Reset Circuit

Fig. 9: Serial I/O and Parallel Data I/O Timing Diagram

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- Regarding monolithic semiconductors, if you should intend to use this IC continuously under high temperature, high current, high voltage, or drastic temperature change, even if it is used within the range of absolute maximum ratings or operating conditions, there is a possibility of decrease reliability. Please contact us for a confirmation.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co..Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned

This catalog provides information as of October, 2012. Specifications and information herein are subject to change without notice.