### Ordering number: EN 38898

### **Overview**

The LC7152, 7152M, 7152NM, 7152KM are universal dual-PLL frequency synthesizers for use in cordless telephone applications in the USA, South Korea and Japan, and broadcast satellite (BS) tuners in the USA and Europe.

### Features

- Dual charge pump for fast channel switching

- Digital lock detector for PLL lock status check with crystal oscillator precision

- Programmable reference frequency divider ideal for various applications

- LC7152NM with built-in power-on reset circuit version of the LC7152M

- LC7152KM with enhanced frequency characteristics version of the LC7152M

### Functions

- 2-system PLL built-in (dual PLL)

- 16-bit programmable local-oscillator divider 1.5 to 55MHz ( $V_{DD} = 2.0$  to 3.3V), LC7152KM: 55 to 80MHz ( $V_{DD} = 2.7$  to 3.3V)

- 14-bit programmable reference-frequency divider

- 320Hz to 640kHz reference frequency using a 10.24MHz crystal

- Digital lock detector

- Dual charge pump

- Amplifier built-in for an active LPF

- Serial transmission data input (CCB format)

- LC7152NM with power-on reset circuit (outputs OUTA and OUTB become open at power-on)

- 2.0 to 3.3V supply

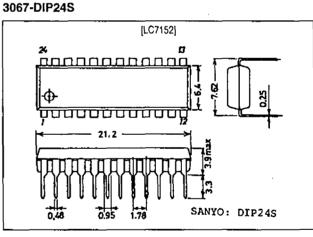

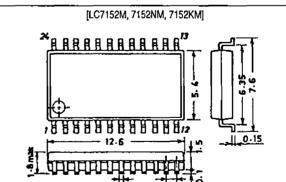

- DIP24S and MFP24S packages

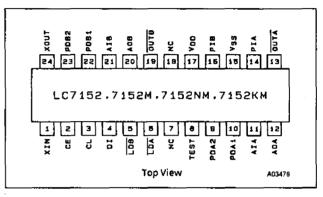

## Pin Assignment

# Package Dimensions

Unit: mm

3112-MFP24S

0-35 1.0 SANYO: MFP24S

## SANYO Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

41495TH (ID) No. 3889-1/12

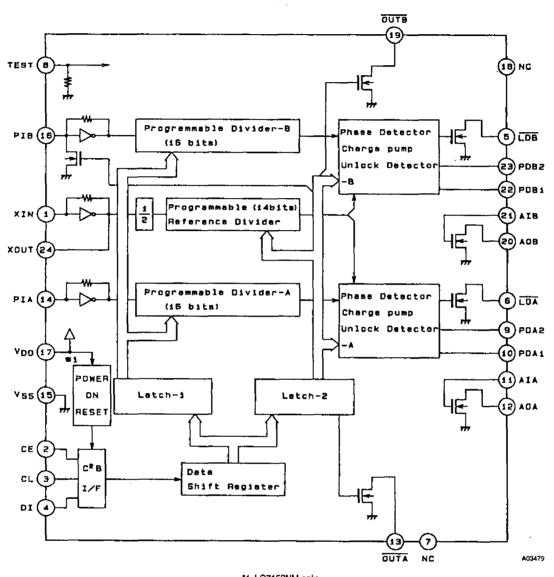

**Block Diagram**

\*1. LC7152NM only

# **Pin Functions**

| Number | Name  | Function                              |

|--------|-------|---------------------------------------|

| 1      | XIN   | Crystal oscillator input              |

| 2      | CE    | Chip enable input                     |

| 3      | CL    | Clock input                           |

| 4      | DI    | Serial data input                     |

| 5      | LDB . | PLL-B unlock detector output          |

| 6      | ĹDA   | PLL-A unlock detector output          |

| 7      | NC    | No connection                         |

| 8      | TEST  | Test input                            |

| 9      | PDA2  | PLL-A phase detector secondary output |

| 10     | PDA1  | PLL-A phase detector main output      |

| 11     | AIA   | LPF transistor A input                |

| 12     | AOA   | LPF transistor A output               |

No. 3889-2/12

-

# LC7152, 7152M, 7152NM, 7152KM

| Number | Name            |                                       | Function                              |    |

|--------|-----------------|---------------------------------------|---------------------------------------|----|

| 13     | OUTA            | General-purpose output port           |                                       |    |

| 14     | PIA             | PLL-A local-oscillator input          |                                       |    |

| . 15   | V <sub>SS</sub> | Ground                                |                                       |    |

| 16     | PIB             | PLL-B local-oscillator input          |                                       |    |

| 17     | V <sub>DD</sub> | 3V supply                             |                                       |    |

| 18     | NC              | No connection                         |                                       |    |

| 19     | OUTB            | General-purpose output port           |                                       |    |

| 20     | AOB             | LPF transistor B output               |                                       |    |

| 21     | AIB             | LPF transistor B input                |                                       | "· |

| 22     | PDB1            | PLL-B phase detector main output      |                                       |    |

| 23     | PDB2            | PLL-B phase detector secondary output | · · · · · · · · · · · · · · · · · · · |    |

| 24     | XOUT            | Crystal oscillator output             |                                       |    |

# Specifications

Absolute Maximum Ratings at Ta = 25°C,  $V_{SS} = 0V$

| Parameter                   | Symbol                 | Conditions                                                                                                                                                                                   | Ratings                                                                                                                                                                                                                                                                                                | Unit |

|-----------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max    | V <sub>DD</sub>                                                                                                                                                                              | -0.3 to +7.0                                                                                                                                                                                                                                                                                           | V    |

|                             | V <sub>IN</sub> max(1) | CE, CL, DI, AIA, AIB                                                                                                                                                                         | -0.3 to +7.0                                                                                                                                                                                                                                                                                           | v    |

| Maximum input voltage       | V <sub>IN</sub> max(2) | V <sub>DD</sub> -0.3 to +7.0           CE, CL, DI, AIA, AIB         -0.3 to +7.0           XIN, PIA, PIB, TEST         -0.3 to V <sub>00</sub> + 0.3           LDA, LDB         -0.3 to +7.0 | V                                                                                                                                                                                                                                                                                                      |      |

|                             | V <sub>O</sub> max(1)  | LDA, LDB                                                                                                                                                                                     | -0.3 to +7.0                                                                                                                                                                                                                                                                                           | v    |

| Maximum output voltage      | V <sub>O</sub> max(2)  | AOA, AOB, OUTA, OUTB                                                                                                                                                                         | -0.3 to +15                                                                                                                                                                                                                                                                                            | V    |

|                             | V <sub>O</sub> max(3)  | PDA1, PDA2, PDB1, PDB2, XOUT                                                                                                                                                                 | 0.3 to V <sub>DD</sub> + 0.3                                                                                                                                                                                                                                                                           | V    |

|                             | l <sub>o</sub> max(1)  | LDA, LDB, OUTA, OUTB                                                                                                                                                                         | 0 to +3                                                                                                                                                                                                                                                                                                | mA   |

| Maximum output current      | l <sub>O</sub> max(2)  | AOA, AOB                                                                                                                                                                                     | -0.3 to +7.0           -0.3 to +7.0           -0.3 to V <sub>00</sub> + 0.3           -0.3 to V <sub>00</sub> + 0.3           -0.3 to +7.0           UTB           -0.3 to +15           PDB2, XOUT           -0.3 to +3           0 to +3           0 to +6           350           I, 7152NM, 7152KM | mA   |

|                             | Dd may                 | Ta ≤ 85°C, LC7152                                                                                                                                                                            | 350                                                                                                                                                                                                                                                                                                    | mW   |

| Allowable power dissipation | Pd max                 | Ta ≤ 85°C, LC7152M, 7152NM, 7152KM                                                                                                                                                           | 160                                                                                                                                                                                                                                                                                                    | mW   |

| Operating temperature       | Topr                   |                                                                                                                                                                                              | -40 to +85                                                                                                                                                                                                                                                                                             | °C   |

| Storage temperature         | Tstg                   |                                                                                                                                                                                              | -55 to +125                                                                                                                                                                                                                                                                                            | °C   |

Allowable Operating Ranges at Ta = -40 to +85°C,  $V_{SS} = 0V$

| Parameter                | Symbol              | Conditions                                                                                                       | min                                                                                                                                                                                                                                                                                                                                                                                                                 | typ | max | Unit |

|--------------------------|---------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

|                          | V <sub>DD</sub> (1) | V <sub>DD</sub>                                                                                                  | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                 | _   | 3.3 | v    |

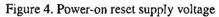

| Supply voltage           | V <sub>DD</sub> (2) | V <sub>DD</sub> : Serial data retention voltage, see<br>Figure 4 <sup>1</sup>                                    | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                 | -   | -   | v    |

|                          | V <sub>DD</sub> (3) | V <sub>DO</sub> 2.0     -     3.3       V <sub>DO</sub> : Serial data retention voltage, see     1.5     -     - | · V                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |      |

|                          | V <sub>IH</sub> (1) |                                                                                                                  | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                 | _   | 5.5 | v    |

| Input high-level voltage | V <sub>IH</sub> (2) | CE, CL, DI: $V_{DD}$ = 3.3V,<br>(Note that $V_{iH}$ can exceed $V_{DD}$ )                                        | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                              | v   |     |      |

| Input low-level voltage  | V <sub>IL</sub> (1) | CE, CL, DI: V <sub>DD</sub> = 2.0V                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                   | -   | 0.4 | v    |

| input low-level voltage  | V <sub>IL</sub> (2) | CE, CL, DI: V <sub>DD</sub> = 3.3V                                                                               | 2.0       -       3.3         1 retention voltage, see       1.5       -       -         reset voltage, $t_R \ge 20ms^1$ -       -       0.05         = 2.0V, an exceed V <sub>DD</sub> )       1.5       -       5.5         = 3.3V, an exceed V <sub>DD</sub> )       1.7       -       5.5         = 2.0V       0       -       0.4         = 3.3V       0       -       0.6         0       -       5.5       - | v   |     |      |

|                          | V <sub>0</sub> (1)  | LDA, LDB                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                   | -   | 5.5 | · V  |

| Output voltage           | V <sub>0</sub> (2)  | AOA, AOB, OUTA, OUTB                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                   | -   | 13  | v    |

No. 3889-3/12

į

| Parameter                    | Symbol              | Conditions                                                | min | typ   | max | Unit  |

|------------------------------|---------------------|-----------------------------------------------------------|-----|-------|-----|-------|

|                              | f <sub>IN</sub> (1) | XIN: Sine wave, capacitively coupled                      | 1.0 |       | 13  | MHz   |

| Input frequency              | f <sub>IN</sub> (2) | PIA, PIB: Sine wave, capacitively coupled <sup>2</sup>    | 1.5 | -     | 55  | MHz   |

| -                            | f <sub>IN</sub> (3) | PIA, PIB: Sine wave, capacitively<br>coupled <sup>3</sup> | 55  | _     | 80  | MHz   |

|                              | V <sub>IN</sub> (1) | XIN: Sine wave, capacitively coupled                      | 200 | -     | 600 | mVrms |

| Input amplitude              | V <sub>IN</sub> (2) | PIA, PIB: Sine wave, capacitively coupled <sup>2,3</sup>  | 100 | -     | 600 | mVrms |

| Crystal oscillator frequency | f <sub>X'tal</sub>  | XIN, XOUT: $CI \le 50\Omega$ , $C_L \le 16pF^4$           | 4   | 10.24 | 11  | MHz   |

1. LC7152NM

2. 1.5 to 23MHz when FA/FB = 0, 20 to 55MHz when FA/FB = 1,  $V_{DD}$  = 2.0 to 3.3V, LC7152, 7152M, 7152NM, 7152KM. FA and FB are serial data input frequency select bits. 3. 55 to 80MHz when FA/FB = 1,  $V_{DD}$  = 2.7 to 3.3V, LC7152KM. FA and FB are serial data input frequency select bits. 4. CI is the crystal impedance and CL is the load capacitance.

## Electrical Characteristics within the allowable operating ranges

| Parameter                     | Symbol                                 | Conditions                                                                                               | min                   | typ  | max  | Unit |

|-------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------|------|------|------|

| Output high level values      | V <sub>OH</sub> (1)                    | PDA1, PDB1: I <sub>0</sub> = 1mA                                                                         | V <sub>DD</sub> - 1.0 | -    | _    | V    |

| Output high-level voltage     | V <sub>OH</sub> (2)                    | PDA2, PDB2: I <sub>O</sub> = 2mA                                                                         | V <sub>DD</sub> - 1.0 |      | -    | v    |

|                               | V <sub>OL</sub> (1)                    | PDA1, PDB1: I <sub>O</sub> = 1mA                                                                         | _                     | -    | 1.0  | v    |

|                               | V <sub>QL</sub> (2)                    | PDA2, PDB2: I <sub>O</sub> = 2mA                                                                         | -                     | _    | 1.0  | v    |

| Output law laws loss have     | V <sub>OL</sub> (3)                    | OUTA, OUTB: I <sub>O</sub> = 1mA                                                                         | _                     | -    | 1.0  | v    |

| utput low-level voltage       | V <sub>OL</sub> (4)                    | LDA, LDB: I <sub>O</sub> = 2mA                                                                           | _                     | -    | 1.0  | v    |

|                               | V <sub>OL</sub> (5)                    | AOA, AOB: 1 <sub>0</sub> = 0.5mA, AIA = AIB = 1.2V                                                       | -                     | _    | 0.5  | v    |

|                               | V <sub>OL</sub> (6)                    | AOA, AOB: I <sub>O</sub> = 1mA, AIA = AIB = 1.3V                                                         | _                     | -    | 0.5  | V    |

|                               | I <sub>OFF</sub> (1)                   | LDA, LDB: V <sub>O</sub> = 5.5V                                                                          | _                     | -    | 5.0  | μA   |

| Output leakage current        | I <sub>OFF</sub> (2)                   | PDA1, PDB1, PDA2, PDB2: Vo = 0/3.3V                                                                      | -                     | 0.01 | 10.0 | nA   |

|                               | I <sub>OFF</sub> (3)                   | AOA, AOB, OUTA, OUTB: Vo = 13V                                                                           | -                     | -    | 5.0  | μА   |

|                               | I <sub>III</sub> (1)                   | CE, CL, DI: V <sub>1</sub> = 5.5V                                                                        | -                     | -    | 5.0  | μA   |

|                               | I <sub>IM</sub> (2)                    | XIN: V <sub>1</sub> = 3.3V, V <sub>DD</sub> = 3.3V                                                       | 2.0                   | -    | 6.5  | μA   |

| Input high-level current      | I <sub>H</sub> (3)                     | PIA, PIB: V <sub>I</sub> = 3.3V, V <sub>DD</sub> = 3.3V                                                  | 3.5                   | -    | 10.0 | μA   |

| ,                             | <br>I <sub>IH</sub> (4)                | AIA, AIB: V <sub>1</sub> = 3.3V                                                                          | -                     | 0.01 | 10.0 | nA   |

|                               | ا <sub>اH</sub> (5)                    | TEST: V <sub>1</sub> = 3.3V, V <sub>DD</sub> = 3.3V                                                      | -                     | 120  | -    | μA   |

|                               | l <sub>IL</sub> (1)                    | CE, CL, DI: V <sub>1</sub> = 0V                                                                          | -                     | -    | 5.0  | μΑ   |

|                               | l <sub>IL</sub> (2)                    | XIN: V <sub>1</sub> = 0V, V <sub>DD</sub> = 3.3V                                                         | 2.0                   | -    | 6.5  | μA   |

| Input low-level current       | ا <sub>ال</sub> (3)                    | PIA, PIB: V <sub>1</sub> = 0V, V <sub>DD</sub> = 3.3V                                                    | 3.5                   | -    | 10.0 | μA   |

|                               | –––––––––––––––––––––––––––––––––––––– | AIA, AIB: V <sub>I</sub> = 0V                                                                            | -                     | 0.01 | 10.0 | nA   |

|                               | –––––––––––––––––––––––––––––––––––––– | TEST: V <sub>1</sub> = 0V, V <sub>DD</sub> = 3.3V                                                        |                       | _    | 5.0  | μΑ · |

|                               | R <sub>(</sub> (1)                     | XIN: V <sub>DD</sub> = 3.3V                                                                              | -                     | 1.0  | -    | MΩ   |

| Internal reedback resistance  | R <sub>f</sub> (2)                     | PIA, PIB: V <sub>DD</sub> = 3.3V                                                                         | -                     | 600  | -    | kΩ   |

| Internal pull-down resistance | Rd                                     | PIA, PIB: $V_{DD} = 3.3V$ -         600         -           TEST: $V_{DD} = 3.3V$ -         30         - |                       | kΩ   |      |      |

| Input capacitance             | C <sub>IN</sub>                        | XIN, PIA, PIB                                                                                            | -                     | 2.5  | -    | ρF   |

| Cupelu europti                | I <sub>DD</sub> (1)                    | V <sub>DD</sub> (= 2.0V): I <sub>IN</sub> = 55MHz                                                        | -                     | 3.0  | 8.0  | mA   |

|                               | 1 <sub>00</sub> (2)                    | V <sub>DD</sub> (= 3.3V): f <sub>IN</sub> = 55MHz                                                        | -                     | 7.0  | 14.0 | mA   |

| Supply current <sup>2</sup> | 1 <sub>DD</sub> (4) | V <sub>DD</sub> (= 2.0V): I <sub>IN</sub> = 55MHz | - | 1.5 | 4.5 | mA |

|-----------------------------|---------------------|---------------------------------------------------|---|-----|-----|----|

| Supply current              | I <sub>DD</sub> (5) | V <sub>DD</sub> (= 3.3V): f <sub>IN</sub> = 55MHz | - | 3.9 | 8.0 | mA |

1. Dual PLL operation (both PLL-A and PLL-B), SB = 0,  $f_{XIN}$  = 10.24MHz (crystal), PIA and PIB input = 100mVrms at  $f_{IN}$ , all other inputs at  $V_{SS}$ , all other outputs open. 2. Standby mode: Single PLL operation (PLL-A operating and PLL-B stopped), SB = 1,  $f_{XIN}$  = 10.24MHz (crystal), PIA input = 100mVrms at  $f_{IN}$ , all other inputs at  $V_{SS}$ , all other outputs open.

No. 3889-4/12

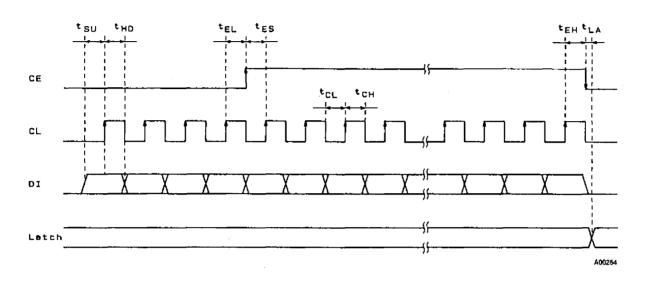

# Serial Data Input Timing

.

| Parameter                    | Symbol          | Conditions                | min                  | max                 | Unit |

|------------------------------|-----------------|---------------------------|----------------------|---------------------|------|

| Data anti                    |                 | 10.24MHz crystal          | 0.40                 | -                   | μs   |

| Data setup time              | t <sub>SU</sub> | Other crystal frequencies | 4/f <sub>x'tal</sub> | -                   | -    |

| Data hold time               |                 | 10.24MHz crystal          | 0.40                 | -                   | μs   |

| Data noig time               | Чнр             | Other crystal frequencies | 4/f <sub>X'tal</sub> |                     | -    |

| Eachta law lavel autoa width |                 | 10.24MHz crystal          | 0.40                 | _                   | μs   |

| Enable low-level pulse width | tel             | Other crystal frequencies | 4/f <sub>X'tal</sub> |                     | -    |

| Enable setup time            | t <sub>ES</sub> | 10.24MHz crystal          | 0.40                 | -                   | μs   |

|                              |                 | Other crystal frequencies | 4/f <sub>X'tal</sub> |                     | -    |

| Enable hold time             | t <sub>EH</sub> | 10.24MHz crystal          | 0.40                 | -                   | μs   |

|                              |                 | Other crystal frequencies | 4/f <sub>X'tel</sub> | -                   | -    |

|                              |                 | 10.24MHz crystal          | 0.40                 | -                   | μs   |

| Clock low-level pulse width  | tci.            | Other crystal frequencies | 4/f <sub>X'tal</sub> | -                   | -    |

|                              | •               | 10.24MHz crystal          | 0.40                 | -                   | μs   |

| Clock high-level pulse width | t <sub>СН</sub> | Other crystal frequencies | 4/i <sub>Xtal</sub>  |                     | -    |

| Lotab proposation dalou      |                 | 10.24MHz crystal          | -                    | 0.40                | μs   |

| Latch propagation delay      | t <sub>LA</sub> | Other crystal frequencies | _                    | 4/f <sub>Xtal</sub> | -    |

Note. Data transfer occurs after the crystal oscillations normalize. Data transferred before oscillations normalize will not be recognized.

No. 3889-5/12

.

### **Functional Description**

### PLL-A and PLL-B Programmable Dividers

PLL-A and PLL-B input frequency ranges are set by Mode 2 command bits FA and FB, respectively. Their divider ratios,  $N_A$  and  $N_B$ , are set by Mode 1 command bits DA0 to DA15 and DB0 to DB15, respectively.

### **Programmable Reference Divider**

The divider ratio,  $N_R$ , is set by Mode 2 command bits R0 to R13. The reference frequency is given by  $f_{XIN}/(2 \times N_R)$ .

#### **Phase Detector**

The phase detector output state as a function of the divider ratio and reference frequency is shown in Table 1.

#### Table 1. Phase detector output states

| Condition <sup>1</sup>                           | PDA1, PDB1     |

|--------------------------------------------------|----------------|

| fosc/N > fref (leading)                          | High           |

| f <sub>osc</sub> /N < f <sub>rei</sub> (lagging) | Low            |

| $f_{osc}/N = f_{ref}$ (coincident)               | High impedance |

1. N = N<sub>A</sub> for PLL-A, and N<sub>B</sub> for PLL-B

When PLL-A is unlocked,  $\overline{\text{LDA}}$  is pulled low and both PDA1 and PDA2 are active. PLL-B operates identically to PLL-A. Mode 2 command bits UL0 and UL1 set the unlock phase-error threshold, and bits UE0 and UE1, the  $\overline{\text{LDA}}$  and  $\overline{\text{LDB}}$  output extension.

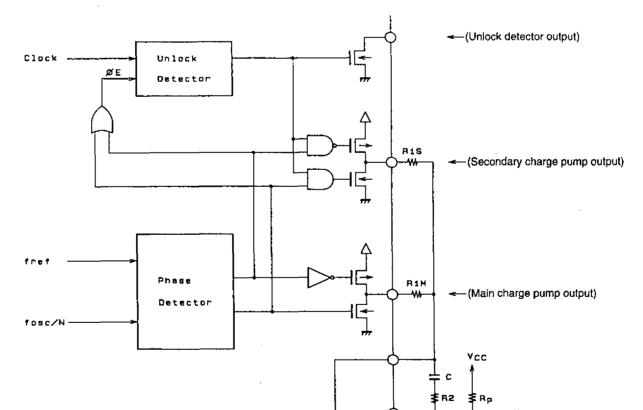

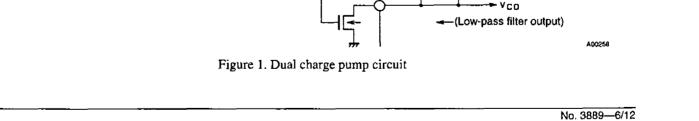

### Dual Charge Pump

A typical dual charge pump configuration is shown in Figure 1. The phase detector secondary output is active after a change in frequency, and the phase error causes the PLL to unlock. In this case, the load resistance R1 becomes  $R1M \mid R1S$ , decreasing the LPF time constant and the time required to lock the PLL.

The phase detector secondary output is high impedance when the PLL is locked. In this case, R1 becomes R1M, increasing the LPF time constant and improving sideband and modulation response.

#### Test Mode

TEST is normally held low. However, when TEST is high and test bits T0 to T2 are set to 0, the signal on  $\overline{OUTA}$  has a frequency of  $f_{Xtal}/2$ , allowing the crystal oscillator frequency to be monitored.

### Serial Input Data

Serial data should be input only after  $f_{Xtal}$  has become stable.

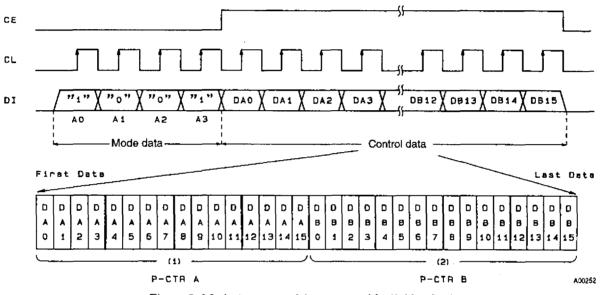

### Mode 1 command format and functions

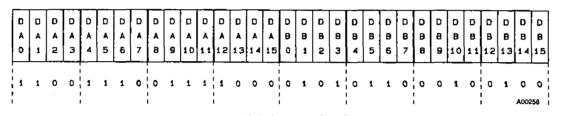

The Mode 1 command comprises the data bits which determine the PLL-A and PLL-B programmable divider ratios. The command format is shown in Figure 2. Bits DA0 to DA15 and bits DB0 to DB15 determine the PLL-A

and PLL-B programmable divider ratios, respectively. Bit DA0 is the first bit received. The range of allowable divider ratios is N = 272 (0110H) to 65535 (FFFFH).

Figure 2. Mode 1 command (programmable divider data)

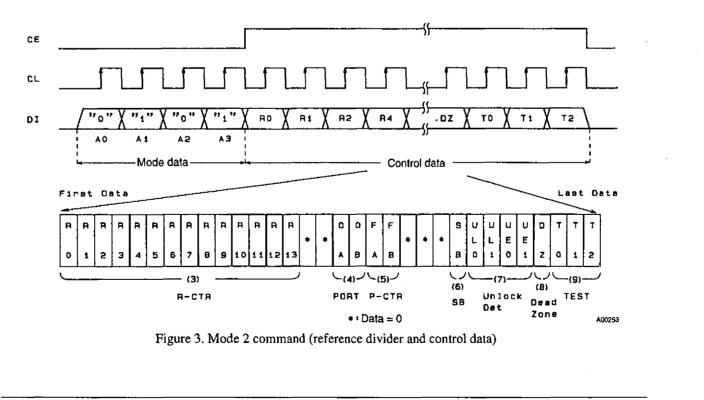

### Mode 2 command format and functions

determine the reference frequency divider ratio and con-

The Mode 2 command comprises the data bits which trol functions. The command format is shown in Figure 3. Bit R0 is the first bit received.

No. 3889-7/12

1

Bits R0 to R13 determine the reference frequency ratio. The range of allowable divider ratios is  $N_R = 8$  (0008H) to 16383 (3FFFH).

Bits OA and OB are the general-purpose output port control bits. They are latched and then inverted to control OUTA and OUTB, respectively. If either bit is 1, the opendrain output is pulled low.

Bits FA and FB are the input frequency range select bits. The PIA and PIB frequency ranges, set by FA and FB, respectively, are shown in Table 2.

Table 2. Frequency ranges

| FA<br>(FB) | Input frequency<br>range | Supply      | Device           |

|------------|--------------------------|-------------|------------------|

| 0          | 1.5 to 23.0MHz           | 2.0 to 3.3V | LC7152, 7152M    |

|            | 20 to 55MHz              | 2.0 10 3.34 | LC7152NM, 7152KM |

|            | 55 to 80MHz              | 2.7 to 3.3V | LC7152KM         |

Table 3. Unlock detector thresholds

Bit SB is the standby mode control bit. When SB = 1, standby mode is selected. In standby mode, PLL-B is stopped, PIB is pulled low, and PDB1, PDB2 and  $\overline{\text{LDB}}$  are high impedance. When SB = 0, normal operation is selected.

Bits UL0 and UL1 determine the unlock detection threshold. The PLL unlock detector output,  $\overline{\text{LDA}}$  or  $\overline{\text{LDB}}$ , is pulled low when the phase differential between the reference and the divider inputs exceeds the threshold set by UL0 and UL1. The threshold for different crystal frequencies is shown in Table 3, from which the threshold for other frequencies can be calculated. The threshold is common to both PLLs. Note that a PLL will temporarily lose lock when either UL0 or UL1 is changed.

|   | ULO UL1 | LDA, LDB phase error<br>threshold | Example phase error thresholds (μs) |                           |                         |                             |                            |  |

|---|---------|-----------------------------------|-------------------------------------|---------------------------|-------------------------|-----------------------------|----------------------------|--|

|   |         |                                   | f <sub>XIN</sub> = 4MHz             | f <sub>XIN</sub> = 7.2MHz | f <sub>XIN</sub> ≈ 8MHz | f <sub>XIN</sub> = 10.24MHz | f <sub>XIN</sub> = 12.8MHz |  |

| 0 | 0       | 0                                 | 0                                   | 0                         | 0                       | 0                           | 0                          |  |

| 1 | D       | ±4/f <sub>XIN</sub>               | ±1.00                               | ±0.55                     | ±0.50                   | ±0.39                       | ±0.31                      |  |

| 0 | 1       | ±16/f <sub>XIN</sub>              | · ±4.00                             | ±2.22                     | ±2.00                   | ±1.56                       | ±1.20                      |  |

| 1 | 1       | ±64/f <sub>XIN</sub>              | ±16.00                              | ±8.88                     | ±8.00                   | ±6.25                       | ±5.00                      |  |

Bits UE0 and UE1 determine the unlock extension, or delay, before the unlock detector outputs,  $\overline{\text{LDA}}$  and  $\overline{\text{LDB}}$ , can change state. The extension for different reference fre-

quencies is shown in Table 4. However, if a phase error threshold of zero is set using ULO and UL1, no output extension occurs.

| ULO |     | LDA, LDB output extension |                         | Example output extensions (ms | )                          |

|-----|-----|---------------------------|-------------------------|-------------------------------|----------------------------|

| ULU | UL1 | LUA, LUB output extension | f <sub>ref</sub> = 1kHz | f <sub>ret</sub> = 5kHz       | f <sub>ref</sub> = 12.5kHz |

| 0   | 0   | 4/f <sub>cot</sub>        | 4.0 <sup>1</sup>        | 0.8                           | 0.32                       |

| 1   | 0   | 8/f <sub>rof</sub>        | 8.0                     | 1.6                           | 0.64                       |

| 0   | 1   | 32/t <sub>rot</sub>       | 32.0                    | 6.4 <sup>1</sup>              | 2.56                       |

| 1   | 1   | 64/f <sub>ref</sub>       | 64.0                    | 12.8                          | 5.12 <sup>1</sup>          |

1. Typical value

Bit DZ is the dead-zone selection bit. It selects the phaseinsensitive bandwidth, or dead zone, of the phase comparator. When DZ = 1, DZB mode is selected, and when DZ = 0, DZA mode. DZB mode has a larger dead zone than Bits D0 to D2 are test bits. They should be set to for normal operation.

DZA mode.

No. 3889-8/12

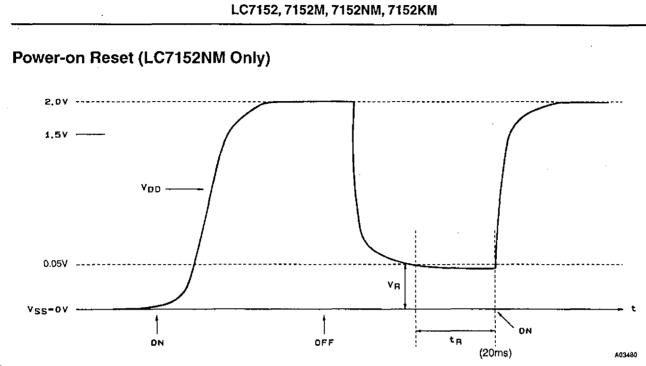

A power-on reset takes place when the supply voltage,  $V_{DD}$ , falls to a value  $V_R \le 0.05V$  for a period of  $t_R \ge 20$ ms prior to rising to a value of 2.0V or greater, as shown in Figure 4. At supply voltages above 1.5V, the latch data is retained (and a power-on reset is not required).

### Power-on reset serial data state

At power-on reset state, bits OA and OB are set to 0, which set  $\overline{OUTA}$  and  $\overline{OUTB}$  open circuit, and bit SB is set to 1.

No. 3889-9/12

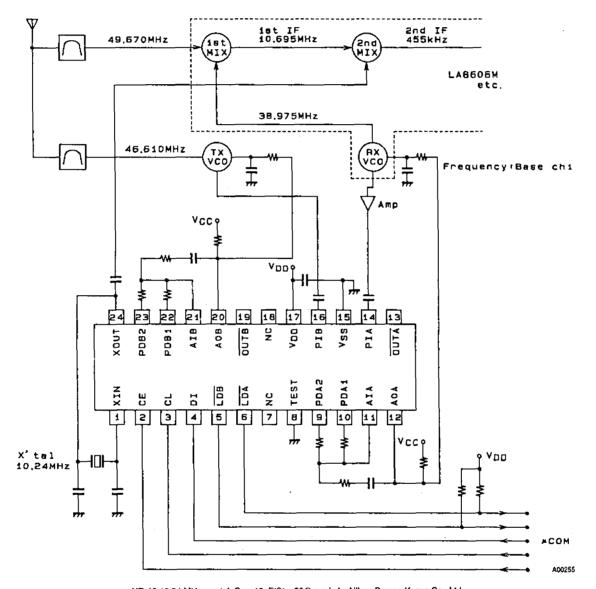

# **Typical Application**

A LC7152, 7152M, 7152NM, 7152KM cordless telephone application circuit is shown in Figure 5. The telephone is tuned to channel 1, which has a transmit VCO frequency of 46.610MHz and a receive VCO frequency of 38.975MHz.

For  $f_{ref} = 5 kHz$ , the divider ratios are as follows:

$$N_A = \frac{f_{VCO-A}}{f_{ref}} = \frac{RX VCO}{f_{ref}} = \frac{38.975 MHz}{5 kHz} = 7795 (1E73H)$$

$$N_{\rm B} = \frac{I_{\rm VCO-B}}{f_{\rm ref}} = \frac{TX \ VCO}{f_{\rm ref}} = \frac{46.610 \ MHz}{5 \ kHz} = 9322 \ (246 \ AH)$$

$$N_{\rm R} = \frac{f_{\rm Xtal}}{f_{\rm ref}} + 2 = \frac{10.24 \ MHz}{5 \ kHz} + 2 = 1024 \ (400 \ H)$$

No. 3889-10/12

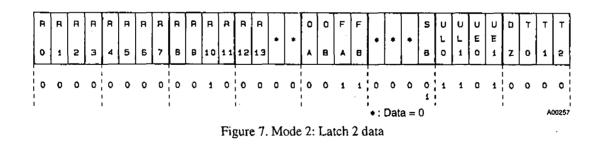

The Mode 1 and Mode 2 commands are shown in Tables 5 and 6, respectively, and in Figures 6 and 7, respectively.

Table 5. Mode 1 command

| Field       | Value | Comment                     |

|-------------|-------|-----------------------------|

| DA0 to DA15 | 1E73H | PLL-A divider ratio of 7795 |

| DB0 to DB15 | 246A  | PLL-B divider ratio of 9322 |

## Figure 6. Mode 1: Latch 1 data

Table 6. Mode 2 command

| Field                                          | Value  | Comment                                  |  |  |

|------------------------------------------------|--------|------------------------------------------|--|--|

| R0 to R13                                      | 0400H  | Reference divider ratio of 1024          |  |  |

| OA                                             | 0      |                                          |  |  |

| OB                                             | 0      | OUTA and OUTB left open.                 |  |  |

| FA                                             | 1      | 20 to 55MHz RX VCO input frequency range |  |  |

| FB                                             | 1      | 20 to 55MHz TX VCO input frequency range |  |  |

| SB                                             | 0 or 1 | Standby mode selection                   |  |  |

| UL0, UL1 11                                    |        | ±6.25µs lock/unlock detection threshold  |  |  |

| UE0, EU1 01 6.4ms LDA and LDB output extension |        | 6.4ms LDA and LDB output extension       |  |  |

| DZ 1 DZB dead-zone mode                        |        | DZB dead-zone mode                       |  |  |

| T0 to T2 000                                   |        | Test mode deselected                     |  |  |

No. 3889-11/12

# **Device Comparison**

|          | Operating frequency |             |                                        |                        |         |

|----------|---------------------|-------------|----------------------------------------|------------------------|---------|

| Device   | FA/FB = 0           | FA/FB = 1   |                                        | Power-on reset circuit | Package |

|          | 1.5 to 23MHz        | 20 to 55MHz | 55 to 80MHz                            | 1                      |         |

| LC7152   | Yes                 | Yes         | No                                     | No                     | DIP24S  |

| LC7152M  | Yes                 | Yes         | No                                     | No                     | MFP24S  |

| LC7152NM | Yes                 | Yes         | No                                     | Yes                    | MFP24S  |

| LC7152KM | Yes                 | Yes         | Yes<br>(V <sub>DD</sub> = 2.7 to 3.3V) | No                     | MFP24S  |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees, jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of April, 1995. Specifications and information herein are subject to change without notice.

No. 3889-12/12

1