# **Closed Caption Signal Extraction IC**

#### Overview

The LC7455A/M extracts the closed caption signal superimposed on a video signal during the vertical return period and, under the control of a clock signal provided by the decoder IC, transfers that signal to the IC (usually a microcontroller) that decodes the closed caption data. The LC7455A/M supports four operating modes. Modes 1 and 2 can be used for XDS. In these modes, the LC7455A/M, in combination with the decoder IC (microcontroller), extracts the caption signal superimposed on field 2 and uses it for NTSC VCR functions such as the automatic time and date setting function. In modes 3 and 4, the LC7455A/M, in combination with the decoder IC (microcontroller), extracts the caption signal superimposed on fields 1 and 2 and uses it for NTSC TV applications (mode 3) or PAL TV applications (mode 4).

#### **Functions**

- Low power dissipation achieved by fabrication in a CMOS process.

- Stable caption signal extraction achieved by a built-in peak hold circuit and the use of digital technology.

- Operating supply voltage: 5 V ±10%

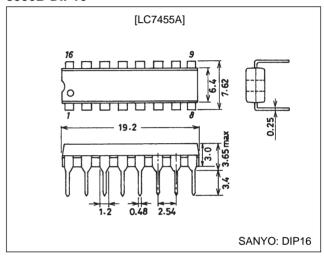

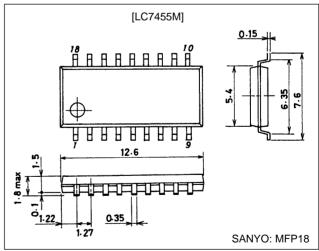

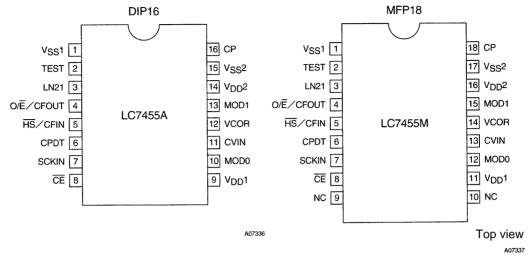

Package LC7455A: 16-pin DIP LC7455M: 18-pin MFP

#### **Package Dimensions**

unit: mm

#### 3006B-DIP16

unit: mm

#### 3095-MFP18

#### **Pin Assignments**

#### **Pin Functions**

|                   | Pin No. |       | Pin function                                                                                          |                                                     |                                   |                                     |  |  |

|-------------------|---------|-------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------|-------------------------------------|--|--|

| Pin               | DIP16   | MFP18 | Mode 1                                                                                                | Mode2                                               | Mode3                             | Mode4                               |  |  |

| V <sub>SS</sub> 1 | 1       | 1     | Ground                                                                                                |                                                     |                                   |                                     |  |  |

| TEST              | 2       | 2     | Test pin. Must be left open du                                                                        | est pin. Must be left open during normal operation. |                                   |                                     |  |  |

| LN21              | 3       | 3     | Line 21H pulse output (even field)  Line 21H pulse output (both fields)  Line 22H pulse (both fields) |                                                     |                                   | Line 22H pulse output (both fields) |  |  |

| O/E/CFOUT         | 4       | 4     | Field discrimination pulse output                                                                     | Ceramic oscillator output                           | Field discrimination pulse output |                                     |  |  |

| HS/CFIN           | 5       | 5     | Sync separator Hsync pulse output                                                                     | Ceramic oscillator input                            | Hsync pulse input                 |                                     |  |  |

| CPDT              | 6       | 6     | Caption data output (n-channel open-drain output)                                                     |                                                     |                                   |                                     |  |  |

| SCKIN             | 7       | 7     | Caption data transfer clock in                                                                        | Caption data transfer clock input                   |                                   |                                     |  |  |

| CE                | 8       | 8     | Chip select input                                                                                     |                                                     |                                   |                                     |  |  |

| V <sub>DD</sub> 1 | 9       | 11    | Power supply                                                                                          |                                                     |                                   |                                     |  |  |

| MOD0              | 10      | 12    | Leave open                                                                                            | Short to the power supply                           | Leave open                        | Short to the power supply           |  |  |

| CVIN              | 11      | 13    | Composite video input                                                                                 |                                                     |                                   |                                     |  |  |

| VCOR              | 12      | 14    | Connection for an external res                                                                        | sistor to control the built-in VC                   | O oscillator frequency            |                                     |  |  |

| MOD1              | 13      | 15    | Leave open                                                                                            |                                                     | Short to the power supply         |                                     |  |  |

| V <sub>DD</sub> 2 | 14      | 16    | Power supply                                                                                          |                                                     |                                   |                                     |  |  |

| V <sub>SS</sub> 2 | 15      | 17    | Ground                                                                                                |                                                     |                                   |                                     |  |  |

| СР                | 16      | 18    | Connection for the filter used by the built-in PLL                                                    |                                                     |                                   |                                     |  |  |

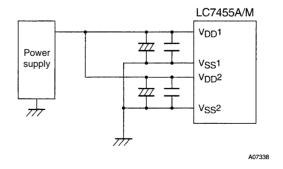

Note: V<sub>DD</sub>1 and V<sub>SS</sub>1 are the power supply for the digital block, and V<sub>DD</sub>2 and V<sub>SS</sub>2 are the power supply for the analog block. Use a circuit similar to the one shown below to minimize mutual interference due to noise from these blocks.

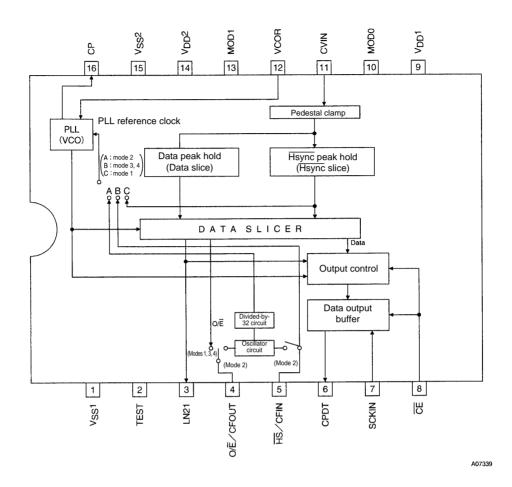

#### **System Block Diagram**

## **Operation in the Different Modes**

| Pin             |                 | Mode   | Application equipment | Operation                                                                                                                                                                                                    |

|-----------------|-----------------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOD1            | MOD0            |        | equipment             |                                                                                                                                                                                                              |

| Open            | Open            | Mode 1 | VCR                   | <ul> <li>Even field line 21 data extraction</li> <li>The internal PLL is operated with the horizontal synchronizing signal separated from the composite video signal as the reference.</li> </ul>            |

| Open            | V <sub>DD</sub> | Mode 2 | VCR                   | <ul> <li>Even field line 21 data extraction</li> <li>An external 508 kHz ceramic oscillator is used, and the internal PLL is operated with that oscillator output divided by 32 as the reference.</li> </ul> |

| V <sub>DD</sub> | Open            | Mode 3 | NTSC-TV               | Odd and even field line 21 data extraction     The internal PLL is operated with the Hsync signal applied from fly back as the reference.                                                                    |

| V <sub>DD</sub> | V <sub>DD</sub> | Mode 4 | PAL-TV                | Odd and even field line 22 data extraction     The internal PLL is operated with the Hsync signal applied from the fly back circuit as the reference.                                                        |

Note: The data extraction operations in modes 1 and 2 are identical. However, while mode 1 can operate without problem for normal "on air" signals, it may be difficult for the PLL to lock with signals such as scrambled CATV signals.

# **Specifications**

# Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS} = 0$ V

| Parameter                   | Parameter Symbol Conditions |                                             | Ratings                      | Unit |

|-----------------------------|-----------------------------|---------------------------------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max         | $V_{DD}1$ , $V_{DD}2$ : $V_{DD}1 = V_{DD}2$ | -0.3 to +7.0                 | V    |

| Input voltage               | VI                          | HS/CFIN, CVIN, SCKIN, CE                    | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage              | Vo                          | LN21, CPDT, O/E/CFOUT, HS/CFIN              | -0.3 to V <sub>DD</sub> +0.3 | V    |

|                             |                             | LC7455A                                     | 300                          | mW   |

| Allowable power dissipation | Pd max                      | LC7455M                                     | 150                          | mW   |

| Operating temperature       | Topr                        |                                             | -30 to +70                   | °C   |

| Storage temperature         | Tstg                        |                                             | -55 to +150                  | °C   |

Note:  $V_{SS}1$  and  $V_{SS}2$  must be at the same potential.  $V_{DD}1$  and  $V_{DD}2$  must be at the same potential.

# Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}, V_{SS} = 0 \text{ V}$

| Parameter                       | Symbol          | Conditions                                                                                                           | Ratings              |                |                     | Unit       |  |

|---------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|---------------------|------------|--|

| Parameter                       | Symbol          |                                                                                                                      | min                  | typ            | max                 | Oill       |  |

| Operating supply voltage        | V <sub>DD</sub> | $V_{DD}$ $V_{DD}1$ , $V_{DD}2$ : $V_{DD}1 = V_{DD}2$                                                                 |                      |                | 5.5                 | V          |  |

| Input high-level voltage        | V <sub>IH</sub> | $\overline{\text{HS}}/\text{CFIN}$ , SCKIN, $\overline{\text{CE}}$ ;<br>V <sub>DD</sub> = 4.5 to 5.5 V               | 0.75 V <sub>DD</sub> |                | V <sub>DD</sub>     | V          |  |

| Input low-level voltage         | V <sub>IL</sub> | $\overline{\text{HS}}/\text{CFIN}$ , SCKIN, $\overline{\text{CE}}$ ; $V_{\text{DD}} = 4.5 \text{ to } 5.5 \text{ V}$ | V <sub>SS</sub>      |                | 0.25V <sub>DD</sub> | ٧          |  |

| CVIN input amplitude            | CVSYNC          | CVIN : SYNC-WHITE = 1.0 V;<br>V <sub>DD</sub> = 4.5 to 5.5 V                                                         | 1Vp-p – 3dB          | 1Vp-p          | 1Vp-p + 3 dB        | V          |  |

| HS input frequency range        | fH              | HS/CFIN: V <sub>DD</sub> = 4.5 V<br>For mode 3<br>For mode 4                                                         | 15.23<br>15.13       | 15.73<br>15.63 | 16.23<br>16.13      | kHz<br>kHz |  |

| Oscillator frequency range*1    | FmCF            | HS/CFIN, O/E/CFOUT;<br>For mode 2, see Figure 1.<br>V <sub>DD</sub> = 4.5 to 5.5 V                                   | 503                  | 508            | 513                 | kHz        |  |

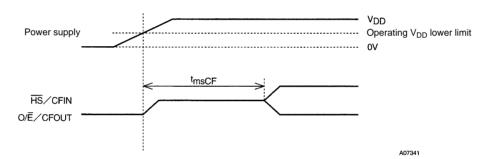

| Oscillator stabilization time*2 | tmsCF           | HS/CFIN, O/E/CFOUT;<br>For mode 2, see Figure 2.<br>V <sub>DD</sub> = 4.5 to 5.5 V                                   |                      | 0.5            | 5                   | ms         |  |

Note: 1. See Table 1 for more information on the oscillator frequency.

## Electrical Characteristics at Ta = -30 to +70°C, $V_{SS} = 0$ V.

| Parameter                                                                                                                                                            | Symbol            | Conditions                                                                                                                                            | Ratings               |     |     | Unit  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-------|--|

| Parameter                                                                                                                                                            | Symbol            | Conditions                                                                                                                                            | min                   | typ | max | Offic |  |

| Input high-level current                                                                                                                                             | Іін               | H $\overline{\text{HS}}/\text{CFIN}$ , SCKIN, $\overline{\text{CE}}: V_{\text{IN}} = V_{\text{DD}}$ ; $V_{\text{DD}} = 4.5 \text{ to } 5.5 \text{ V}$ |                       |     | 1   | μА    |  |

| Input low-level current                                                                                                                                              | I <sub>IL</sub>   | $\overline{\text{HS}}/\text{CFIN}$ , SCKIN, $\overline{\text{CE}}$ : $V_{\text{IN}} = V_{\text{SS}}$ ; $V_{\text{DD}} = 4.5$ to 5.5 V                 | -1                    |     |     | μA    |  |

| Output high-level voltage                                                                                                                                            | V <sub>OH</sub>   | LN21, O/E/CFOUT, HS/CFIN;<br>I <sub>OH</sub> = -4 mA; V <sub>DD</sub> = 4.5 to 5.5 V                                                                  | V <sub>DD</sub> – 1.2 |     |     | V     |  |

| Output low-level voltage $ V_{OL} = \frac{LN21, CPDT, O/\overline{E}/CFOUT,}{\overline{HS}/CFIN: I_{OL} = 10 \text{ mA; } V_{DD} = 4.5 \text{ to } 5.5 \text{ V} } $ |                   |                                                                                                                                                       |                       | 1   | V   |       |  |

| Input clamping voltage                                                                                                                                               | V <sub>CLMP</sub> | CVIN ; V <sub>DD</sub> = 5.0 V                                                                                                                        | 2.3                   | 2.5 | 2.7 | V     |  |

| Input clamping current                                                                                                                                               | I <sub>IC</sub>   | CVIN : CVIN = 3 V ; V <sub>DD</sub> = 5.0 V                                                                                                           | 5                     | 10  | 18  | μA    |  |

| Output clamping current I <sub>OC</sub> CVIN : CVIN = 2 V ; V <sub>D</sub>                                                                                           |                   | CVIN : CVIN = 2 V ; V <sub>DD</sub> = 5.0 V                                                                                                           | -120                  | -70 | -30 | μA    |  |

| Current drain                                                                                                                                                        | I <sub>DD</sub>   | $V_{DD}1$ , $V_{DD}2$ ; $V_{DD} = 4.5$ to 5.5 V                                                                                                       |                       | 6   | 15  | mA    |  |

# Serial Output Characteristics at $Ta=-30~to~+70^{\circ}C,\,V_{SS}=0~V,\,V_{DD}=4.5~to~5.5~V$

| Parameter                                                                                                                                | Symbol Conditions |                                                                                                                    |     | Linit |     |      |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Parameter                                                                                                                                |                   |                                                                                                                    | min | typ   | max | Unit |

| [Serial clock]                                                                                                                           |                   |                                                                                                                    |     |       |     |      |

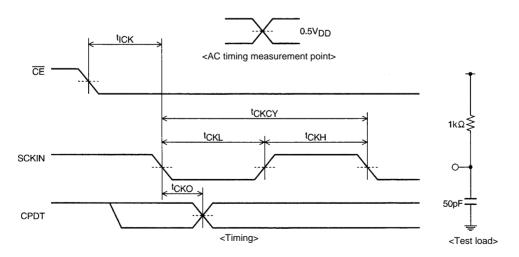

| Input clock period                                                                                                                       | tckcy             | SCKIN : See Figure 3.                                                                                              | 1   |       |     | μs   |

| Input clock low-level pulse width                                                                                                        | t <sub>CKL</sub>  | SCKIN : See Figure 3.                                                                                              | 0.5 |       |     | μs   |

| Input clock high-level pulse width                                                                                                       | t <sub>CKH</sub>  | SCKIN : See Figure 3.                                                                                              | 0.5 |       |     | μs   |

| Setup time $t_{ICK} \hspace{0.5cm} \text{SCKIN}: \text{Stipulated with respect to the falling} \\ \text{edge of } \overline{\text{CE}}.$ |                   | 1                                                                                                                  |     |       | μs  |      |

| [Serial output]                                                                                                                          |                   |                                                                                                                    |     |       |     |      |

| Output delay time                                                                                                                        | tско              | Stipulated with respect to the falling edge of SCKIN. A 1-kΩ external pull-up resistor is connected. See Figure 3. |     |       | 0.5 | μs   |

<sup>2.</sup> The oscillator stabilization time is the time required until the oscillator is stable after the power-supply voltage is applied. See figure 2.

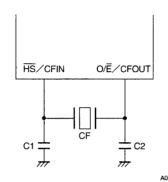

**Table 1 Ceramic Oscillator Guaranteed Constants**

| Oscillator type            | Manufacturer          | Oscillator element | C1     | C2     |   |

|----------------------------|-----------------------|--------------------|--------|--------|---|

| 508-kHz ceramic oscillator | Murata Mfg. Co., Ltd. | CSB 508E           | 150 pF | 150 pF | 1 |

Note: Capacitors with K tolerance (±10%) and SL characteristics must be used for C1 and C2.

- Since this circuit is influenced by the length of the circuit pattern, components related to oscillator functioning must be mounted as close together as possible so that pattern lines do not become longer than is absolutely necessary.

- · The characteristics are not guaranteed if an oscillator element other than the one listed above is used.

Figure 1 Ceramic Oscillator

Figure 2 Oscillator Stabilization Time

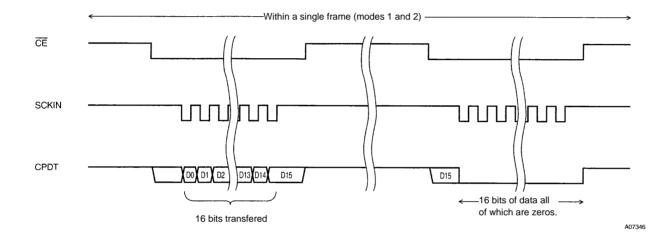

Note: CPDT goes to the high-impedance state while  $\overline{\text{CE}}$  is high.

Figure 3 Serial Output Test Conditions

No. 5680-5/13

A07342

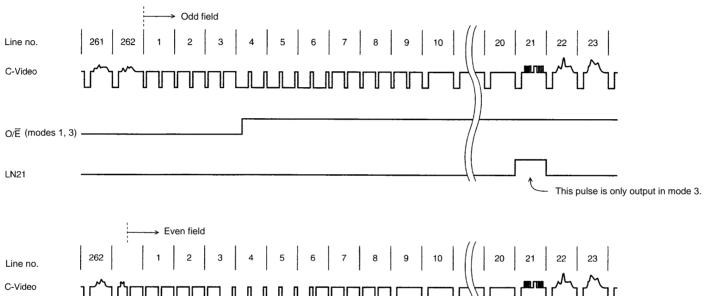

#### O/E and LN21 Output Timing (Modes 1, 2, and 3)

C-Video

O/Ē (modes 1, 3)

LN21

This pulse is only output in modes 1, 2, and 3.

A07343

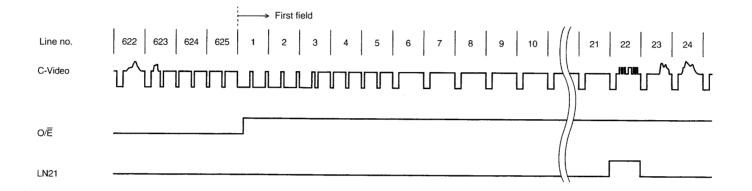

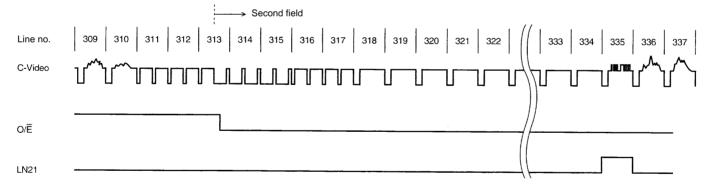

## O/E and LN21 Output Timing (Mode 4)

A07344

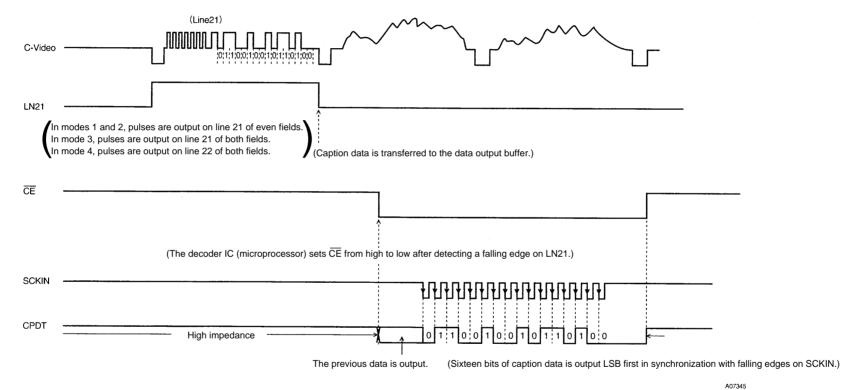

# Caption Data Transfer from the LC7455A/M to the Decoder IC (microcontroller): Method 1 (This is the basic technique.)

#### Caption Data Transfer from the LC7455A/M to the Decoder IC (microcontroller): Method 2

(For applications that cannot provide an input port on the decoder IC (microcontroller) to detect LN21 falling edges.)

In modes 1 and 2, since data is output to the output buffer once every frame (in the even field), the decoder IC (microcontroller) must perform a transfer control operation at least twice every frame (about 32 ms).

When the second control operation is performed in a given frame, the CPDT output for that second operation will be 16 bits of zeros. This allows the microprocessor to recognize that the data for the next frame has not yet been transferred to the output buffer.

Notes: When  $\overline{\mathsf{CE}}$  remains low, the hardware will not transfer the data to the output buffer. Thus applications must restore  $\overline{\mathsf{CE}}$  from low to high after each data transfer to the decoder IC (microcontroller) operation has completed. This transfer technique (method 2) cannot be used in modes 3 and 4.

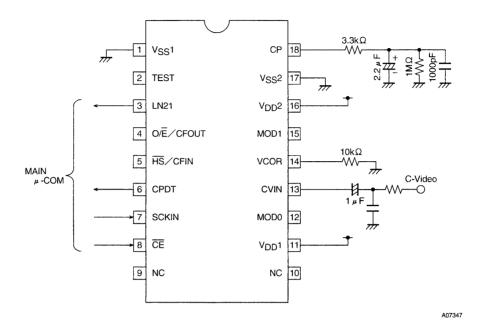

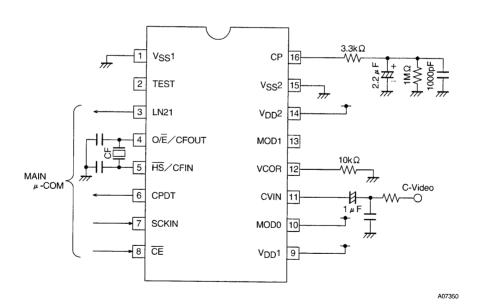

## **Sample Application Circuits (mode 1)**

#### MFP18

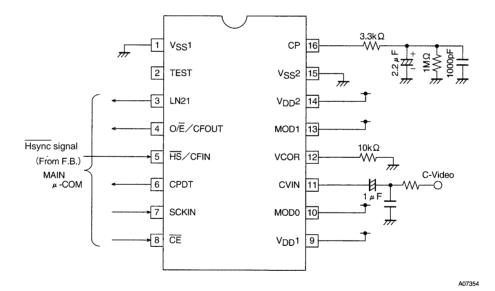

## DIP16

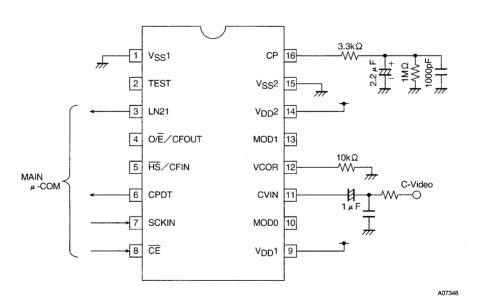

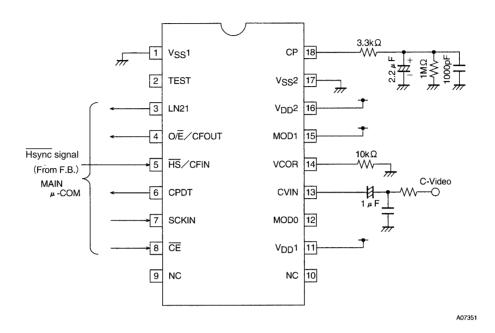

## **Sample Application Circuits (mode 2)**

#### MFP18

## DIP16

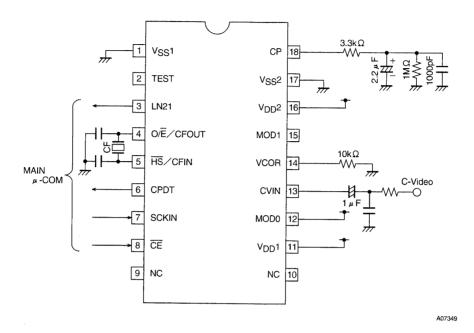

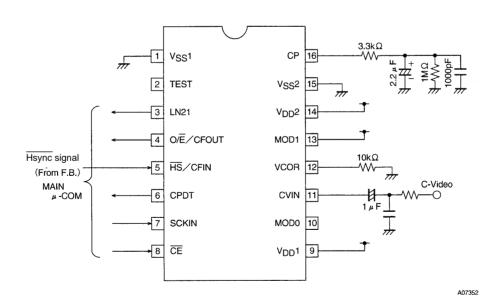

## **Sample Application Circuits (mode 3)**

#### MFP18

## DIP16

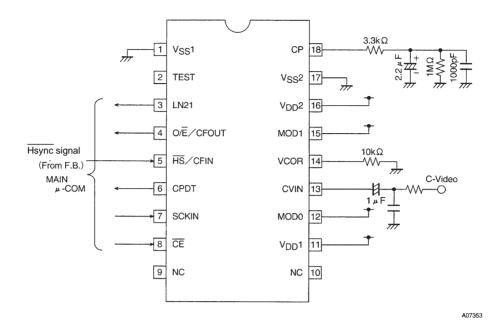

#### Sample Application Circuits (mode 4)

#### MFP18

DIP16

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.