# LM3433 Common Anode Capable High Brightness LED Driver with High Frequency Dimmina

Check for Samples: LM3433

## **FEATURES**

- Operating input voltage range of -9V to -14V w.r.t. LED anode

- Control inputs are referenced to the LED anode

- Output current greater than 6A

- Greater than 30kHz PWM frequency capable

- Negative output voltage capability allows LED anode to be tied directly to chassis for maximum heat sink efficacy

- No output capacitor required

- Up to 1MHz switching frequency

- Low I<sub>o</sub>, 1mA typical

- Soft start

- Adaptive programmable ON time allows for constant ripple current

- 24-pin WQFN package

## APPLICATIONS

- LCD backlighting

- **Projection systems**

- Solid state lighting

- Automotive lighting

## DESCRIPTION

The LM3433 is an adaptive constant on-time DC/DC buck (step-down) constant current controller (a true current source). The LM3433 provides a constant current for illuminating high power LEDs. The output configuration allows the anodes of multiple LEDs to be tied directly to the ground referenced chassis for maximum heat sink efficacy. The high frequency capable architecture allows the use of small external passive components and no output capacitor while maintaining low LED ripple current. Two control inputs are used to modulate LED brightness. An analog current control input is provided so the LM3433 can be adjusted to compensate for LED manufacturing variations and/or color temperature correction. The other input is a logic level PWM control of LED current. The PWM functions by shorting out the LED with a parallel switch allowing high PWM dimming frequencies. High frequency PWM dimming allows digital color temperature control, interference blanking, field sequential illumination, and brightness control. Additional features include thermal shutdown, V<sub>CC</sub> under-voltage lockout, and logic level shutdown mode. The LM3433 is available in a low profile 24-pin WQFN package.

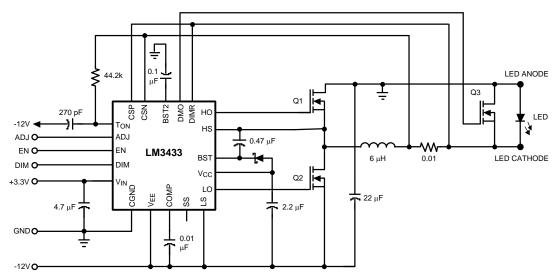

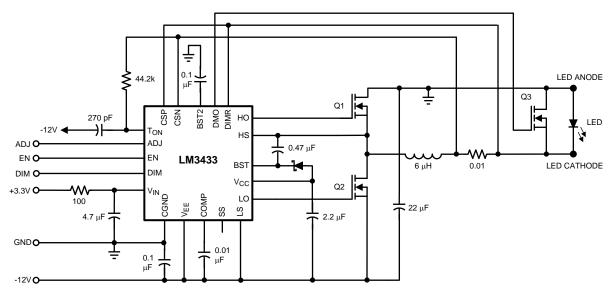

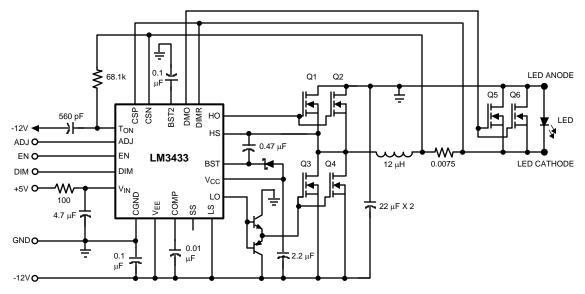

TYPICAL APPLICATION CIRCUIT

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

## LM3433

#### SNVS535B-OCTOBER 2007-REVISED MARCH 2008

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

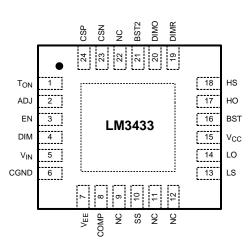

## **CONNECTION DIAGRAM**

**Top View**

#### Figure 1. 24-Lead QFN See RTW Package

### **PIN DESCRIPTIONS**

| Pin | Name            | Function                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | T <sub>ON</sub> | On-time programming pin. Tie an external resistor ( $R_{ON}$ ) from $T_{ON}$ to CSN, and a capacitor ( $C_{ON}$ ) from $T_{ON}$ to $V_{EE}$ . This sets the nominal operating frequency when the LED is fully illuminated.                                                                                                                                                                    |

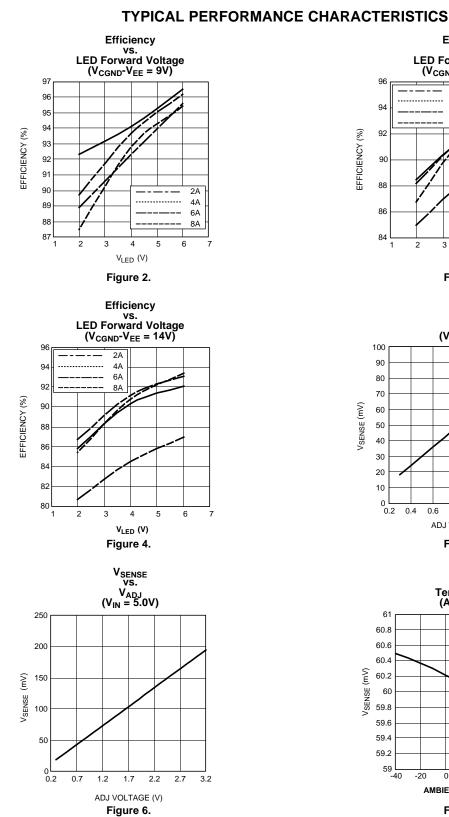

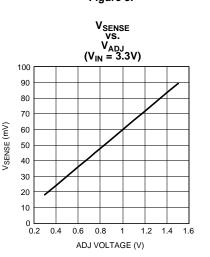

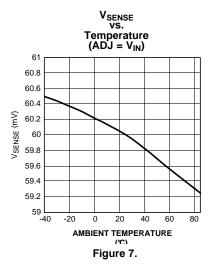

| 2   | ADJ             | Analog LED current adjust. Tie to $V_{IN}$ for fixed 60mV average current sense resistor voltage. Tie to an external reference to adjust the average current sense resistor voltage (programmed output current). Refer to the "V <sub>SENSE</sub> vs. ADJ Voltage" graphs in the <i>Typical Performance Characteristics</i> section and the <i>Design Procedure</i> section of the datasheet. |

| 3   | EN              | Enable pin. Connect this pin to logic level HI or $V_{IN}$ for normal operation. Connect this pin to CGND for low current shutdown. EN is internally tied to $V_{IN}$ through a 100k resistor.                                                                                                                                                                                                |

| 4   | DIM             | Logic level input for LED PWM dimming. DIM is internally tied to CGND through a 100k resistor.                                                                                                                                                                                                                                                                                                |

| 5   | V <sub>IN</sub> | Logic power input: Connect to positive voltage between +3.0V and +5.8V w.r.t. CGND.                                                                                                                                                                                                                                                                                                           |

| 6   | CGND            | Chassis ground connection.                                                                                                                                                                                                                                                                                                                                                                    |

| 7   | $V_{EE}$        | Negative voltage power input: Connect to voltage between -14V to -9V w.r.t. CGND.                                                                                                                                                                                                                                                                                                             |

| 8   | COMP            | Compensation pin. Connect a capacitor between this pin and $V_{\text{EE}}$ .                                                                                                                                                                                                                                                                                                                  |

| 9   | NC              | No internal connection. Tie to V <sub>EE</sub> or leave open.                                                                                                                                                                                                                                                                                                                                 |

| 10  | SS              | Soft Start pin. Tie a capacitor from SS to $V_{EE}$ to reduce input current ramp rate. Leave pin open if function is not used. The SS pin is pulled to $V_{EE}$ when the device is not enabled.                                                                                                                                                                                               |

| 11  | NC              | No internal connection. Tie to V <sub>EE</sub> or leave open.                                                                                                                                                                                                                                                                                                                                 |

| 12  | NC              | No internal connection. Tie to V <sub>EE</sub> or leave open.                                                                                                                                                                                                                                                                                                                                 |

| 13  | LS              | Low side FET gate drive return pin.                                                                                                                                                                                                                                                                                                                                                           |

| 14  | LO              | Low side FET gate drive output. Low in shutdown.                                                                                                                                                                                                                                                                                                                                              |

| 15  | V <sub>CC</sub> | Low side FET gate drive power bypass connection and boost diode anode connection. Tie a 2.2 $\mu$ F capacitor between V <sub>CC</sub> and V <sub>EE</sub> .                                                                                                                                                                                                                                   |

| 16  | BST             | High side "synchronous" FET drive bootstrap rail.                                                                                                                                                                                                                                                                                                                                             |

| 17  | HO              | High side "synchronous" FET gate drive output. Pulled to HS in shutdown.                                                                                                                                                                                                                                                                                                                      |

| 18  | HS              | Switching node and high side "synchronous" FET gate drive return.                                                                                                                                                                                                                                                                                                                             |

SNVS535B-OCTOBER 2007-REVISED MARCH 2008

## **PIN DESCRIPTIONS (continued)**

| Pin | Name            | Function                                                                                                        |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------|

| 19  | DIMR            | LED dimming FET gate drive return. Tie to LED cathode.                                                          |

| 20  | DIMO            | LED dimming FET gate drive output. DIMO is a driver that switches between DIMR and BST2.                        |

| 21  | BST2            | DIMO high side drive supply pin. Tie a 0.1µF between BST2 and CGND.                                             |

| 22  | NC              | No internal connection. Tie to V <sub>EE</sub> or leave open.                                                   |

| 23  | CSN             | Current sense amplifier inverting input. Connect to current sense resistor negative terminal.                   |

| 24  | CSP             | Current sense amplifier non-inverting input. Connect to current sense resistor positive terminal.               |

| EP  | V <sub>EE</sub> | Exposed Pad on the underside of the device. Connect this pad to a PC board plane connected to V <sub>EE</sub> . |

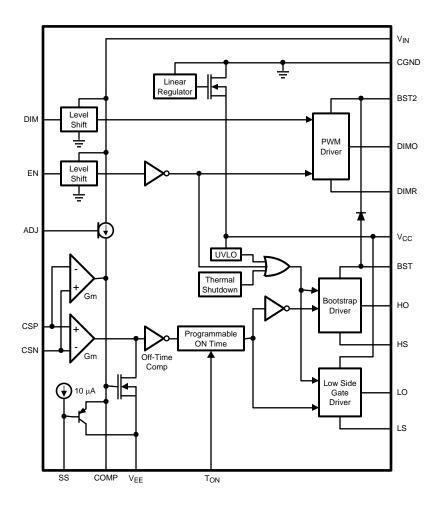

## **BLOCK DIAGRAM**

#### ABSOLUTE MAXIMUM RATINGS (1)

|                                                          | VALUE / UNIT              |

|----------------------------------------------------------|---------------------------|

| V <sub>IN</sub> , EN, DIM, ADJ to CGND                   | -0.3V to +7V              |

| COMP, SS to V <sub>EE</sub>                              | -0.3V to +7V              |

| BST to HS                                                | -0.3V to +7V              |

| V <sub>CC</sub> to V <sub>EE</sub>                       | -0.3V to +7.5V            |

| CGND, DIMR, CSP, CSN, T <sub>ON</sub> to V <sub>EE</sub> | -0.3V to +16V             |

| HS to $V_{EE}^{(2)}$                                     | -0.3V to +16V             |

| LS to V <sub>EE</sub>                                    | -0.3V to +0.3V            |

| HO output                                                | HS-0.3V to BST+0.3V       |

| DIMO to DIMR                                             | -0.3V to +7V              |

| LO output                                                | LS-0.3V to $V_{CC}$ +0.3V |

| BST2 to V <sub>EE</sub>                                  | -0.3V to 22.0V            |

| Maximum Junction Temperature                             | 150°C                     |

| Power Dissipation <sup>(3)</sup>                         | Internally Limited        |

| ESD Susceptibility <sup>(4)</sup>                        |                           |

| Human Body Model                                         | 2kV                       |

| Machine Model                                            | 200V                      |

| Charge Device Model                                      | 1kV                       |

(1) Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may **not be** guaranteed. For specified specifications and test conditions, see the Electrical Characteristics.

(2) The HS pin can go to -6V with respect to V<sub>EE</sub> for 30ns and +22V with respect to V<sub>EE</sub> for 50ns without sustaining damage.

(3) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is calculated using: P<sub>D</sub> (MAX) = (T<sub>J</sub>(MAX) - T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub>=175°C (typ.) and disengages at T<sub>J</sub>=155°C (typ).

(4) Human Body Model, applicable std. JESD22-A114-C. Machine Model, applicable std. JESD22-A115-A. Field Induced Charge Device Model, applicable std. JESD22-C101-C.

## **REOMMENDED OPERATING CONDITIIONS**

|                                                     | VALUE / UNIT          |

|-----------------------------------------------------|-----------------------|

| Operating Junction Temperature Range <sup>(1)</sup> | −40°C to +125°C       |

| Storage Temperature                                 | −65°C to +150°C       |

| Input Voltage V <sub>IN</sub> w.r.t. CGND           | 3.0V to 5.8V          |

| Input Voltage V <sub>EE</sub> w.r.t. CGND           | -9V to -14V           |

| ADJ Input Voltage Range to CGND                     | 0V to V <sub>IN</sub> |

| CSP, CSN Common Mode Range With Respect to CGND     | -6V to 0V             |

(1) All limits specified at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are 100% production tested. All limits at temperature extremes are ensured via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

SNVS535B-OCTOBER 2007-REVISED MARCH 2008

www.ti.com

## **ELECTRICAL CHARACTERISTICS**

Specifications in standard type face are for  $T_J = 25^{\circ}$ C and those with **boldface type** apply over the full **Operating Temperature Range** ( $T_J = -40^{\circ}$ C to +125°C). Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = +25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{EE} = -12.0$ V and  $V_{IN} = +3.3$ V with respect to CGND.

| Symbol                          | Parameter                                                                                 | Conditions                                                    | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units |

|---------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------|--------------------|--------------------|-------|

| SUPPLY                          | CURRENT                                                                                   |                                                               |                    |                    |                    |       |

| I <sub>IN</sub> V <sub>EE</sub> | V <sub>EE</sub> Quiescent Current                                                         | EN = CGND                                                     |                    | 3                  | 19                 | μA    |

|                                 |                                                                                           | EN = V <sub>IN</sub> , Not Switching                          |                    | 1.0                |                    | mA    |

| I <sub>IN</sub> V <sub>IN</sub> | VIN Quiescent Current                                                                     | EN = V <sub>IN</sub> , Not Switching                          |                    | 300                |                    |       |

|                                 |                                                                                           | EN = CGND                                                     |                    | 35                 | 71                 | μA    |

| OUTPUT                          | CURRENT CONTROL                                                                           |                                                               |                    |                    |                    |       |

| V <sub>CS</sub>                 | Current sense target voltage;<br>$V_{CS} = V_{CSP} - V_{CSN}$                             | $V_{ADJ} = V_{IN}$                                            | 57                 | 60                 | 63                 | mV    |

| G <sub>ADJ</sub>                | $I_{ADJ}$ Gain = ( $V_{ADJ}$ -CGND)/( $V_{CNP}$ - $V_{CSN}$ )                             | $V_{IN}$ = 3.3V, $V_{ADJ}$ = 0.5V or 1.5V w.r.t. CGND         | 15                 | 16.67              | 18                 | V/V   |

| I <sub>CSN</sub>                | Isense Input Current                                                                      | V <sub>ADJ</sub> = 1V w.r.t. CGND                             |                    | -50                |                    |       |

|                                 |                                                                                           | $V_{ADJ} = V_{IN}$                                            |                    | 10                 |                    | μA    |

| I <sub>CSP</sub>                | Isense Input Current                                                                      | $V_{ADJ} = V_{IN}$                                            |                    | 60                 |                    |       |

|                                 |                                                                                           | V <sub>ADJ</sub> = 1V w.r.t. CGND                             |                    | 1                  |                    | μA    |

| Gm                              | CS to COMP Transconductance; Gm = $I_{COMP}$<br>/ ( $V_{CSP} - V_{CSN} - V_{ADJ}/16.67$ ) |                                                               | 0.6                | 1.3                | 2.2                | mS    |

| ON TIME                         | CONTROL                                                                                   |                                                               |                    |                    |                    |       |

| T <sub>ONTH</sub>               | On time threshold                                                                         | $V_{\text{Ton}}$ - $V_{\text{EE}}$ at terminate ON time event | 230                | 287                | 334                | mV    |

| GATE DR                         | IVE AND INTERNAL REGULATOR                                                                | •                                                             | <u>.</u>           | *                  |                    |       |

| V <sub>CCOUT</sub>              | V <sub>CC</sub> output regulation w.r.t. V <sub>EE</sub>                                  | I <sub>CC</sub> = 0mA to 20mA                                 | 6.3                | 6.75               | 7.1                | V     |

| V <sub>CCILIM</sub>             | V <sub>CC</sub> current limit                                                             | $V_{CC} = V_{EE}$                                             | 33                 | 53                 |                    | mA    |

| R <sub>OLH</sub>                | HO output low resistance                                                                  | I = 50mA source                                               |                    | 2                  |                    | 0     |

| R <sub>OHH</sub>                | HO output high resistance                                                                 | I = 50mA sink                                                 |                    | 3                  |                    | Ω     |

| R <sub>OLL</sub>                | LO output low resistance                                                                  | I = 50mA source                                               |                    | 2                  |                    | 0     |

| R <sub>OHL</sub>                | LO output high resistance                                                                 | I = 50mA sink                                                 |                    | 3                  |                    | Ω     |

| R <sub>OLP</sub>                | DIMO output low resistance                                                                | I = 5mA source                                                |                    | 20                 |                    | -     |

| R <sub>OHP</sub>                | DIMO output high resistance                                                               | I = 5mA sink                                                  |                    | 30                 |                    | Ω     |

|                                 | NAL CONTROL                                                                               | 1                                                             | I                  | 1                  | 1 1                |       |

| V <sub>INUVLO</sub>             | V <sub>IN</sub> undervoltage lockout                                                      | With respect to CGND                                          |                    | 1.4                |                    | V     |

| V <sub>CCUVLO</sub>             | V <sub>CC</sub> - V <sub>EE</sub> undervoltage lockout thresholds                         | On Threshold                                                  | 6.0                | 6.6                | 7.0                |       |

|                                 |                                                                                           | Off threshold                                                 | 4.9                | 5.4                | 5.8                | V     |

| V <sub>EN</sub>                 | Enable threshold, with respect to CGND                                                    | Device on w.r.t. CGND                                         |                    | 1                  | 1.6                |       |

|                                 |                                                                                           | Device off w.r.t. CGND                                        | 0.6                |                    |                    | V     |

| R <sub>EN</sub>                 | Enable pin pullup resistor                                                                |                                                               |                    | 100                |                    | kΩ    |

| V <sub>DIM</sub>                | DIM logic input threshold                                                                 | DIM rising threshold w.r.t. CGND                              |                    |                    | 1.6                |       |

| 2                               | - · ·                                                                                     | DIM falling threshold w.r.t. CGND                             | 0.6                |                    |                    | V     |

| R <sub>DIM</sub>                | DIM pin pulldown resistor                                                                 |                                                               | -                  | 100                |                    | kΩ    |

|                                 | ADJ pin current                                                                           |                                                               | -1.0               |                    | 1.0                | μΑ    |

| I <sub>SS</sub>                 | SS pin source current                                                                     |                                                               |                    | 10                 |                    | μA    |

| R <sub>SS</sub>                 | SS pin pulldown resistance                                                                | EN = CGND                                                     |                    | 1.0                |                    | kΩ    |

(1) All limits specified at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are 100% production tested. All limits at temperature extremes are ensured via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) Typical numbers are at 25°C and represent the most likely norm.

SNVS535B -OCTOBER 2007-REVISED MARCH 2008

www.ti.com

## ELECTRICAL CHARACTERISTICS (continued)

Specifications in standard type face are for  $T_J = 25^{\circ}$ C and those with **boldface type** apply over the full **Operating Temperature Range** ( $T_J = -40^{\circ}$ C to +125°C). Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = +25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{EE} = -12.0$ V and  $V_{IN} = +3.3$ V with respect to CGND.

| Symbol                  | Parameter                          | Conditions                        | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units |

|-------------------------|------------------------------------|-----------------------------------|--------------------|--------------------|--------------------|-------|

| AC SPEC                 | IFICATIONS                         |                                   |                    |                    |                    |       |

| T <sub>DTD</sub>        | LO and HO dead time                | LO falling to HO rising dead time |                    | 26                 |                    | -     |

|                         |                                    | HO falling to LO rising dead time |                    | 28                 |                    | ns    |

| T <sub>PDIM</sub>       | DIM to DIMO propagation delay      | DIM rising to DIMO rising delay   |                    | 68                 | 124                |       |

|                         |                                    | DIM falling to DIMO falling delay |                    | 58                 | 160                | ns    |

| THERMAI                 | SPECIFICATIONS                     |                                   |                    |                    |                    |       |

| T <sub>JLIM</sub>       | Junction temperature thermal limit |                                   |                    | 175                |                    | °C    |

| T <sub>JLIM(hyst)</sub> | Thermal limit hysteresis           |                                   |                    | 20                 |                    | °C    |

| θ <sub>JA</sub>         | WQFN package thermal resistance    | JEDEC 4 layer board               |                    | 39                 |                    | °C/W  |

Figure 5.

TEXAS INSTRUMENTS

www.ti.com

SNVS535B-OCTOBER 2007-REVISED MARCH 2008

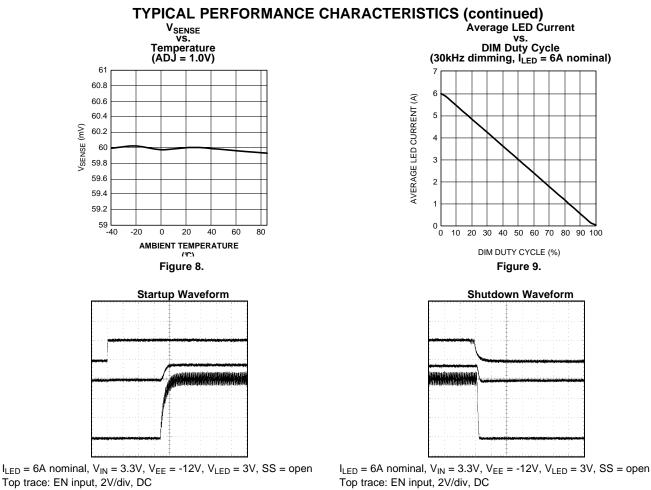

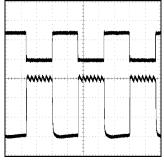

Middle trace:  $V_{EE}$  input current, 2A/div, DC Bottom trace:  $I_{LED}$ , 2A/div, DC T = 100µs/div

Figure 11.

Middle trace: V<sub>EE</sub> input current, 2A/div, DC

Bottom trace: ILED, 2A/div, DC

30kHz PWM Dimming Waveform Showing Inductor Ripple Current

T = 100µs/div

$$\begin{split} I_{LED} &= 6A \text{ nominal, } V_{IN} = 3.3V, V_{EE} = -12V\\ \text{Top trace: DIM input, } 2V/div, DC\\ \text{Bottom trace: } I_{LED}, 2A/div, DC\\ T &= 10 \mu s/div \end{split}$$

Figure 12.

#### Operation

#### **CURRENT REGULATOR OPERATION**

The LM3433 is a controller for a Continuous Conduction Buck Converter. Because of its buck topology and operation in the continuous mode, the output current is very well controlled. It only varies within a switching frequency cycle by the inductor ripple current. This ripple current is normally set at 10% of the DC current. Setting the ripple current lower than 10% is a useful tradeoff of inductor size for less LED light output ripple. Additional circuitry can be added to achieve any LED light ripple desired.

The LED current is set by the voltage across a sense resistor. This sense voltage is nominally 60mV but can be programmed higher or lower by an external control voltage.

The running frequency of the converter is programmed by an external RC network in conjunction with the LED's forward voltage. The frequency is nominally set around 200kHz to 500khz. Fast PWM control is available by shorting the output of the current source by a MOSFET in parallel with the LED. During the LED OFF time the running frequency is determined by the RC network and the parasitic resistance of the output circuit including the DIM FET R<sub>DSON</sub>.

The LM3433 system has been evaluated to be a very accurate, high compliance current source. This is manifest in its high output impedance and accurate current control. The current is measured to vary less than 6mA out of 6A when transitioning from LED OFF (output shorted) to LED ON (output ~6V).

#### PROTECTION

The LM3433 has dedicated protection circuitry running during normal operation. The thermal shutdown circuitry turns off all power devices when the die temperature reaches excessive levels. The V<sub>CC</sub> undervoltage lockout (UVLO) comparator protects the power devices during power supply startup and shutdown to prevent operation at voltages less than the minimum operating input voltage. The V<sub>CC</sub> pin is short circuit protected to V<sub>EE</sub>. The LM3433 also features a shutdown mode which decreases the supply current to approximately 35µA.

The ADJ, EN, and DIM pins are capable of sustaining up to +/-2mA. If the voltages on these pins will exceed either  $V_{IN}$  or CGND by necessity or by a potential fault, an external resistor is recommended for protection. Size this resistor to limit pin current to under 2mA. A 10k resistor should be sufficient. This resistor may be used in any application for added protection without any impact on function or performance.

#### **DESIGN PROCEDURE**

This section presents guidelines for selecting external components.

#### SETTING LED CURRENT CONTROL

LM3433 uses average current mode control to regulate the current delivered to the LED ( $I_{LED}$ ). An external current sense resistor ( $R_{SENSE}$ ) in series with the LED is used to convert  $I_{LED}$  into a voltage that is sensed by the LM3433 at the CSP and CSN pins. CSP and CSN are the inputs to an error amplifier with a programmed input offset voltage ( $V_{SENSE}$ ).  $V_{SENSE}$  is used to regulate  $I_{LED}$  based on the following equation:

$I_{LED} = V_{SENSE}/R_{SENSE}$

#### FIXED LED CURRENT

The ADJ pin sets  $V_{SENSE}$ . Tie ADJ to  $V_{IN}$  to use a fixed 60mV internal reference for  $V_{SENSE}$ . Select  $R_{SENSE}$  to fix the LED current based on the following equation:

$R_{SENSE} = 60 mV/I_{LED}$

#### ADJUSTABLE LED CURRENT

$V_{\text{SENSE}} = (V_{\text{ADJ}} - V_{\text{CGND}})/16.6$

(3)

(1)

(2)

SNVS535B-OCTOBER 2007-REVISED MARCH 2008

#### When the reference on ADJ is adjustable, V<sub>SENSE</sub> and I<sub>LED</sub> can be adjusted within the linear range of the ADJ pin. This range has the following limitations:

$0.3V < V_{\text{ADJ}} <$  (The greater of 1.5V or (V\_{IN} - 1.9V))

When V<sub>ADJ</sub> is less than this linear range the V<sub>SENSE</sub> is guaranteed by design to be less than or equal to 0.3V/16.667. When V<sub>ADJ</sub> is greater than this linear range and less than V<sub>IN</sub> - 1V, V<sub>SENSE</sub> is specified by design to be less than or equal to  $V_{ADJ}/16.667$ . If  $V_{ADJ}$  is greater than  $V_{IN}$  - 1V,  $V_{SENSE}$  switches to 60mV.

## INPUT CAPACITOR SELECTION

A low ESR ceramic capacitor is needed to bypass the MOSFETs. This capacitor is connected between the drain of the synchronous FET (CGND) and the source of the main switch ( $V_{EE}$ ). This capacitor prevents large voltage transients from appearing at the V<sub>FF</sub> pin of the LM3433. Use a 22µF value minimum with X5R or X7R dielectric. In addition to the FET bypass capacitors, additional bypass capacitors should be placed near the V<sub>EE</sub> and V<sub>IN</sub> pins and should be returned to CGND.

The input capacitor must also be sized to handle the dimming frequency input ripple when the DIM function is used. This ripple may be as high as 85% of the nominal DC input current (at 50% duty cycle). When dimming this input capacitor should be selected to handle the input ripple current.

#### RECOMMENDED OPERATING FREQUENCY AND ON TIME "TIME<sub>ON</sub>" CALCULATION

Although the switching frequency can be set over a wide range, the following equation describes the recommended frequency selection given inexpensive magnetic materials available today:

$$f = \frac{A}{\sqrt{I_{LED}}} (MHz)$$

(5)

In the above equation A=1.2 for powdered iron core inductors and A=0.9 or less for ferrite core inductors. This difference takes into account the fact that ferrite cores generally become more lossy at higher frequencies. Given the switching frequency f calculated above, TIME<sub>ON</sub> can be calculated. If V<sub>LED</sub> is the forward voltage drop of the LED that is being driven, TIME<sub>ON</sub> can be calculated with the following equation:

Using the calculated value for TIME<sub>ON</sub>, the timing components

$$R_{ON}$$

and  $C_{ON}$  can be selected.  $C_{ON}$  should be large enough to dominate the parasitic capacitance of the  $T_{ON}$  pin. A good  $C_{ON}$  value for most applications is 1nF. Based on calculated TIME<sub>ON</sub>,  $C_{ON}$ , and the nominal  $V_{EE}$  and  $V_{LED}$  voltages,  $R_{ON}$  can be calculated based on the following equation:

10

V<sub>LED</sub>

$R_{ON} = \frac{TIME_{ON}}{C_{ON}(0.3/(|V_{EE}|-V_{LED}))}$

TIMING COMPONENTS (R<sub>on</sub> and C<sub>on</sub>)

$\mathsf{TIME}_{\mathsf{ON}} = \frac{1}{\mathsf{f}|\mathsf{V}_{\mathsf{EE}}|}$

The most critical inductor parameters are inductance, current rating, and DC resistance. To calculate the inductance, use the desired peak to peak LED ripple current (IRIPPLE), RON, and CON. A reasonable value for I<sub>RIPPLE</sub> is 10% of I<sub>LED</sub>. The inductor value is calculated using the following equation:

$$L = \frac{0.3 \times R_{ON} \times C_{ON}}{I_{RIPPLE}}$$

(8)

#### For all $V_{LED}$ and $V_{EE}$ voltages, $I_{RIPPLE}$ remains constant and is only dependent on the passive external components R<sub>ON</sub>, C<sub>ON</sub>, and L.

The I<sup>2</sup>R loss caused by the DC resistance of the inductor is an important parameter affecting the efficiency. Lower DC resistance inductors are larger. A good tradeoff point between the efficiency and the core size is letting the inductor I<sup>2</sup>R loss equal 1% to 2% of the output power. The inductor should have a current rating greater than the peak current for the application. The peak current is  $I_{LED}$  plus 1/2  $I_{RIPPLE}$ .

(4)

۱

(7)

(6)

#### POWER FET SELECTION

FETs should be chosen so that the  $I^2R_{DSON}$  loss is less than 1% of the total output power. Analysis shows best efficiency with around  $8m\Omega$  of  $R_{DSON}$  and 15nC of gate charge for a 6A application. All of the switching loss is in the main switch FET. An additional important parameter for the synchronous FET is reverse recovery charge ( $Q_{RR}$ ). High  $Q_{RR}$  adversely affects the transient voltages seen by the IC. A low  $Q_{RR}$  FET should be used.

#### DIM FET SELECTION

Choose a DIM FET with the lowest  $R_{DSON}$  for maximum efficieny and low input current draw during the DIM cycle. The output voltage during DIM will determine the switching frequency. A lower output voltage results in a lower switching frequency. If the lower frequency during DIM must be bound, choose a FET with a higher  $R_{DSON}$  to force the switching frequency higher during the DIM cycle.

#### **BOOTSTRAP CAPACITORS**

The LM3433 uses two bootstrap capacitors and a bypass capacitor on V<sub>CC</sub> to generate the voltages needed to drive the external FETs. A 2.2µF ceramic capacitor or larger is recommended between the V<sub>CC</sub> and LS pins. A 0.47µF is recommended between the HS and BST pins. A 0.1µF is recommended between BST2 and CGND.

#### SOFT-START CAPACITOR

The LM3433 integrates circuitry that, when used in conjunction with the SS pin, will slow the current ramp on start-up. The SS pin is used to tailor the soft-start for a specific application. A capacitor value of 0.1µF on the SS pin will yield a 12mS soft start time. For most applications soft start is not needed.

#### ENABLE OPERATION

The EN pin of the LM3433 is designed so that it may be controlled using a 1.6V or higher logic signal. If the enable function is not used, the EN pin may be tied to  $V_{IN}$  or left open. This pin is pulled to  $V_{IN}$  internally through a 100k pull up resistor.

#### PWM DIM OPERATION

The DIM pin of the LM3433 is designed so that it may be controlled using a 1.6V or higher logic signal. The PWM frequency easily accomodates more than 40kHz dimming and can be much faster if needed. If the PWM DIM pin is not used, tie it to CGND or leave it open. The DIM pin is tied to CGND internally through a 100k pull down resistor.

#### LAYOUT CONSIDERATIONS

The LM3433 is a high performance current driver so attention to layout details is critical to obtain maximum performance. The most important PCB board design consideration is minimizing the loop comprised by the main FET, synchronous FET, and their associated decoupling capacitor(s). Place the V<sub>CC</sub> bypass capacitor as near as possible to the LM3433. Place the PWM dimming/shunt FET as close to the LED as possible. A ground plane should be used for power distribution to the power FETs. Use a star ground between the LM3433 circuitry, the synchronous FET, and the decoupling capacitor(s). The EP contact on the underside of the package must be connected to V<sub>EE</sub>. The two lines connecting the sense resistor to CSN and CSP must be routed as a differential pair directly from the resistor. A Kelvin connection is recommended. It is good practice to route the DIMO/DIMR, HS/HO, and LO/LS lines as differential pairs. The most important PCB board design consideration is minimizing the loop comprised by the main FET, synchronous FET, and their associated decoupling capacitor(s). Optimally this loop should be orthogonal to the ground plane.

TEXAS INSTRUMENTS

SNVS535B-OCTOBER 2007-REVISED MARCH 2008

www.ti.com

Figure 13. 2A to 6A Output Application Circuit

Figure 14. 2A to 14A Output Application Circuit

SNVS535B-OCTOBER 2007-REVISED MARCH 2008

| Manufacturer | Inductor                     | Contact Information               |  |  |  |

|--------------|------------------------------|-----------------------------------|--|--|--|

| Coilcraft    | GA3252-AL and SER1360 series | www.coilcraft.com<br>800-322-2645 |  |  |  |

| Coiltronics  | HCLP2 series                 | www.coiltronics.com               |  |  |  |

| Pulse        | PB2020 series                | www.pulseeng.com                  |  |  |  |

## Table 1. Some Recommended Inductors (Others May Be Used)

## Table 2. Some Recommended Input/Bypass Capacitors (Others May Be Used)

| Manufacturer     | Capacitor                                                                     | Contact Information             |

|------------------|-------------------------------------------------------------------------------|---------------------------------|

| Vishay Sprague   | 293D, 592D, and 595D series tantalum                                          | www.vishay.com<br>407-324-4140  |

| Taiyo Yuden      | High capacitance MLCC ceramic                                                 | www.t-yuden.com<br>408-573-4150 |

| Cornell Dubilier | ESRD seriec Polymer Aluminum Electrolytic<br>SPV and AFK series V-chip series | www.cde.com                     |

| MuRata           | High capacitance MLCC ceramic                                                 | www.murata.com                  |

### Table 3. Some Recommended MOSFETs (Others May Be Used)

| Manufacturer     | Inductor                                                    | Contact Information                          |

|------------------|-------------------------------------------------------------|----------------------------------------------|

| Siliconix        | Si7386DP (Main FET, DIM FET)<br>Si7668ADP (Synchronous FET) | www.vishay.com/company/brands/sili<br>conix/ |

| ON Semiconductor | NTMFS4841NHT1G (Main FET, Synchronous FET, DIM FET)         | www.onsemi.com                               |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated