April 2000

LM9832 42-Bit Color 1200dpi USB Image

Scanner

National Semiconductor

### LM9832 42-Bit Color, 1200dpi USB Image Scanner **General Description Features**

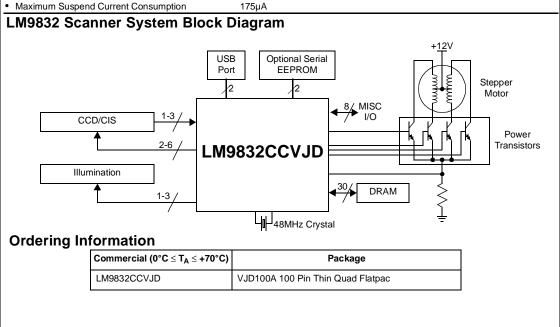

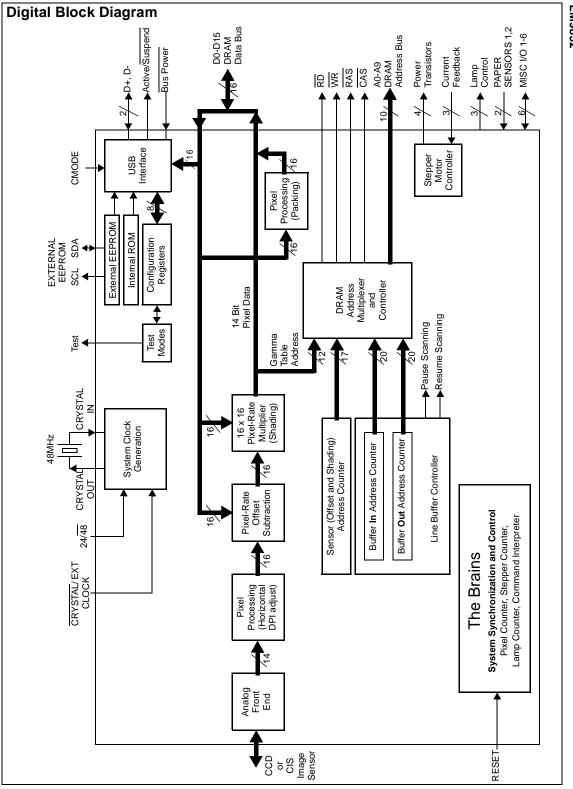

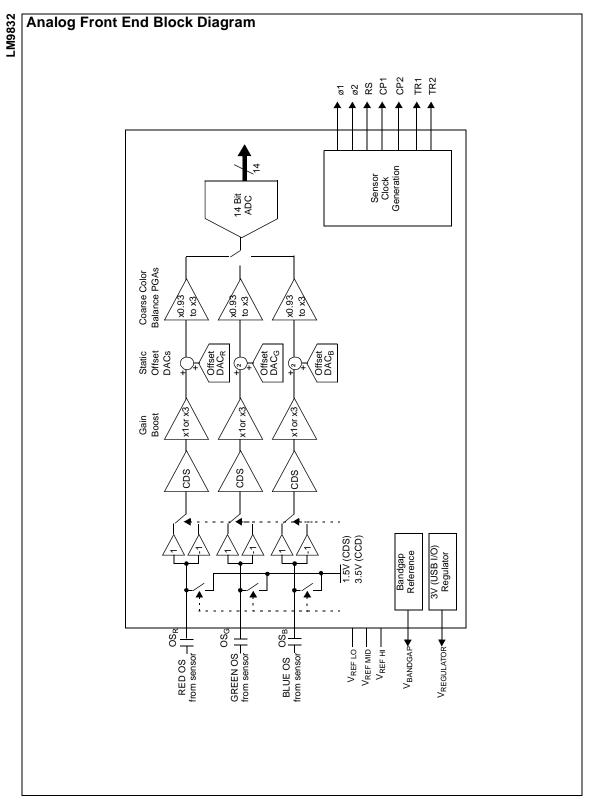

The LM9832 is a complete USB image scanner system on a single IC. The LM9832 provides all the functions (image sensor control, illumination control, analog front end, pixel processing function image data buffer/DRAM controller, microstepping motor controller, and USB interface) necessary to create a high performance color scanner. The LM9832 scans images in 42 bit color/14 bit gray, and has output data formats for 42 and 24 bit color/14 and 8 bit gray. The LM9832 supports sensors with pixel counts of up to 16384 pixels x 3 colors (1200 dpi x 13.6 inches).

The LM9832's low operating and suspend mode supply currents allow design of USB bus-powered scanners. The only additional active components required are an external 4Mbit or 16Mbit DRAM for data buffering and power transistors for the stepper motor.

### Applications

- Color Flatbed Document Scanners

- Color Sheetfed Document Scanners

## **Key Specifications**

- Analog to Digital Converter Resolution 14 Bits • Maximum Pixel Conversion Rate 6MHz A4 Color 150dpi scan time <10 seconds · A4 Color 300dpi scan time <40 seconds A4 Color 600dpi scan time <160 seconds Supply Voltage - LM9832 +4.75V to +5.25V - LM9832 DRAM I/O +2.85 to +5.25V Maximum Operating Current Consumption 136mA

- Maximum Suspend Current Consumption

- 14 bit ADC digitizes at up to 6Mpixels/s (2M RGB pixels/sec).

- Digital Pixel Processing provides 1200, 800, 600, 400, 300, 200, 150, and 100dpi horizontal resolution from a 1200dpi sensor and 600, 400, 300, 200, 150, 100, 75, and 50dpi horizontal resolution from a 600dpi sensor.

- Provides 50-2400dpi vertical resolution in 1 dpi increments.

- Pixel rate error correction for gain (shading) and offset errors.

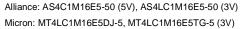

- Supports 4 or 16Mbit external DRAMs.

- Multiple CCD clocking rates allows matching of CCD clock to scan resolution and pixel depth for maximum scan speed.

- Stepper motor control tightly coupled with image data buffer management to maximize data transfer efficiency.

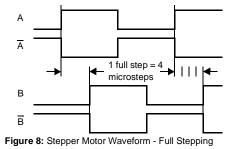

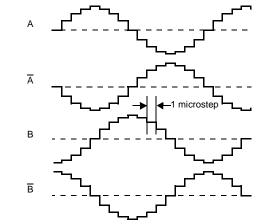

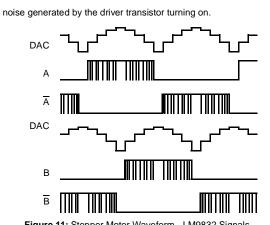

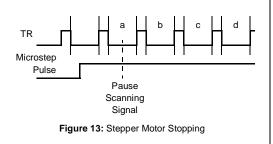

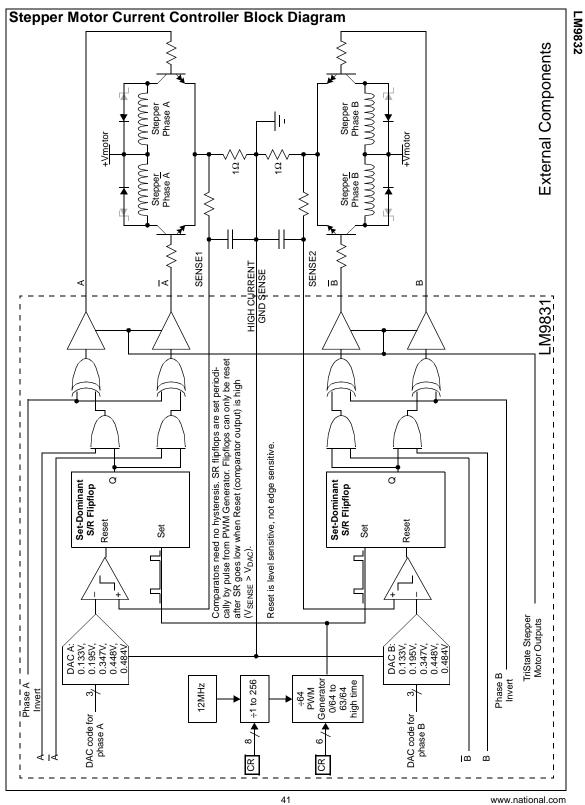

- PWM stepper motor current control allows microstepping for the price of fullstepping.

- USB interface for Plug and Play operation on USB-equipped computers.

- Serial EEPROM option for custom Vendor and Product IDs.

- Support for USB bus-powered operation.

- Pixel depths of 1, 2, or 4 bits are packed into bytes for faster scans of line art and low pixel depth images.

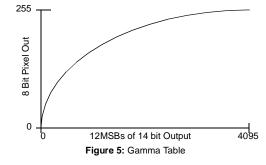

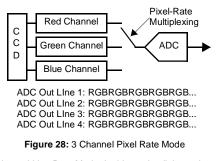

- Supports 3 channel CCDs and 1 channel CIS sensors. 3 (R, G, and B) 12-bit, user-programmable gamma correction tables

- Compatible with a wide range of color linear CCDs and Contact Image Sensors (CIS).

- Operates with 48MHz external crystal.

- Internal bandgap voltage reference.

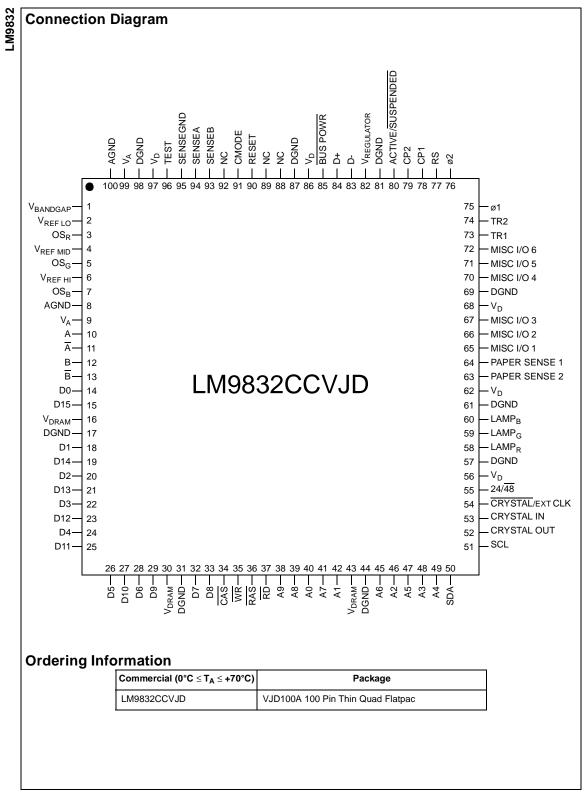

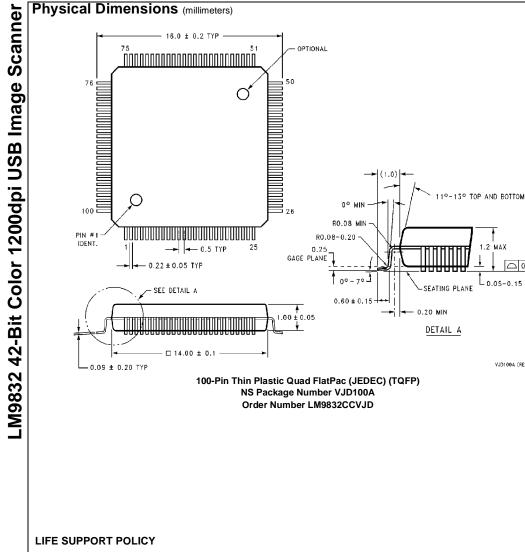

- 100 pin TQFP package

©2000 National Semiconductor Corporation

www.national.com

| Pin Descriptions                                          |                                                                                                                                                                                                            |  |  |  |  |  |  |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                           | USB Interface                                                                                                                                                                                              |  |  |  |  |  |  |

| D+, D-                                                    | Digital I/O. USB Interface signals                                                                                                                                                                         |  |  |  |  |  |  |

| BUS POWER                                                 | Digital Input. Tie low for bus powered sys-<br>tems, tie high for external power.                                                                                                                          |  |  |  |  |  |  |

| ACTIVE/<br>SUSPENDED                                      | Digital Output. Low in Suspend mode. High in operational mode. Used to control external regulators, other components.                                                                                      |  |  |  |  |  |  |

| SDA                                                       | Digital I/O. Serial Data to/from external EEPROM.                                                                                                                                                          |  |  |  |  |  |  |

| SCL                                                       | Digital Output. Serial Clock Output to external EEPROM.                                                                                                                                                    |  |  |  |  |  |  |

|                                                           | Analog                                                                                                                                                                                                     |  |  |  |  |  |  |

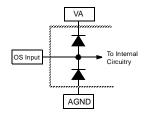

| OS <sub>R</sub> ,<br>OS <sub>G</sub> ,<br>OS <sub>B</sub> | Analog Inputs. These inputs (for Red, Green,<br>and Blue) should be tied to the sensor's out-<br>put signal through DC blocking capacitors. If<br>unused, tie to ground through DC blocking<br>capacitors. |  |  |  |  |  |  |

| V <sub>REF LO</sub>                                       | Analog Output/Input. Bypass to AGND with a 0.047µF monolithic capacitor. Do not put a DC load on this pin.                                                                                                 |  |  |  |  |  |  |

| V <sub>REF MID</sub>                                      | Analog Output/Input. Bypass to AGND with a 0.047µF monolithic capacitor. Do not put a DC load on this pin.                                                                                                 |  |  |  |  |  |  |

| V <sub>REF HI</sub>                                       | Analog Output/Input. Bypass to AGND with a $0.047\mu F$ monolithic capacitor. Do not put a DC load on this pin.                                                                                            |  |  |  |  |  |  |

| V <sub>BANDGAP</sub>                                      | Analog Output. Bypass to AGND with a 0.047μF monolithic capacitor. Do not put a DC load on this pin.                                                                                                       |  |  |  |  |  |  |

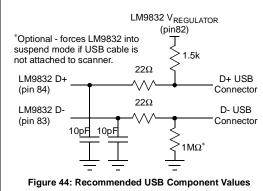

| V <sub>REGULATOR</sub>                                    | Analog Output. Bypass to AGND with a 0.047µF monolithic capacitor. Used as termi-<br>nal voltage for 1.5k D+ pullup resistor.                                                                              |  |  |  |  |  |  |

|                                                           | DRAM                                                                                                                                                                                                       |  |  |  |  |  |  |

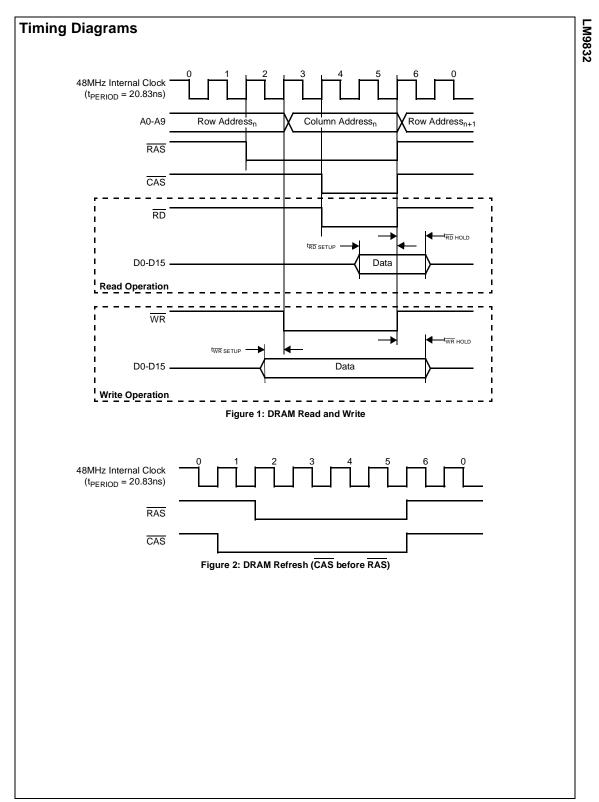

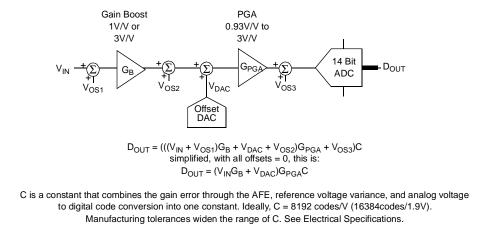

| D0 (LSB) -D15<br>(MSB)                                    | Digital Inputs/Outputs. This is the 16 bit data path between the external DRAM and the LM9832.                                                                                                             |  |  |  |  |  |  |

| RD                                                        | Digital Output. Read signal to external DRAM.                                                                                                                                                              |  |  |  |  |  |  |

| WR                                                        | Digital Output. Write signal to external DRAM.                                                                                                                                                             |  |  |  |  |  |  |

| A0-A9                                                     | Digital Outputs. Address pins for up to 1M x 16 external DRAM.                                                                                                                                             |  |  |  |  |  |  |

| RAS                                                       | Digital Output. Row Address Strobe signal.                                                                                                                                                                 |  |  |  |  |  |  |

| CAS                                                       | Digital Output. Column Address Strobe sig-<br>nal.                                                                                                                                                         |  |  |  |  |  |  |

|                                                                 | Scanner Support I/O                                                                                                                                                                                                                       |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

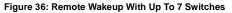

| PAPER<br>SENSE 1-2                                              | Digital Inputs. Programmable, used for sens<br>ing home position, paper, front pane<br>switches, etc.                                                                                                                                     |

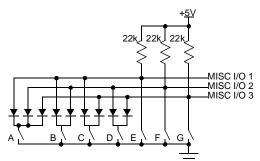

| MISC I/O 1-6                                                    | Digital Inputs/Outputs. Programmable, used<br>for front panel switches, status LEDs, etc. A<br>power-on and in Suspend Mode, MISC I/Os<br>1-3 are inputs and MISC I/Os 4-6 are outputs                                                    |

|                                                                 | Stepper Motor                                                                                                                                                                                                                             |

| A, B, <del>Ā</del> , <del>B</del>                               | Digital Outputs. Pulses to stepper motor drive<br>circuitry.                                                                                                                                                                              |

| SENSE <sub>A</sub> ,<br>SENSE <sub>B</sub>                      | Analog Inputs. Current sensing for steppe motor's PWM current control.                                                                                                                                                                    |

| SENSE <sub>GND</sub>                                            | Analog Input. Ground sense input for steppe motor's PWM current control.                                                                                                                                                                  |

|                                                                 | Sensor Control                                                                                                                                                                                                                            |

| ø1                                                              | Digital Output. CCD/CIS clock signal phase 1                                                                                                                                                                                              |

| ø2                                                              | Digital Output. CCD/CIS clock signal phase 2                                                                                                                                                                                              |

| RS                                                              | Digital Output. Reset pulse for the CCD/CIS.                                                                                                                                                                                              |

| CP1                                                             | Digital Output. Clamp pulse for the CCD/CIS.                                                                                                                                                                                              |

| CP2                                                             | Digital Output. Clamp pulse for the CCD/CIS.                                                                                                                                                                                              |

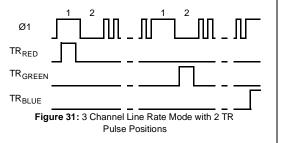

| TR1, TR2                                                        | Digital Outputs. Transfer pulses for the CCD/CIS.                                                                                                                                                                                         |

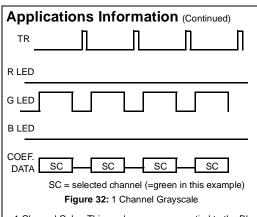

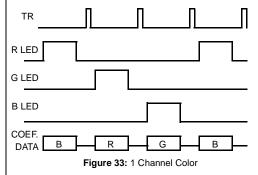

| LAMP <sub>R</sub> ,<br>LAMP <sub>G</sub> ,<br>LAMP <sub>B</sub> | Digital Outputs. Used to control R, G, and E<br>LEDs of single output CIS, as well as bright<br>ness of CCFL. The CDS signal can be seer<br>on LAMP <sub>B</sub> in a test mode (see register 5E, bi<br>7).                               |

| Ma                                                              | ster Clock Generation                                                                                                                                                                                                                     |

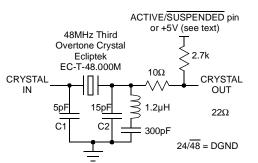

| CRYSTAL IN                                                      | Digital Input. Used with CRYSTAL OUT and<br>an external 48MHz crystal to form a crystal<br>oscillator.                                                                                                                                    |

| CRYSTAL<br>OUT                                                  | Digital Output. Used with CRYSTAL IN and ar<br>external 48MHz crystal to form a crystal oscil<br>lator.                                                                                                                                   |

| CRYSTAL/<br>EXT CLOCK                                           | Digital Input. Tie to DGND for operation with an external crystal. Pull up to $V_D$ to drive CRYSTAL OUT with an external TTL o CMOS clock source.                                                                                        |

| 24/48                                                           | Digital Input. Tie to DGND for operation with a 48MHz crystal or external clock. Pull up to V <sub>r</sub> for operation with a 24MHz crystal or externa clock. NOTE: Operation at 24MHz is not guar anteed - always use a 48MHz crystal. |

| Miscellaneous           RESET         Digital input. Take high to force device into<br>Power On Reset state, low to exit reset state.           TEST         Analog Output.           CMODE         Digital Input. Test mode, always tie high.           Analog Power Supplies (4 pins)           V <sub>A</sub> (2)         This is the positive supply pin for the analog<br>supply. It should be connected to a voltage<br>source of +5V and bypassed to AGND with a<br>0.1µF monolithic capacitor in parallel with a<br>10µF tantalum capacitor.           AGND (2)         This is the ground return for the analog sup-<br>ply.           Digital Power Supplies (17 pins)           V <sub>D</sub> (5)         This is the positive supply pin for the digital<br>supply. It should be connected to a voltage<br>source of +5V and bypassed to DGND with a<br>0.1µF monolithic capacitor.           V <sub>D</sub> (5)         This is the positive supply pin for the digital<br>supply of the LM9832's external DRAM I/O. It<br>also powers the A, B, A, and B stepper motor<br>outputs. It should be connected to a 3 or 5V<br>supply and bypassed to the closest DGND pin<br>with a 0.1µF monolithic capacitor.           DGND (9)         This is the ground return for V <sub>D</sub> and V <sub>DRAM</sub> .                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power On Reset state, low to exit reset state.           TEST         Analog Output.           CMODE         Digital Input. Test mode, always tie high.           Analog Power Supplies (4 pins)           V <sub>A</sub> (2)         This is the positive supply pin for the analog supply. It should be connected to a voltage source of +5V and bypassed to AGND with a 0.1µF monolithic capacitor in parallel with a 10µF tantalum capacitor.           AGND (2)         This is the positive supply pin for the analog supply. It should be connected to a voltage source of +5V and bypassed to AGND with a 0.1µF monolithic capacitor.           V <sub>D</sub> (5)         This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.           V <sub>D</sub> (5)         This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.           V <sub>DRAM</sub> (3)         This is the positive supply pin for the digital supply for the LM9832's external DRAM I/O. It also powers the A, B, Ā, and B stepper motor outputs. It should be connected to a 3 or 5V supply and bypassed to the closest DGND pin with a 0.1µF monolithic capacitor. |

| CMODE         Digital Input. Test mode, always tie high.           Analog         Power Supplies (4 pins)           V <sub>A</sub> (2)         This is the positive supply pin for the analog supply. It should be connected to a voltage source of +5V and bypassed to AGND with a 0.1µF monolithic capacitor in parallel with a 10µF tantalum capacitor.           AGND (2)         This is the ground return for the analog supply.           Digital Power Supplies (17 pins)           V <sub>D</sub> (5)         This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.           V <sub>DRAM</sub> (3)         This is the positive supply pin for the digital supply for the LM9832's external DRAM I/O. It also powers the A, B, Ā, and B stepper motor outputs. It should be connected to a 3 or 5V supply and bypassed to the closest DGND pin with a 0.1µF monolithic capacitor.                                                                                                                                                                                                                                                                                                                                                                    |

| Analog Power Supplies (4 pins)           V <sub>A</sub> (2)         This is the positive supply pin for the analog supply. It should be connected to a voltage source of +5V and bypassed to AGND with a 0.1µF monolithic capacitor in parallel with a 10µF tantalum capacitor.           AGND (2)         This is the ground return for the analog supply.           Digital Power Supplies (17 pins)           V <sub>D</sub> (5)         This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.           V <sub>DRAM</sub> (3)         This is the positive supply pin for the digital supply for the LM9832's external DRAM I/O. It also powers the A, B, Ā, and B stepper motor outputs. It should be connected to a 3 or 5V supply and bypassed to the closest DGND pin with a 0.1µF monolithic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>A</sub> (2)       This is the positive supply pin for the analog supply. It should be connected to a voltage source of +5V and bypassed to AGND with a 0.1µF monolithic capacitor in parallel with a 10µF tantalum capacitor.         AGND (2)       This is the ground return for the analog supply.         Digital Power Supplies (17 pins)         V <sub>D</sub> (5)       This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.         V <sub>DRAM</sub> (3)       This is the positive supply pin for the digital supply for the LM9832's external DRAM I/O. It also powers the A, B, Ā, and B stepper motor outputs. It should be connected to a 3 or 5V supply and bypassed to the closest DGND pin with a 0.1µF monolithic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| supply. It should be connected to a voltage source of +5V and bypassed to AGND with a 0.1µF monolithic capacitor in parallel with a 10µF tantalum capacitor.         AGND (2)       This is the ground return for the analog supply.         Digital Power Supplies (17 pins)         V <sub>D</sub> (5)       This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.         V <sub>DRAM</sub> (3)       This is the positive supply pin for the digital supply for the LM9832's external DRAM I/O. It also powers the A, B, Ā, and B stepper motor outputs. It should be connected to a 3 or 5V supply and bypassed to the closest DGND pin with a 0.1µF monolithic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Digital Power Supplies (17 pins)           V <sub>D</sub> (5)         This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.           V <sub>DRAM</sub> (3)         This is the positive supply pin for the digital supply for the LM9832's external DRAM I/O. It also powers the A, B, Ā, and B stepper motor outputs. It should be connected to a 3 or 5V supply and bypassed to the closest DGND pin with a 0.1µF monolithic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>D</sub> (5)         This is the positive supply pin for the digital supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.           V <sub>DRAM</sub> (3)         This is the positive supply pin for the digital supply for the LM9832's external DRAM I/O. It also powers the A, B, Ā, and B stepper motor outputs. It should be connected to a 3 or 5V supply and bypassed to the closest DGND pin with a 0.1µF monolithic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| supply. It should be connected to a voltage source of +5V and bypassed to DGND with a 0.1µF monolithic capacitor.         V <sub>DRAM</sub> (3)       This is the positive supply pin for the digital supply for the LM9832's external DRAM I/O. It also powers the A, B, Ā, and B stepper motor outputs. It should be connected to a 3 or 5V supply and bypassed to the closest DGND pin with a 0.1µF monolithic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| supply for the LM9832's external DRAM I/O. It<br>also powers the A, B, $\overline{A}$ , and $\overline{B}$ stepper motor<br>outputs. It should be connected to a 3 or 5V<br>supply and bypassed to the closest DGND pin<br>with a 0.1 $\mu$ F monolithic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DGND (9) This is the ground return for $V_D$ and $V_{DRAM}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Absolute Maximum Ratings (Notes 1 & 2)

| Positive Supply Voltage (V <sup>+</sup> =V <sub>A</sub> =V <sub>D</sub> =V <sub>DRA</sub> | AM)              |

|-------------------------------------------------------------------------------------------|------------------|

| With Respect to GND=AGND=DGND                                                             | 6.5V             |

| Voltage On Any Input or Output Pin                                                        | -0.3V to V++0.3V |

| Input Current at any pin (Note 3)                                                         | ±25mA            |

| Package Input Current (Note 3)                                                            | ±50mA            |

| Package Dissipation at $T_A = 25^{\circ}C$                                                | (Note 4)         |

| ESD Susceptibility (Note 5)                                                               |                  |

| Human Body Model                                                                          | 2000 V           |

| Machine Model                                                                             | 250 V            |

| Soldering Information                                                                     |                  |

| Infrared, 10 seconds (Note 6)                                                             | 235°C            |

| Storage Temperature                                                                       | -65°C to +150°   |

## Operating Ratings (Notes 1 & 2)

Operating Temperature Range LM9832VJD V<sub>A</sub> Supply Voltage V<sub>D</sub> Supply Voltage V<sub>DRAM</sub> Supply Voltage |V<sub>A</sub>-V<sub>D</sub>| Input Voltage Range

$\begin{array}{c} (\text{NOES 1 CL2}) \\ \Rightarrow & T_{\text{MIN}} \leq T_{\text{A}} \leq T_{\text{MAX}} \\ 0^{\circ}\text{C} \leq T_{\text{A}} \leq +70^{\circ}\text{C} \\ +4.75 \text{V to } +5.25 \text{V} \\ +4.75 \text{V to } +5.25 \text{V} \\ +2.85 \text{V} \leq \text{V}_{\text{DRAM}} \leq \text{V}_{\text{D}} +100 \text{mV} \\ \leq 100 \text{mV} \\ -0.05 \text{V to } \text{V}^{+} + 0.05 \text{V} \end{array}$

## **Electrical Characteristics**

The following specifications apply for AGND=DGND=0V,  $V_A=V_D=V_{DRAM}=+5.0V_{DC}$ ,  $f_{CRYSTAL IN}=48MHz$ , Analog Bias Current = 100%, unless otherwise noted. **Boldface limits apply for T\_A=T\_J=T\_MIN to T\_MAX**; all other limits  $T_A=T_J=25^{\circ}C$ . (Notes 8, 9, & 10)

| Symbol           | Parameter                                                           | Conditions                                                | Typical<br>(Note 9) | Limits<br>(Note 10) | Units<br>(Limits)      |

|------------------|---------------------------------------------------------------------|-----------------------------------------------------------|---------------------|---------------------|------------------------|

| Full Chann       | nel Characteristics (in units of 12 bit LSB                         | s unless otherwise noted)                                 | •                   |                     |                        |

|                  | Resolution with No Missing Codes                                    |                                                           | 14                  | 12                  | bits (min)             |

| DNL              | Differential Non-Linearity<br>(Note 14)                             | Bias Current = 80%,<br>V <sub>DRAM</sub> =3.3V            | -0.45<br>+0.75      | -0.9<br>+2.4        | LSB (min)<br>LSB (max) |

| INL              | Integral Non-Linearity Error<br>(Notes 11 & 14)                     | Bias Current = 80%,<br>V <sub>DRAM</sub> =3.3V            | -2.3<br>+1.7        | -8.5<br>+7.5        | LSB (min)<br>LSB (max) |

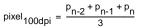

| С                | Analog Channel Gain Constant<br>(ADC Codes/V), referred to 14 bits. | Includes voltage reference<br>variation, gain setting = 1 | 8192                | 7412<br>9300        | LSB (min)<br>LSB (max) |

| V <sub>OS1</sub> | Pre-Boost Analog Channel Offset Error                               |                                                           | 26                  | -34<br>+76          | mV (min)<br>mV (max)   |

| V <sub>OS2</sub> | Pre-PGA Analog Channel Offset Error                                 |                                                           | -30                 | -80<br>+31          | mV (min)<br>mV (max)   |

| V <sub>OS3</sub> | Post-PGA Analog Channel Offset Error                                |                                                           | -26                 | -75<br>+26          | mV (min)<br>mV (max)   |

| Coarse Co        | lor Balance PGA Characteristics (Config                             | uration Registers 3B, 3C, and 3D)                         | 1                   |                     |                        |

|                  | Monotonicity                                                        |                                                           |                     | 5                   | bits (min)             |

|                  | G <sub>0</sub> (Minimum PGA Gain)                                   | PGA Setting = 0                                           | 0.93                | 0.90<br>0.96        | V/V (min)<br>V/V (max) |

|                  | G <sub>31</sub> (Maximum PGA Gain)                                  | PGA Setting = 31                                          | 3.00                | 2.95<br>3.05        | V/V (min)<br>V/V (max) |

|                  | x3 Boost Gain                                                       | x3 Boost Setting On<br>(bit B5 of Gain Register is set)   | 2.94                | 2.85<br>3.04        | V/V (min)<br>V/V (max) |

|                  | Gain Error at any gain (Note 13)                                    |                                                           | 0.3                 | -0.6<br>+0.9        | % (min)<br>% (max)     |

| Static Offs      | et DAC Characteristics (Configuration R                             | egisters 38, 39, and 3A)                                  |                     |                     |                        |

|                  | Monotonicity                                                        |                                                           |                     | 6                   | bits (min)             |

|                  | Offset DAC LSB size                                                 | PGA gain = 1                                              | 9                   | 6<br>12             | mV (min)<br>mV (max)   |

|                  | Offset DAC Adjustment Range                                         | PGA gain = 1                                              | ±278                | ±256                | mV (min)               |

www.national.com

LM9832

## Electrical Characteristics (Continued)

The following specifications apply for AGND=DGND=0V,  $V_A=V_D=V_{DRAM}=+5.0V_{DC}$ ,  $f_{CRYSTAL IN}=48MHz$ , Analog Bias Current = 100%, unless otherwise noted. **Boldface limits apply for**  $T_A=T_J=T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A=T_J=25^{\circ}C$ . (Notes 8, 9, & 10)

| Symbol                                                                                                                                                                                                                                                                                                                                                  | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Conditions                                                                                                                                                                                                                                                                          | Typical<br>(Note 9)                                                         | Limits<br>(Note 10)                                                                | Units<br>(Limits)                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| CCD/CIS S                                                                                                                                                                                                                                                                                                                                               | ource Requirements for Full Specified A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ccuracy and Dynamic Range (No                                                                                                                                                                                                                                                       | ote 12)                                                                     |                                                                                    |                                                                                                                      |

| V <sub>CCDPEAK</sub>                                                                                                                                                                                                                                                                                                                                    | Sensor's Maximum Output Signal<br>Amplitude before LM9832 Analog Front<br>End Saturation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Gain = 0.933<br>Gain = 3.0<br>Gain = 9.0                                                                                                                                                                                                                                            | 1.9<br>0.6<br>0.19                                                          |                                                                                    | V<br>V<br>V                                                                                                          |

| Analog Inp                                                                                                                                                                                                                                                                                                                                              | ut Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                     |                                                                             | <u> </u>                                                                           |                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                         | Average OS <sub>R</sub> , OS <sub>G</sub> , OS <sub>B</sub> Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CDS Enabled, OS = 3.5V <sub>DC</sub>                                                                                                                                                                                                                                                | ±3                                                                          |                                                                                    | nA                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                         | OS <sub>R</sub> , OS <sub>G</sub> , OS <sub>B</sub> Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CDS Disabled, OS = 3.5V <sub>DC</sub>                                                                                                                                                                                                                                               | ±26                                                                         | ±30                                                                                | µA (max                                                                                                              |

| nternal Vo                                                                                                                                                                                                                                                                                                                                              | tage Reference Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                     |                                                                             | L1                                                                                 |                                                                                                                      |

| VBANDGAP                                                                                                                                                                                                                                                                                                                                                | Voltage Reference Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                     | 1.23                                                                        |                                                                                    | V                                                                                                                    |

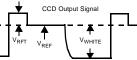

| V <sub>REF LO</sub>                                                                                                                                                                                                                                                                                                                                     | Negative Reference Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                     | V <sub>REF MID</sub> -1.0                                                   |                                                                                    | V                                                                                                                    |

| V <sub>REF MID</sub>                                                                                                                                                                                                                                                                                                                                    | Midpoint Reference Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                     | V <sub>A</sub> /2.0                                                         |                                                                                    | V                                                                                                                    |

| V <sub>REF HI</sub>                                                                                                                                                                                                                                                                                                                                     | Positive Reference Output Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                     | V <sub>REF MID</sub> +1.0                                                   |                                                                                    | V                                                                                                                    |

| V <sub>REGULA</sub> -<br>TOR                                                                                                                                                                                                                                                                                                                            | USB I/O Voltage Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                     | 3.3                                                                         |                                                                                    | V                                                                                                                    |

| CRYSTAL IN                                                                                                                                                                                                                                                                                                                                              | g specifications apply for AGND=DGND=0<br>$48MHz$ . Boldface limits apply for $T_A=T_J=1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathbf{T}_{MIN}$ to $\mathbf{T}_{MAX}$ ; all other limits $T_A=T_J$                                                                                                                                                                                                               | =25°C. (Notes 8,                                                            |                                                                                    | 11.14                                                                                                                |

| CRYSTAL IN=                                                                                                                                                                                                                                                                                                                                             | - 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =<br>Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T <sub>MIN</sub> to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub>                                                                                                                                                                                              | =25°C. (Notes 8,<br>Typical<br>(Note 9)                                     | 9, & 10)<br>Limits<br>(Note 10)                                                    | Units<br>(Limits                                                                                                     |

| CRYSTAL IN=                                                                                                                                                                                                                                                                                                                                             | 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | T <sub>MIN</sub> to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub>                                                                                                                                                                                              | =25°C. (Notes 8,<br>Typical                                                 | Limits                                                                             |                                                                                                                      |

| CRYSTAL IN=                                                                                                                                                                                                                                                                                                                                             | - 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =<br>Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T <sub>MIN</sub> to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub>                                                                                                                                                                                              | =25°C. (Notes 8,<br>Typical                                                 | Limits                                                                             | Units<br>(Limits)<br>V (min)<br>V (min)                                                                              |

| CRYSTAL IN <sup>=</sup><br>Symbol<br>Digital Inpu                                                                                                                                                                                                                                                                                                       | ■ 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =<br>Parameter<br>It Characteristics for D0-D15 (DRAM Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | T <sub>MIN</sub> to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub><br>Conditions<br>erface)                                                                                                                                                                     | =25°C. (Notes 8,<br>Typical                                                 | Limits<br>(Note 10)<br>2.0                                                         | V (min)<br>V (min)<br>V (max                                                                                         |

| Symbol<br>Digital Inpu<br>V <sub>IN(1)</sub>                                                                                                                                                                                                                                                                                                            | 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =     Parameter     It Characteristics for D0-D15 (DRAM Inter     Logical "1" Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VDRAM=3.6V         VDRAM=4.75V                                                                                                                                                                                                                                                      | =25°C. (Notes 8,<br>Typical                                                 | Limits<br>(Note 10)<br>2.0<br>2.0<br>0.8                                           | V (min)<br>V (min)<br>V (max                                                                                         |

| CRYSTAL IN= Symbol Digital Inpu VIN(1) VIN(0)                                                                                                                                                                                                                                                                                                           | 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =     Parameter     It Characteristics for D0-D15 (DRAM Inte     Logical "1" Input Voltage     Logical "0" Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VDRAM=3.6V         VDRAM=4.75V                                                                                                                                                                                                                                                      | =25°C. (Notes 8,<br>Typical<br>(Note 9)                                     | Limits<br>(Note 10)<br>2.0<br>2.0<br>0.8                                           | (Limits)<br>V (min)<br>V (min)<br>V (max)<br>V (max)                                                                 |

| CRYSTAL IN=  Symbol  Digital Inpu VIN(1)  VIN(0)  IIN CIN  Digital Inpu                                                                                                                                                                                                                                                                                 | 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =     Parameter     It Characteristics for D0-D15 (DRAM Inter     Logical "1" Input Voltage     Logical "0" Input Voltage     Input Leakage Current                                                                                                                                                                                                                                                                                                                                                                                                                             | VDRAM=3.6V         VDRAM=3.6V           VDRAM=4.75V         VDRAM=2.85V                                                                                                                                                                                                             | =25°C. (Notes 8,<br>Typical<br>(Note 9)<br>±0.1<br>5                        | Limits<br>(Note 10)<br>2.0<br>2.0<br>0.8<br>0.8                                    | (Limits)<br>V (min)<br>V (min)<br>V (max<br>V (max)<br>μA<br>pF                                                      |

| CRYSTAL IN=  Symbol  Digital Inpu VIN(1)  VIN(0)  IIN CIN  Digital Inpu                                                                                                                                                                                                                                                                                 | 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =     Parameter     tt Characteristics for D0-D15 (DRAM Inter     Logical "1" Input Voltage     Logical "0" Input Voltage     Input Leakage Current     Input Capacitance                                                                                                                                                                                                                                                                                                                                                                                                       | VDRAM=3.6V         VDRAM=3.6V           VDRAM=4.75V         VDRAM=2.85V                                                                                                                                                                                                             | =25°C. (Notes 8,<br>Typical<br>(Note 9)<br>±0.1<br>5                        | Limits<br>(Note 10)<br>2.0<br>2.0<br>0.8<br>0.8                                    | (Limits<br>V (min)<br>V (min)<br>V (max<br>V (max<br>μA<br>pF<br>48, RESE                                            |

| $\frac{\text{CRYSTAL IN}^{2}}{\text{Symbol}}$ $\frac{\text{Digital Input}}{\text{V}_{IN(1)}}$ $\frac{\text{V}_{IN(0)}}{\text{I}_{IN}}$ $\frac{\text{Digital Input}}{\text{CMODE}}$                                                                                                                                                                      | 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =     Parameter     It Characteristics for D0-D15 (DRAM Inter     Logical "1" Input Voltage     Logical "0" Input Voltage     Input Leakage Current     Input Capacitance     It Characteristics for PAPER SENSE 1-2,                                                                                                                                                                                                                                                                                                                                                           | T <sub>MIN</sub> to T <sub>MAX</sub> ; all other limits T <sub>A</sub> =T <sub>J</sub><br>Conditions<br>(V <sub>DRAM</sub> =5.25V<br>V <sub>DRAM</sub> =3.6V<br>(V <sub>DRAM</sub> =4.75V<br>V <sub>DRAM</sub> =2.85V<br>(V <sub>DRAM</sub> =2.85V)<br>MISC I/O 1-6, SDA, BUS POWER | =25°C. (Notes 8,<br>Typical<br>(Note 9)<br>±0.1<br>5                        | Limits<br>(Note 10)<br>2.0<br>2.0<br>0.8<br>0.8<br>0.8<br>CLOCK, 24/               | (Limits<br>V (min)<br>V (max<br>V (max<br>V (max<br>μA<br>pF<br>48, RESE<br>V (min)                                  |

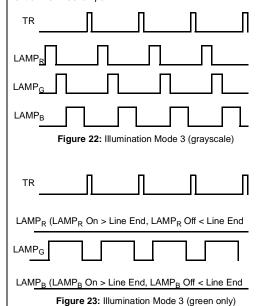

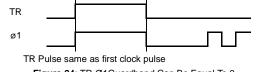

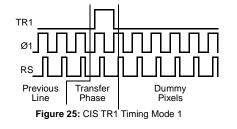

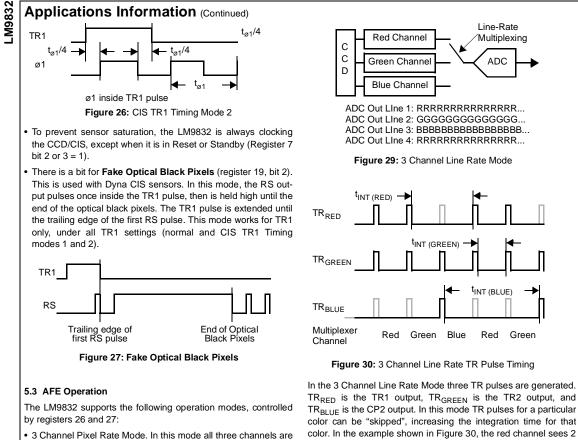

| CRYSTAL IN= Symbol Digital Inpu VIN(1) VIN(0) IIN CIN Digital Inpu CMODE VIN(1)                                                                                                                                                                                                                                                                         | 48MHz. Boldface limits apply for T <sub>A</sub> =T <sub>J</sub> =     Parameter     tt Characteristics for D0-D15 (DRAM Inter     Logical "1" Input Voltage     Logical "0" Input Voltage     Input Leakage Current     Input Capacitance     tt Characteristics for PAPER SENSE 1-2,     Logical "1" Input Voltage                                                                                                                                                                                                                                                                                                                             | VDRAM         Subscription           VDRAM         5.25V           VDRAM         3.6V           VDRAM         4.75V           VDRAM         2.85V           MISC I/O 1-6, SDA, BUS POWER           VD=5.25V                                                                         | =25°C. (Notes 8,<br>Typical<br>(Note 9)<br>±0.1<br>5                        | Limits<br>(Note 10)<br>2.0<br>2.0<br>0.8<br>0.8<br>0.8<br>0.8<br>CLOCK, 24/<br>2.0 | (Limits)<br>V (min)<br>V (max,<br>V (max,<br>V (max,<br>μA<br>pF<br>48, RESE<br>V (min)                              |