# LMK01801 Dual Clock Divider Buffer

Check for Samples: LMK01801

# **FEATURES**

- Pin Control Mode or MICROWIRE (SPI)

- Input and Output Frequency Range 1 kHz to

- Separate Input for Clock Output Banks A & B.

- 14 Differential Clock Outputs in Two Banks (A & B)

- Output Bank A

- 8 Differential, Programmable Outputs (Up to 8 as LVCMOS)

- Divider Values of 1 to 8, Even and Odd.

- Output Bank B

- 6 Differential Outputs (or up to 12 as LVCMOS)

- Divides Values of 1 to 1045 or 1 to 8, **Even and Odd**

- Analog and Digital Delays

- 50% Duty Cycle on All Outputs for All Divides

- Separate Synchronization of Bank A and B.

- RMS Additive Jitter 50 fs at 800 MHz

- 50 fs RMS Additive Jitter (12 kHz to 20 MHz)

- Industrial Temperature Range: -40 to 85 °C

- 3.15 V to 3.45 V Operation

### TARGET APPLICATIONS

- **High Performance Clock Distribution and** Division

- **Wireless Infrastructure**

- **Datacom and Telecom Clock Distribution**

- Medical Imaging

- **Test and Measurement**

- Military / Aerospace

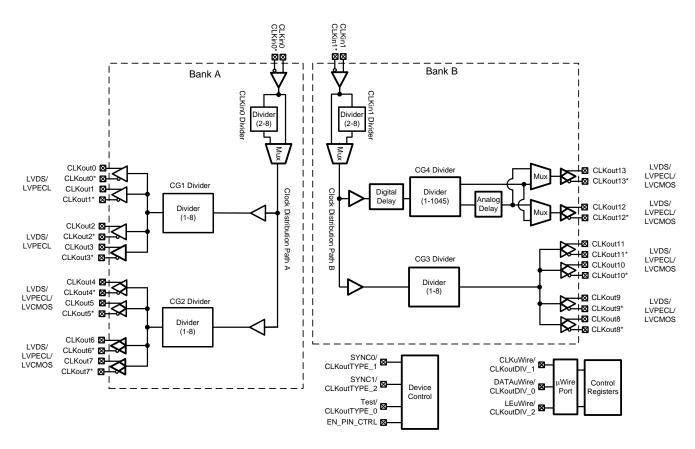

### DESCRIPTION

The LMK01801 is a very low noise solution for clocking systems that require distribution and frequency division of precision clocks.

The LMK01801 features extremely low residual noise, frequency division, digital and analog delay adjustments, and fourteen (14) programmable differential outputs: LVPECL, LVDS and LVCMOS (2 outputs per differential output).

The LMK01801 features two independent inputs that can be driven differentially (LVDS, LVPECL) or in single-ended mode (LVCMOS, RF Sinewave). The first input drives output Bank A consisting of eight (8) outputs. The second input drives output Bank B consisting of six (6) outputs.

# **Functional Configurations**

**Table 1. Clock Output Configurations**

| Bank | Input              | Clock Group | Output<br>CLKoutX/CLK<br>outX* | Output Type            | Outputs in<br>Divider Group | Divider Ratios | Delay                 |

|------|--------------------|-------------|--------------------------------|------------------------|-----------------------------|----------------|-----------------------|

|      | CLKin0/CLKin0      | CG1         | 0 to 3                         | LVDS/LVPECL            | 0 to 3                      | 1 to 8         | No                    |

| Α    | CLKINO/CLKINO<br>* | CG2         | LVDS/LVPECL/                   | 4 to 7                 | 1 to 8                      | No             |                       |

|      | CLIVind (CLIVind   | CG3         | 8 to 11                        | LVDS/LVPECL/<br>LVCMOS | 8 to 11                     | 1 to 8         | No                    |

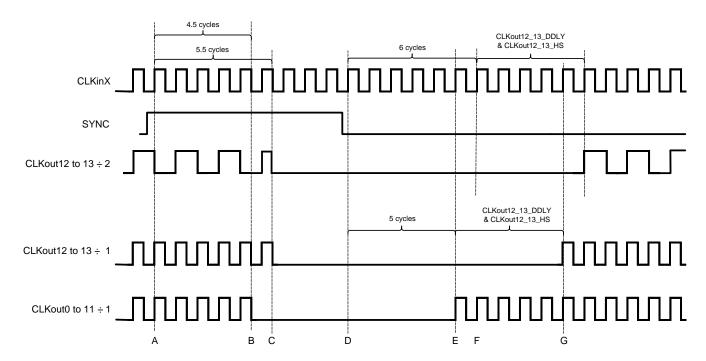

| В    | CLKin1/CLKin1 *    | CG4         | 12 and 13                      | LVDS/LVPECL/<br>LVCMOS | 12 and 13                   | 1 to 1045      | Digital and<br>Analog |

<sup>(1)</sup> Digital Delay will not work if CLKout12\_13\_DIV = 1.

<sup>(2)</sup> See Electrical Characteristics

# Table 2. Pin Control Mode for EN\_PIN\_CTRL = Low

| Pin          | Output Groups                   | Pin=Low | Pin=Middle                  | Pin=High |

|--------------|---------------------------------|---------|-----------------------------|----------|

| CLKoutTYPE_0 | CLKout0 to CLKout3              | LVDS    | Powerdown                   | LVPECL   |

| CLKoutTYPE_1 | CLKout4 to CLKout7              | LVDS    | LVCOMS (Norm/Inv)           | LVPECL   |

| CLKoutTYPE_2 | CLKout8 to CLKout13             | LVDS    | LVCMOS (Norm/Inv)           | LVPECL   |

| CLKoutDIV_0  | CLKout0 to<br>CLKout3 Divider   | ÷ 1     | ÷ 4                         | ÷ 2      |

| CLKoutDIV_1  | CLKout4 to<br>CLKout7 Divider   | ÷ 1     | ÷ 4                         | ÷ 2      |

| CL KoutDIV 2 | CLKout8 to<br>CLKout11 Divider  | ÷ 1     | ÷ 4                         | ÷ 2      |

| CLKoutDIV_2  | CLKout12 to<br>CLKout13 Divider | ÷ 8     | LVCMOS (Norm/Inv)  ÷ 4  ÷ 4 | ÷ 16     |

# Table 3. Pin Control Mode for EN\_PIN\_CTRL = High<sup>(1)(2)</sup>

| Pin            | Output Groups                   | Pin=Low | Pin=Middle        | Pin=High |

|----------------|---------------------------------|---------|-------------------|----------|

| CL KoustTVDE 0 | CLKout0 to CLKout3              | LVDS    | LVPECL            | LVPECL   |

| CLKoutTYPE_0   | CLKout4 to CLkout7              | LVDS    | LVCMOS (Norm/Inv) | LVPECL   |

| CLKoutTYPE_1   | CLKout8 to CLKout11             | LVDS    | LVCMOS (Norm/Inv) | LVPECL   |

| CLKoutTYPE_2   | CLKout12 to CLKout13            | LVDS    | LVCMOS (Norm/Inv) | LVPECL   |

| CLKoutDIV_0    | CLKout0 to<br>CLKout7 Dividers  | ÷ 1     | ÷ 4               | ÷ 2      |

| CLKoutDIV_1    | CLKout8 to<br>CLKout11 Divider  | ÷ 1     | ÷ 4               | ÷ 2      |

| CLKoutDIV_2    | CLKout12 to<br>CLKout13 Divider | ÷ 4     | ÷ 512             | ÷ 16     |

Digital Delay will not work if CLKout12\_13\_DIV = 1. See Electrical Characteristics

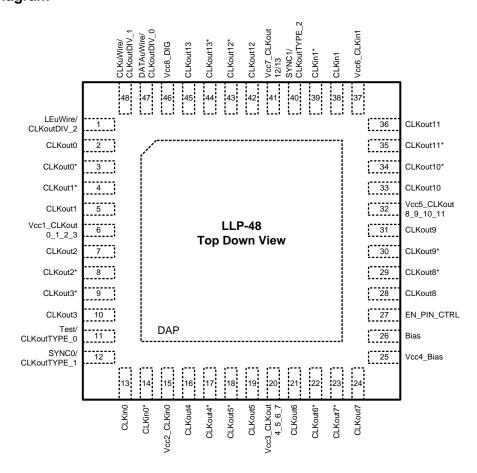

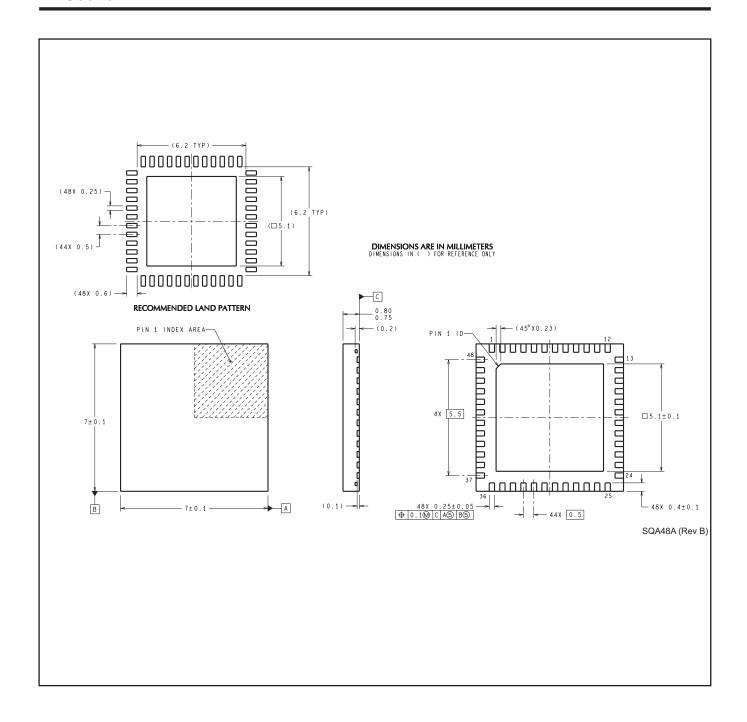

# **Connection Diagram**

Figure 1. 48-Pin Package

### PIN DESCRIPTIONS(1)

| Pin Number | Name(s)                 | I/O | Туре           | Description                                                                                  |

|------------|-------------------------|-----|----------------|----------------------------------------------------------------------------------------------|

| 1          | LEuWire/<br>CLKoutDIV_2 | I   | CMOS / 3-State | MICROWIRE Latch Enable Input /<br>Pin control mode: clock divider 2                          |

| 2, 3       | CLKout0<br>CLKout0*     | 0   | Programmable   | Clock output 0: LVDS or LVPECL                                                               |

| 4, 5       | CLKout1<br>CLKout1*     | 0   | Programmable   | Clock output 1: LVDS or LVPECL                                                               |

| 6          | Vcc1_CLKout<br>0_1_2_3  | I   | PWR            | Power supply for clock outputs 0, 1, 2, and 3                                                |

| 7, 8       | CLKout2,<br>CLKout2*    | 0   | Programmable   | Clock output 2: LVDS or LVPECL                                                               |

| 9. 10      | CLKout3,<br>CLKout3*    | 0   | Programmable   | Clock output 3: LVDS or LVPECL                                                               |

| 11         | Test/<br>CLKoutTYPE_0   | I   | CMOS / 3-State | Reserved Test Pin / Pin control mode: clock output type select 0                             |

| 12         | SYNC0/<br>CLKoutTYPE_1  | I   | CMOS / 3-State | SYNC0 / Pin control mode: clock output type select 1                                         |

| 13, 14     | CLKin0/<br>CLKin0*      | I   | ANLG           | Clock input 0. Supports clocking types including but not limited to LVDS, LVPECL, and LVCMOS |

| 15         | Vcc2_CLKin0             | I   | PWR            | Power supply for clock input 0                                                               |

(1) See Application Information section PIN CONNECTION RECOMMENDATIONS for recommended connections.

Product Folder Links: LMK01801

INSTRUMENTS

# PIN DESCRIPTIONS<sup>(1)</sup> (continued)

| Pin Number | Name(s)                   | I/O | Туре           | Description                                                                                  |

|------------|---------------------------|-----|----------------|----------------------------------------------------------------------------------------------|

| 16, 17     | CLKout4/<br>CLKout4*      | 0   | Programmable   | Clock output 4: LVDS, LVPECL, or LVCMOS                                                      |

| 18, 19     | CLKout5*/<br>CLKout5      | 0   | Programmable   | Clock output 5: LVDS, LVPECL, or LVCMOS                                                      |

| 20         | Vcc3_CLKout<br>4_5_6_7    | I   | PWR            | Power supply for clock outputs 4, 5, 6, and 7                                                |

| 21, 22     | CLKout6/<br>CLKout6*      | 0   | Programmable   | Clock output 6: LVDS, LVPECL, or LVCMOS                                                      |

| 23, 24     | CLKout7*/<br>CLKout7      | 0   | Programmable   | Clock output 7: LVDS, LVPECL, or LVCMOS                                                      |

| 25         | Vcc4_Bias                 | I   | PWR            | Power supply for Bias                                                                        |

| 26         | Bias                      |     | ANLG           | Bias bypass pin                                                                              |

| 27         | EN_PIN_CTRL               | I   | 3-State        | Select MICROWIRE or pin control mode                                                         |

| 28, 29     | CLKout8/<br>CLKout8*      | 0   | Programmable   | Clock output 8: LVDS, LVPECL, or LVCMOS                                                      |

| 30, 31     | CLKout9*/<br>CLKout9      | 0   | Programmable   | Clock output 9: LVDS, LVPECL, or LVCMOS                                                      |

| 32         | Vcc5_CLKout<br>8_9_10_11  | 1   | PWR            | Power supply for clock outputs 8, 9, 10, and 11                                              |

| 33, 34     | CLKout10/<br>CLKout10*    | 0   | Programmable   | Clock output 10: LVDS, LVPECL, or LVCMOS                                                     |

| 35, 36     | CLKout11*/<br>CLKout11    | 0   | Programmable   | Clock output 11: LVDS, LVPECL, or LVCMOS                                                     |

| 37         | Vcc6_CLKin1               | - 1 | PWR            | Power supply for clock input 1                                                               |

| 38, 39     | CLKin1/<br>CLKin1*        | 1   | ANLG           | Clock input 1. Supports clocking types including but not limited to LVDS, LVPECL, and LVCMOS |

| 40         | SYNC1/<br>CLKoutTYPE_2    | 1   | CMOS / 3-State | SYNC pin for CLKin1 and bank B. Pin control mode: Clock output type select 2                 |

| 41         | Vcc7_CLKout<br>12_13      | 1   | PWR            | Power supply for clock outputs 12, and 13                                                    |

| 42, 43     | CLKout12/<br>CLKout12*    | 0   | Programmable   | Clock output 12: LVDS, LVPECL, or LVCMOS                                                     |

| 44, 45     | CLKout13*/<br>CLKout13    | 0   | Programmable   | Clock output 13: LVDS, LVPECL, or LVCMOS                                                     |

| 46         | Vcc8_DIG                  | 1   | PWR            | Power supply for digital                                                                     |

| 47         | DATAuWire/<br>CLKoutDIV_0 | 1   | CMOS / 3-State | MICROWIRE DATA Pin / Pin control mode: Clock divider 0                                       |

| 48         | CLKuWire/<br>CLKoutDIV_1  | 1   | CMOS / 3-State | MICROWIRE CLK Pin / Pin control mode: Clock divider 1                                        |

| DAP        | DAP                       |     | GND            | DIE ATTACH PAD, connect to GND                                                               |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)(3)(4)

| Parameter                              | Symbol           | Ratings                         | Units |

|----------------------------------------|------------------|---------------------------------|-------|

| Supply Voltage (5)                     | V <sub>CC</sub>  | -0.3 to 3.6                     | V     |

| Input Voltage                          | V <sub>IN</sub>  | -0.3 to (V <sub>CC</sub> + 0.3) | V     |

| Storage Temperature Range              | T <sub>STG</sub> | -65 to 150                      | °C    |

| Lead Temperature (solder 4 seconds)    | T <sub>L</sub>   | +260                            | °C    |

| Differential Input Current (CLKinX/X*) | I <sub>IN</sub>  | ± 5                             | mA    |

| Moisture Sensitivty Level              | MSL              | 3                               |       |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only to the test conditions listed.

- (2) This device is a high performance RF integrated circuit with an ESD rating up to 2.5 kV Human Body Model, up to 250 V Machine Model and up to 1,250 V Charged Device Model and is ESD sensitive. Handling and assembly of this device should only be done at ESD-free workstations.

- (3) Stresses in excess of the absolute maximum ratings can cause permanent or latent damage to the device. These are absolute stress ratings only. Functional operation of the device is only implied at these or any other conditions in excess of those given in the operation sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

- (4) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (5) Never to exceed 3.6 V.

# **Package Thermal Resistance**

#### 48-Lead WQFN

| Parameter                                                                         | Symbol        | Ratings | Units |

|-----------------------------------------------------------------------------------|---------------|---------|-------|

| Thermal resistance from junction to ambient on 4-layer JEDEC board <sup>(1)</sup> | $\theta_{JA}$ | 26      | °C/W  |

| Thermal resistance from junction to case (2)                                      | $\theta_{JC}$ | 3       | °C/W  |

<sup>(1)</sup> Specification assumes 9 thermal vias connect the die attach pad to the embedded copper plane on the 4-layer JEDEC board. These vias play a key role in improving the thermal performance of the WQFN. It is recommended that the maximum number of vias be used in the board layout.

# **Recommended Operating Conditions**

| Parameter               | Symbol          | Condition               | Min  | Typical | Max  | Unit |

|-------------------------|-----------------|-------------------------|------|---------|------|------|

| Ambient<br>Temperature  | T <sub>A</sub>  | V <sub>CC</sub> = 3.3 V | -40  | 25      | 85   | °C   |

| Supply Voltage          | V <sub>CC</sub> |                         | 3.15 | 3.3     | 3.45 | V    |

| Junction<br>Temperature | T <sub>J</sub>  |                         |      |         | 125  | °C   |

<sup>(2)</sup> Case is defined as the DAP (die attach pad).

# **Electrical Characteristics**

$(3.15 \text{ V} \le \text{V}_{CC} \le 3.45 \text{ V}, -40 \text{ °C} \le \text{T}_{A} \le 85 \text{ °C}.$  Typical values represent most likely parametric norms at  $\text{V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25 \text{ °C},$  at the Recommended Operating Conditions at the time of product characterization and are not guaranteed.)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Symbol                              | Parameter                                             | Conditions                           | Min       | Тур    | Max             | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|--------------------------------------|-----------|--------|-----------------|-------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                   |                                                       | Current Consumption                  |           |        |                 |       |

| CC_CLKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I <sub>CC_PD</sub>                  | Power Down Supply Current                             |                                      |           | 1      |                 | mA    |

| CLKINX_MUX = Bypassed   CLKOUX_Y_DIV = 1   0.001   3100   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600   1600  | I <sub>CC_CLKS</sub>                | Supply Current with all clocks enabled <sup>(1)</sup> | $CLKoutX_Y_DIV = 1,$                 |           | 313    | 390             | mA    |

| CLKoutX_Y_DIV = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                     | CLKin0/                                               | 0* and CLKin1/1* Input Clock Specifi | cations   |        |                 |       |

| CLKINX   CLKIN   CLKIN   CLKIN   CLKINX   CLKI |                                     |                                                       |                                      | 0.001     |        | 3100            | MHz   |

| CLKINX_DIV = 1 to 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f <sub>CLKinX</sub>                 | Clock 0 or 1 Input Frequency                          |                                      | .001      |        | 1600            | MHz   |

| DUTY_CLKin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                     | W <sub>CLKin</sub> Slew Rate on CLKin <sup>(2)</sup>  |                                      | .001      |        | 3100            | MHz   |

| Vclkin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SLEW <sub>CLKin</sub>               | Slew Rate on CLKin (2)                                | 20% to 80%                           | 0.15      | 0.5    |                 | V/ns  |

| V_{CLKin}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DUTY <sub>CLKin</sub>               | Clock input duty cycle                                |                                      |           | 50     |                 | %     |

| VipCLKin   VipCLKin  | V                                   | Clock Input,                                          | coupled to Ground                    | 0.25      |        | 2.4             | Vpp   |

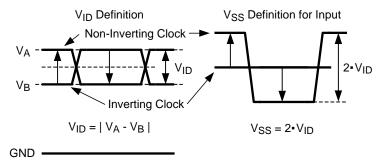

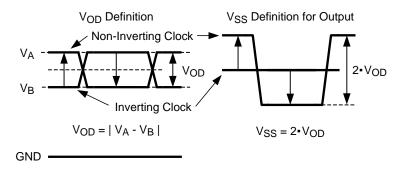

| VSSCLKin   VIDCLKin   VIDCLKin   Differential Input Voltage (3) (4)   AC coupled (CLKinX_BUF_TYPE = MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V CLKin                             | Single-ended Input Voltage                            | coupled to Ground                    | 0.25      |        | 2.4             | Vpp   |

| V <sub>ID</sub> CLK <sub>in</sub>   Differential Input Voltage (3) (4)   AC coupled (CLKinX_BUF_TYPE = MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $V_{ID}CLK_{in}$                    |                                                       | AC coupled                           | 0.25      |        | 1.55            | V     |

| V <sub>SS</sub> CLK <sub>in</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>SS</sub> CLK <sub>in</sub>   | Clock Input                                           |                                      | 0.5       |        | 3.1             | Vpp   |

| VCLKinX-offset   DC offset voltage between   CLKinX/CLKinX*   CLKinX   CLKinX   CLKinX   CLKinX   CLKinX   CLKinX   CLKinX   CLKinX   DC coupled to CLKinX; CLKinX*   AC   Coupled to Ground   CLKinX-BUF_TYPE   Bipolar   O   O.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_{ID}CLK_{in}$                    | Differential Input Voltage (3) (4)                    | AC coupled                           | 0.25      |        | 1.55            | V     |

| VCLKinX-offset         CLKinX/CLKinX* CLKinX         CLKinX_BUF_TYPE = Bipolar         0           VCLKin-VIH         Maximum input voltage         DC coupled to CLKinX; CLKinX* AC coupled to Ground CLKinX_BUF_TYPE = MOS         0.0         0.4           VCLKin-VIL         Minimum input voltage         Each pin AC coupled CLKinX_BUF_TYPE = MOS         0.0         0.4           DC offset voltage between CLKinX/CLKinX* CLKinXX* CLKinX* DTYPE = MOS         55         55           Digital Inputs (CLKuWire, DATAuWire, LEuWire) for EN_PIN_CTRL = MIDDLE           VIH         High-Level Input Voltage         1.2         VCC           VIL         Low-Level Input Voltage         0.4         0.4           IIH         High-Level Input Current         VIH = VCC         -5         5           Digital Inputs (SYNC0, SYNC1) for EN_PIN_CTRL = MIDDLE           VIH         High-Level Input Current         VIH = VCC         -5         5           VIL         Low-Level Input Voltage         1.2         VCC           VIL         Low-Level Input Current         VIH = VCC         -5         5           VIL         Low-Level Input Current         VIH = VCC         -5         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_{SS}CLK_{in}$                    |                                                       | (CLKinX_BUF_TYPE = MOS               | 0.5       |        | 3.1             | Vpp   |

| V_{CLKinX-offset   CLKinX  CLKinX  CLKinX_BUF_TYPE = Bipolar   D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |                                                       | Fach pin AC coupled                  |           | 0      |                 | mV    |

| V <sub>CLKin</sub> .V <sub>IL</sub> Minimum input voltage         Coupled to Ground CLKinX_BUF_TYPE = MOS         0.0         0.4           V <sub>CLKin</sub> .V <sub>IL</sub> DC offset voltage between CLKinX/CLKinX* CLKinX* CLKinX* CLKinX BUF_TYPE = MOS         55         55           Digital Inputs (CLKuWire, DATAuWire, LEuWire) for EN_PIN_CTRL = MIDDLE           V <sub>IH</sub> High-Level Input Voltage         1.2         V <sub>CC</sub> V <sub>IL</sub> Low-Level Input Voltage         0.4         0.4           I <sub>IH</sub> High-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5           Digital Inputs (SYNC0, SYNC1) for EN_PIN_CTRL = MIDDLE           V <sub>IH</sub> High-Level Input Voltage         1.2         V <sub>CC</sub> V <sub>IL</sub> Low-Level Input Voltage         1.2         V <sub>CC</sub> I <sub>IH</sub> High-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5           I <sub>IH</sub> High-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>CLKinX-offset</sub>          |                                                       |                                      |           | 0      |                 | mV    |

| V <sub>CLKin-</sub> V <sub>IL</sub> Minimum input voltage         CLKinX_BUF_TYPE = MOS         0.0         0.4           V <sub>CLKinX-offset</sub> DC offset voltage between CLKinX/CLKinX* CLKinX*         Each pin AC coupled CLKinX_BUF_TYPE = MOS         55           Digital Inputs (CLKuWire, DATAuWire, LEuWire) for EN_PIN_CTRL = MIDDLE           V <sub>IH</sub> High-Level Input Voltage         1.2         V <sub>CC</sub> V <sub>IL</sub> Low-Level Input Voltage         0.4         0.4           I <sub>IH</sub> High-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5           Digital Inputs (SYNC0, SYNC1) for EN_PIN_CTRL = MIDDLE           V <sub>IH</sub> High-Level Input Voltage         1.2         V <sub>CC</sub> V <sub>IL</sub> Low-Level Input Voltage         0.4           I <sub>IH</sub> High-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5           I <sub>IH</sub> High-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $V_{CLKin}V_{IH}$                   | Maximum input voltage                                 |                                      | 2.0       |        | V <sub>CC</sub> | V     |

| DC offset voltage between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>CLKin-</sub> V <sub>IL</sub> | Minimum input voltage                                 |                                      | 0.0       |        | 0.4             | V     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CLKinX-offset</sub>          | CLKinX/CLKinX*                                        | Each pin AC coupled                  |           | 55     |                 | mV    |

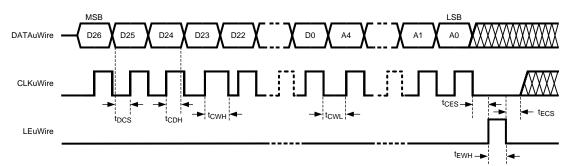

| V <sub>IL</sub> Low-Level Input Voltage         0.4           I <sub>IH</sub> High-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5           Digital Inputs (SYNC0, SYNC1) for EN_PIN_CTRL = MIDDLE           V <sub>IH</sub> High-Level Input Voltage         1.2         V <sub>CC</sub> V <sub>IL</sub> Low-Level Input Voltage         0.4           I <sub>IH</sub> High-Level Input Current V <sub>IH</sub> = V <sub>CC</sub> -5         5           Low-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                     | Digital Inputs (CLKu                                  | Wire, DATAuWire, LEuWire) for EN_F   | IN_CTRL = | MIDDLE |                 |       |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>IH</sub>                     | High-Level Input Voltage                              |                                      | 1.2       |        | V <sub>CC</sub> | V     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>IL</sub>                     | Low-Level Input Voltage                               |                                      |           |        | 0.4             | V     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>IH</sub>                     | High-Level Input Current                              | $V_{IH} = V_{CC}$                    | -5        |        | 5               | μΑ    |

| V <sub>IH</sub> High-Level Input Voltage         1.2         V <sub>CC</sub> V <sub>IL</sub> Low-Level Input Voltage         0.4           I <sub>IH</sub> High-Level Input Current V <sub>IH</sub> = V <sub>CC</sub> -5         5           Low-Level Input Current         V <sub>IH</sub> = V <sub>CC</sub> -5         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>IL</sub>                     | Low-Level Input Current                               | V <sub>IL</sub> = 0                  | -5        |        | 5               | μA    |

| V <sub>IL</sub> Low-Level Input Voltage         0.4           I <sub>IH</sub> High-Level Input Current V <sub>IH</sub> = V <sub>CC</sub> V <sub>IH</sub> = V <sub>CC</sub> -5         5           Low-Level Input Current         V <sub>II</sub> = 0         -40         -5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     | Digital Inpu                                          | ts (SYNC0, SYNC1) for EN_PIN_CTRL    | = MIDDLE  |        |                 |       |

| $I_{IH}$ High-Level Input Current $V_{IH} = V_{CC}$ -5 5 Low-Level Input Current $V_{II} = 0$ -40 -5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>IH</sub>                     | High-Level Input Voltage                              |                                      | 1.2       |        | V <sub>CC</sub> | V     |

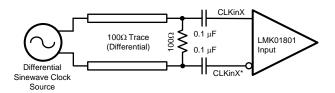

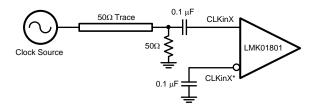

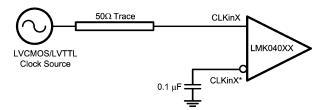

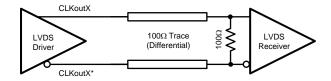

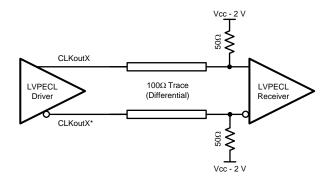

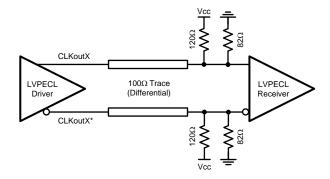

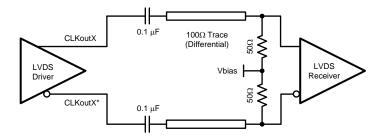

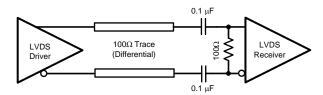

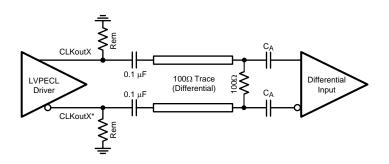

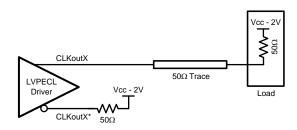

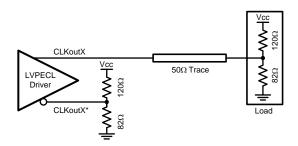

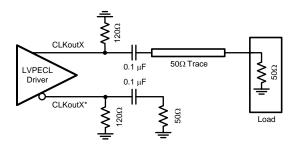

| $V_{\text{IH}} = V_{\text{CC}}$ $V_{\text{IH}} = V_{\text{CC}}$ $V_{\text{CC}} = 0$ $V_{\text{CC}} = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{IL}$                            | Low-Level Input Voltage                               |                                      |           |        | 0.4             | V     |