# QUADRATURE CLOCK CONVERTER

# FEATURES:

- x1, x2 and x4 mode selection

- Up to 16 MHz output clock frequency

- INDEX input and output

- UP/DOWN indicator output

- Programmable output clock pulse width

- On-chip filtering of inputs for optical or

- magnetic encoder applications.

- TTL and CMOS compatible I/Os

- +4.5V to +10.0V operation (VDD-VSS)

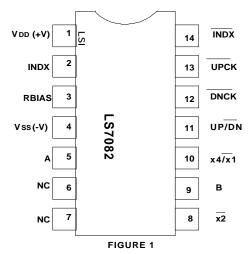

- LS7082 (DIP); LS7082-S (SOIC ) See Figure 1

# **DESCRIPTION:**

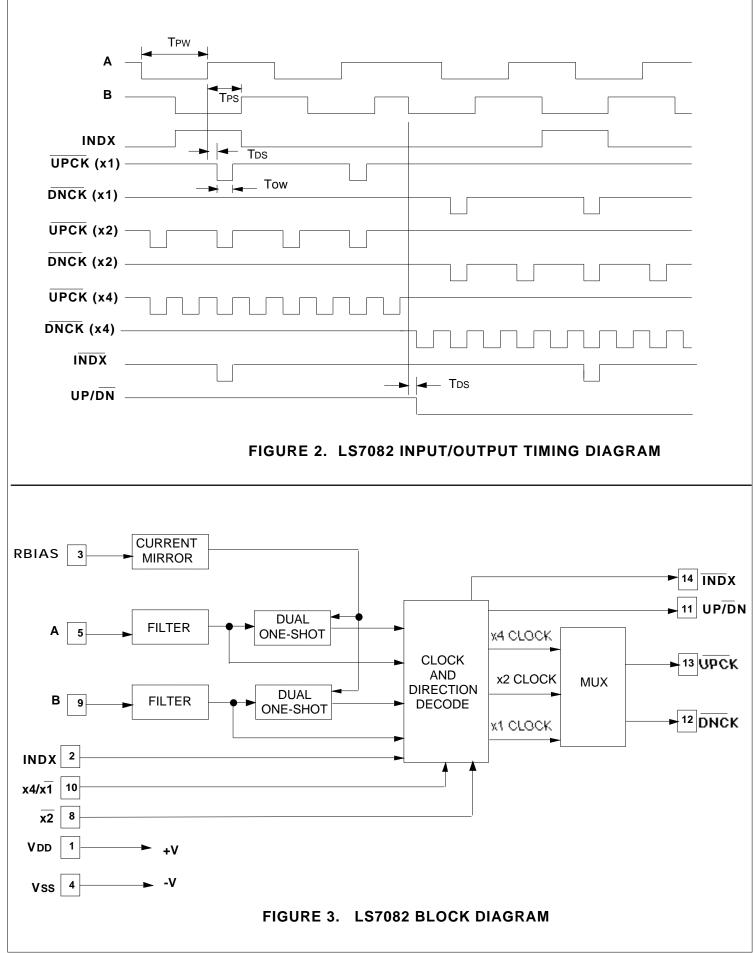

The LS7082 is a monolithic CMOS silicon gate quadrature clock converter. Quadrature clocks derived from optical or magnetic encoders, when applied to the A and B Inputs of the LS7082, are converted to strings of Up Clocks and Down Clocks. Pulses derived from the Index Track of an encoder, when applied to the INDX input, produce absolute position reference pulses which are synchronized to the Up Clocks and Down Clocks. These outputs can be interfaced directly with standard Up/Down counters for direction and position sensing of the encoder.

# **INPUT/OUTPUT DESCRIPTION:**

**VDD** (Pin 1) Supply Voltage positive terminal.

# INDX (Pin 2)

Encoder Index pulses are applied to this input.

# RBIAS (Pin 3)

Input for external component connection. A resistor connected between this input and Vss adjusts the output clock pulse width (Tow). For proper operation, the output clock pulse width must be less than or equal to the A,B pulse separation (Tow TPs).

# Vss (Pin 4)

Supply Voltage negative terminal.

# A (Pin 5)

Quadrature Clock Input A. This input has a filter circuit to validate input logic level and eliminate encoder dither.

# **x2** (Pin 8)

A low level applied to this input selects x2 mode of operation. See Table 1 for Mode Selection Truth Table and Figure 2 for Input/Output timing relationship.

# **B** (Pin 9)

Quadrature Clock Input B. This input has a filter circuit identical to input A.

#### PIN ASSIGNMENT - TOP VIEW

October 2000

# TABLE 1. MODE SELECTION TRUTH TABLE

| x2 Input | x4/x1 Input | MODE |  |  |

|----------|-------------|------|--|--|

| 0        | Don't Care  | x2   |  |  |

| 1        | 0           | x1   |  |  |

| 1        | 1           | x4   |  |  |

|          |             |      |  |  |

# **x4/x1** (Pin 10)

This input selects between x1 and x4 modes of operation. See Table 1 for Mode Selection Truth Table and Figure 2 for Input/Output timing relationship.

# **UP/DN** (Pin 11)

The count direction at any instant is indicated at this output. An UP count direction is indicated by a high, and a DOWN count direction is indicated by a low (See Figure 2).

# DNCK (Pin 12)

This DOWN Clock output consists of low-going pulses generated when A input lags the B input (See Figure 2).

# **UPCK** (Pin 13)

This UP Clock output consists of low-going pulses generated when A input leads the B input (See Figure 2).

# **INDX** (Pin 14)

This output consists of low-going pulses generated by clock transitions at the A input when INDX input is high and B input is low (See Figure 2).

NOTE: All unused input pins must be tied to VDD or Vss.

| ABSOLUTE MAXIMUM RATING                                                                                          |               |          |              |          |             |                                              |  |  |  |

|------------------------------------------------------------------------------------------------------------------|---------------|----------|--------------|----------|-------------|----------------------------------------------|--|--|--|

| PARAMETER                                                                                                        | SYMBOL        | SYMBOL V |              | UNITS    |             |                                              |  |  |  |

| DC Supply Voltage                                                                                                | Vdd - Vss     |          | 11.0         | V        |             |                                              |  |  |  |

| Voltage at any input                                                                                             | Vin           |          | 3 to VDD +.3 |          |             |                                              |  |  |  |

| Operating temperature                                                                                            | TA            |          | ) to +70     | °C       |             |                                              |  |  |  |

| Storage temperature                                                                                              | perature TSTG |          | 5 to +150    | °C       |             |                                              |  |  |  |

| <b>DC ELECTRICAL CHARACTERISTICS:</b><br>(All voltages referenced to Vss, TA = $0^{\circ}$ C to $70^{\circ}$ C.) |               |          |              |          |             |                                              |  |  |  |

| (All voltages referenced to VSS, 1)                                                                              | A = 0 C to 70 | C.)      |              |          |             |                                              |  |  |  |

| PARAMETER                                                                                                        | SYMBOL        | MIN      | MAX          | UNITS    | CON         | DITION                                       |  |  |  |

| Supply voltage                                                                                                   | VDD           | 4.5      | 10.0         | V        | -           |                                              |  |  |  |

| Supply current                                                                                                   | IDD           | -        | 6.0          | μΑ       | input       | = 10.0V, All<br>frequencies = 0 Hz<br>S = 2M |  |  |  |

| (4/x1, x2, INDX Logic Low                                                                                        | VIL           | -        | 0.3Vdd       | V        | -           |                                              |  |  |  |

| A,B Logic Low                                                                                                    | VIL           | -        | 0.6          | V        | Vdd =       | = 4.5V                                       |  |  |  |

| -                                                                                                                |               | -        | 1.0          | V        | Vdd =       | = 9V                                         |  |  |  |

|                                                                                                                  |               | -        | 1.1          | V        | Vdd =       | = 10.0V                                      |  |  |  |

| x4/x1, x2, INDX Logic High                                                                                       | Vін           | 0.7Vdd   | -            | V        | -           |                                              |  |  |  |

| <b>A,B</b> Logic High                                                                                            | ViH           | 3.1      | -            | V        | Vdd =       | = 4.5V                                       |  |  |  |

|                                                                                                                  |               | 5.0      | -            | V        | Vdd =       | = 9V                                         |  |  |  |

|                                                                                                                  |               | 5.6      | -            | V        | VDD = 10.0V |                                              |  |  |  |

| ALL OUTPUTS:                                                                                                     |               |          |              |          |             |                                              |  |  |  |

| Sink Current                                                                                                     | IOL           | 1.75     | -            | mA       | Vdd =       | = 4.5V                                       |  |  |  |

| VOL = 0.4V                                                                                                       |               | 5.0      | -            | mA       | Vdd =       | = 9V                                         |  |  |  |

|                                                                                                                  |               | 5.7 -    |              | mA       | VDD = 10.0V |                                              |  |  |  |

| Source Current                                                                                                   | Юн            | 1.0 -    |              | mA       | Vdd = 4.5V  |                                              |  |  |  |

| Voн = Vdd - 0.5V                                                                                                 |               | 2.5      | -            | mA       | Vdd =       | = 9V                                         |  |  |  |

|                                                                                                                  |               | 3.0      | -            | mA       | VDD = 10.0V |                                              |  |  |  |

| TRANSIENT CHARACTERISTICS                                                                                        | :             |          |              |          |             |                                              |  |  |  |

| $(TA = 0^{\circ}C \text{ to } 70^{\circ}C)$                                                                      |               |          |              |          |             |                                              |  |  |  |

| PARAMETER                                                                                                        | SYMBOL        |          | MIN          | MAX      | UNITS       | CONDITION                                    |  |  |  |

| <b>A,B</b> inputs:<br>Validation Delay                                                                           | Tvd           |          | _            | 85       | ns          | VDD = 10.0V                                  |  |  |  |

| Validation Delay                                                                                                 | IVD           |          | -            | 100      | ns          | VDD = 10.0V<br>VDD = 9V                      |  |  |  |

|                                                                                                                  |               |          | -            | 160      | ns          | VDD = 3.0<br>VDD = 4.5V                      |  |  |  |

| A,B inputs:                                                                                                      |               |          |              |          |             |                                              |  |  |  |

| Pulse Width                                                                                                      | TPW           | Τv       | D+TOW        | Infinite | ns          | -                                            |  |  |  |

| A to B or B to A                                                                                                 |               | Tow I    |              |          |             |                                              |  |  |  |

| Phase Delay                                                                                                      | TPS           |          |              | Infinite | ns          | -                                            |  |  |  |

|                                                                                                                  |               |          |              | 1        |             |                                              |  |  |  |

| A,B frequency                                                                                                    | fА,В          | -        |              | 2TPW     | Hz          | -                                            |  |  |  |

|                                                                                                                  | n ,,D         |          |              | <b>,</b> |             |                                              |  |  |  |

| Input to Output Delay                                                                                            | TDS           |          | -            | 120      | ns          | Vdd = 10.0V                                  |  |  |  |

|                                                                                                                  |               | -        |              | 150      | ns          | VDD = 9V                                     |  |  |  |

|                                                                                                                  |               |          | -            | 235      | ns          | VDD = 4.5V                                   |  |  |  |

|                                                                                                                  |               |          |              |          | 10          | Includes input                               |  |  |  |

|                                                                                                                  |               |          |              |          |             | validation delay                             |  |  |  |

|                                                                                                                  |               |          |              |          |             |                                              |  |  |  |

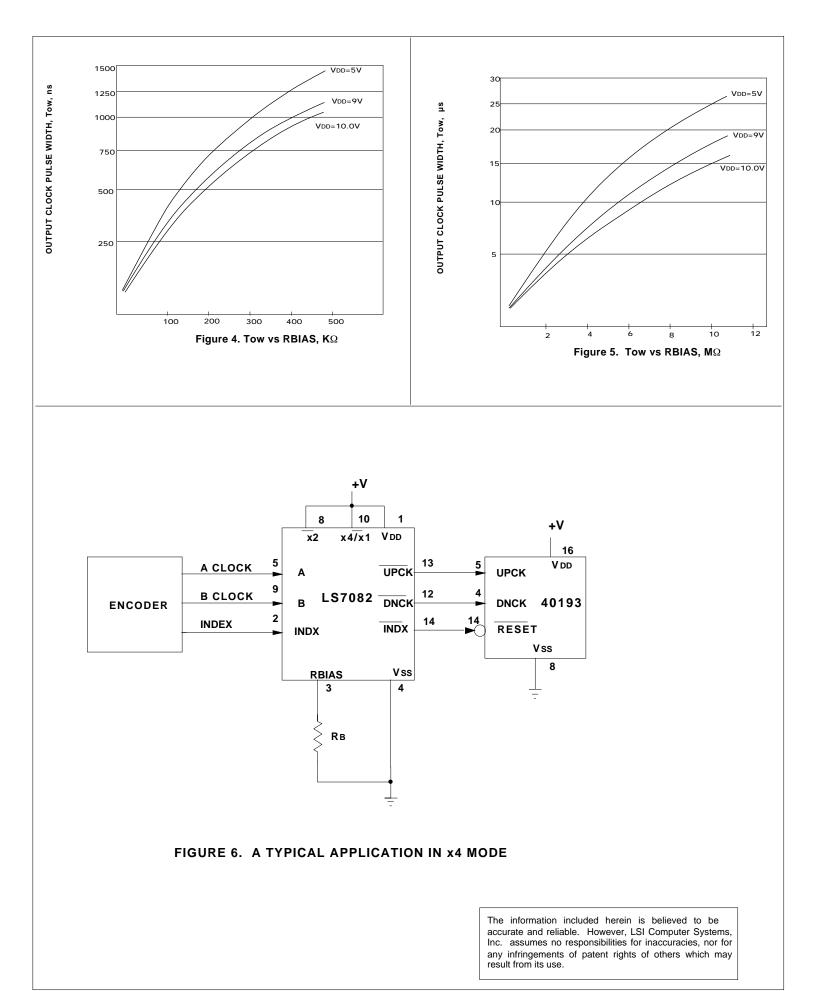

| Output Clock Pulse Width                                                                                         | Tow           |          | 50           | -        | ns          | See Fig. 4 & 5                               |  |  |  |

|                                                                                                                  |               |          |              |          |             |                                              |  |  |  |

7082-100100-3