#### DESCRIPTION

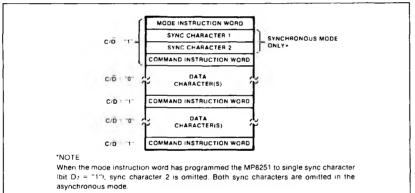

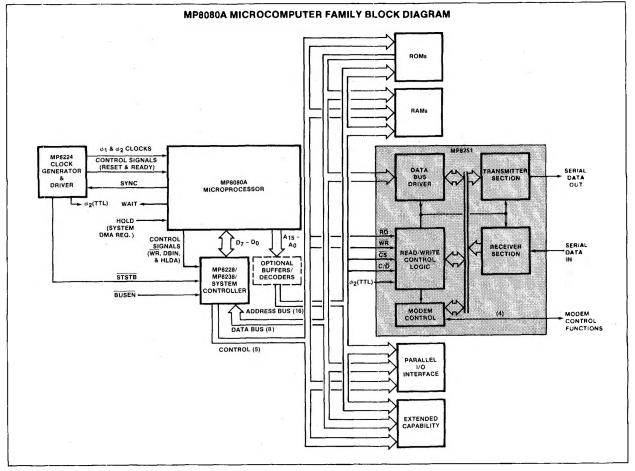

The MP8251 is a programmable Universal Synchronous/Asynchronous Receiver/ Transmitter (USART) chip contained in a standard 28-pin dual-in-line package. The chip, which is fabricated using N-channel silicon gate technology, functions as a serial data input/output interface in the MP8080A microcomputer family. The functional configuration of the MP8251 is programmed by the system software for maximum flexibility, thereby allowing the system to receive and transmit virtually any serial data communication signal presently in use (including IBM Bisync).

The MP8251 can be programmed to receive and transmit either synchronous or asynchronous serial data. The MP8251 performs serial-to-parallel conversion on data characters received from an input/output device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete status of the MP8251 at any time during the functional operation. Status information reported includes the type and the condition of the transfer operations being performed by the MP8251, as well as any transmission error conditions (parity, overrun, or framing).

#### FEATURES

- Synchronous and asynchronous full duplex operations

Synchronous Mode Canabilities

- Synchronous Mode Capabilities Selectable 5- to 8-Bit characters Internal or external character synchronization

- Automatic sync insertion • Asynchronous mode capabilities Selectable 5- to 8-Bit characters 3 selectable clock rates (1x, 16x or 64x the baud rate)

Line break detection and generation 1-, 11/2-, or 2-Stop bit detection and generation

False start bit detection

- Baud rates

- DC to 56k baud (synchronous mode) DC to 9.6k baud (asynchronous mode)

- Transmission error detection capabilities

Parity

- Overrun

- Framing

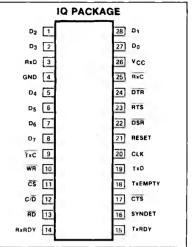

#### PIN CONFIGURATION

MP8251

MP8251-I

· Double buffering of data

- TTL compatible

- Single TTL clock

- Reduces system component count

### PIN DESIGNATION

| MNEMONIC | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ĈŜ       | 1    | Chip select: When low (logic 0), the chip is selected. This enables com-<br>munication between the MP8251 and the MP8080A microprocessor.                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| RD       | 1.1  | <b>Read:</b> When low, allows the MP8080A to read data or status information from the MP8251.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| WR       | 1    | Write: When low, allows the MP8080A to write data or control words into the MP8251.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| C/D      | 1    | <b>Control/data:</b> Used in conjunction with an active RD or WR input (logic 0) to determine overall device operation as indicated below.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|          |      | CS C/D RD WR OPERATION                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|          |      | 0001Data character read from MP82510010Data character written into MP82510101Status information read from MP82510110Control word written into MP82511xxxDevice not selected                                                                                                                                                                                                                                      |  |  |  |  |  |

| RESET    |      | <b>Reset:</b> When high (logic 1), places the MP8251 in the idle mode. The device remains in this mode until a new set of control words is written into the MP8251 to program its functional definition. Minimum Reset pulse width is 6 t <sub>CY</sub> .                                                                                                                                                        |  |  |  |  |  |

| CLK      |      | <b>Clock:</b> TTL clock that is used to generate internal timing signals for the MP8251. The minimum frequency of the CLK input is 30 times the receiver/transmitter clock frequency for the synchronous mode, and 4.5 times the receiver/transmitter clock frequency for the asynchronous mode. The CLK input is normally connected to the $\phi_2$ (TTL) output of the 8224 Clock Generator and Driver device. |  |  |  |  |  |

| DSR      |      | <b>Data set ready:</b> General purpose input whose condition can be tested<br>by the MP8080A using a status read operation. However, a low level<br>DSR input is normally used to test data set ready conditions.                                                                                                                                                                                                |  |  |  |  |  |

| CTS      | 1    | <b>Clear to send:</b> If low when the TxEn bit ( $D_0$ ) of the command Instruction Control Word (see figure) is set high, enables the MP8251 to transmit                                                                                                                                                                                                                                                        |  |  |  |  |  |

signetics

MP8251-I

MP8251

#### PIN DESIGNATION (Cont'd)

| MNEMONIC | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

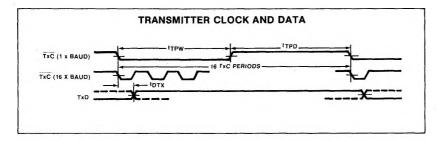

| TxC      | I    | <b>Transmitter Clock:</b> This clock input controls the rate at which a data character is to be transmitted. The frequency of the TxC input is equal to the baud rate for the synchronous mode, and is a multiple (1x, 16x or $64x$ ) of the baud rate for the asynchronous mode. A portion of the Mode Instruction Word (see figure) selects the value of the baud rate factor when in the asynchronous mode. Transmitter data are clocked out of the MP8251 on the falling edge of the TxC input. |

| RxD      | 1    | <b>Receiver data:</b> Serial data input from a MODEM or an input/output device.                                                                                                                                                                                                                                                                                                                                                                                                                     |

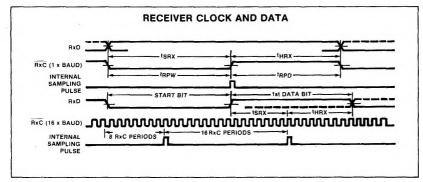

| RxC      |      | <b>Receiver clock:</b> This clock input controls the rate at which a data character is to be received. The frequency and selection of the RxC input is as described above for the TxC input. Receiver data are clocked into the MP8251 on the rising edge of the RxC input.                                                                                                                                                                                                                         |

| Vcc      | 1    | +5V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GND      |      | Ground: 0-V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DTR      | 0    | <b>Data terminal ready</b> General purpose output which can be set to an active low by programming the DTR bit (D <sub>1</sub> ) of the Command Instruction Control Word. However, a low level DTR output is normally used for data terminal ready or rate select control.                                                                                                                                                                                                                          |

| RTS      | 0    | <b>Request to send:</b> General purpose output which can be set to an active low by programming the RTS bit ( $D_5$ ) of the Command Instruction Control Word. However, the RTS output is normally used for request to send control in the transmit mode.                                                                                                                                                                                                                                           |

| TxD      | 0    | <b>Transmitter data:</b> Composite serial data output to a MODEM or input/output device. The TxD output is held in the marking state (logic 1) upon a Reset operation.                                                                                                                                                                                                                                                                                                                              |

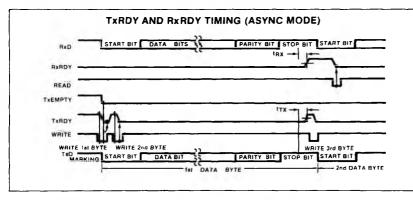

| TxRDY    | 0    | <b>Transmitter ready:</b> When high, alerts the MP8080A that the transmitter is ready to accept a data character. The TxRDY output, which is automatically reset whenever a character is written into the MP8251, can be used as an interrupt to the system. For polled operation, the condition of the TxRDY signal can be tested by the MP8080A using a status read operation.                                                                                                                    |

| TxE      | 0    | <b>Transmitter empty:</b> Goes high to indicate the end of a transmit mode.<br>The TxE output is automatically reset whenever a character is written<br>into the MP8251. In the synchronous mode, a high-level TxE output<br>indicates that a character has not been loaded, the transmitter buffer is<br>empty, and the sync character(s) of a data block are soon to be<br>transmitted automatically as fillers.                                                                                  |

| RxRDY    | 0    | <b>Receiver ready:</b> When high, alert the MP8080A that the receiver contains a data character that is ready to be input to the CPU. The RxRDY output, which is automatically reset whenever a character is read from the MP8251, can be used as an interrupt to the system. For polled operation, the condition of the RxRDY signal can be tested by the MP8080A using a status read operation.                                                                                                   |

| D7-D0    | 1/0  | <b>Data bus:</b> This bus comprises eight Tri-state input/output lines. The bus provides bidirectional communications between the MP8251 and the MP8080A. Data are routed to or from the internal data bus buffer upon execution of an MP8080A OUT or IN instruction, respectively. In addition, control words, command words and status information are transferred through the data bus buffer.                                                                                                   |

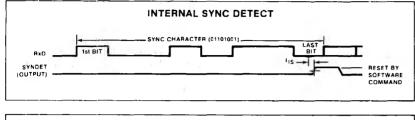

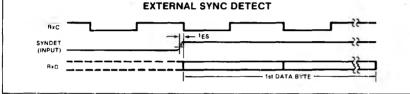

| SYNDET   | 1/0  | <b>Sync detect:</b> This pin may be used in the synchronous mode only.<br>System software can program SYNDET as either an input or an output.<br>When used as an output (Internal sync detect mode), a high level<br>SYNDET output is automatically reset upon a status read operation by<br>the MP8080A. When used as an input (external sync detect mode) a<br>high level SYNDET causes the MP8251 to start assembling data<br>characters on the falling edge of the next RxC input.              |

### signetics

MP8251-I

MP8251

#### **ABSOLUTE MAXIMUM RATINGS\***

|      | PARAMETER                                 | RATING      | UNIT |

|------|-------------------------------------------|-------------|------|

| TA   | Ambient temperature under bias            | 0 to +70    | °C   |

| TSTG | Storage temperature                       | -65 to +150 | °C   |

|      | Voltage on any pin with respect to ground | -0.5 to +7  | V    |

| PD   | Power dissipation                         | 1           | W    |

**NOTE**

Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under dc electrical characteristics.

#### **BLOCK DIAGRAMS**

MP8251-I

MP8251

#### **TEST LOAD CIRCUIT** BLOCK DIAGRAMS (Cont'd) MP8251 INTERNAL DATA BUS 2V \$ 510 \$ DATA (19) TxD TRANSMIT BUFFER D7 - D0 (27.28.1. 2. & 5-8) BUS Φ DEVICE UNDER ᆂᅂ € 24k (21) 4 Ŧ RESET -(15) (20) TARDY CLK -READ/WRITE (18) (12) C/D -TRANSMIT TxE (13) RD -LOGIC (9) - TXC (10) WR ç (11) CS TYPICAL A OUTPUT DELAY vs △ CAPACITANCE (dB) (22) DSR -+ 20 (24) MODEM (3) RECEIVE - RxD (17) CTS BUFFER (23) RTS -+10 △ OUTPUT DELAY (ns) (26) POWER + + 5V (4) GND 0 SPEC. (14) RERDY (25) RECEIVE -10 BrC (16) SYNDET 20 NOTE - 100 - 50 0 50 + 100 △ CAPACITANCE (pF) Applicable pinout numbers are included within parentheses.

#### $\label{eq:constraint} \textbf{DC ELECTRICAL CHARACTERISTICS} \quad \textbf{T}_{A} = 0^{\circ} \text{C to } +70^{\circ} \text{C}; \ \textbf{V}_{CC} = 5.0 \text{V} \pm 5 \text{W}; \ \textbf{GND} = 0 \text{V}.$

|                |                      |                                         | LIMITS |     |           |    |

|----------------|----------------------|-----------------------------------------|--------|-----|-----------|----|

|                | PARAMETER            | TEST CONDITIONS                         | Min    | Тур | Max       |    |

|                | Input voltage        |                                         |        |     |           | v  |

| VIH            | High                 |                                         | 2.0    |     | Vcc       |    |

| VIL            | Low                  |                                         | -0.5   |     | 0.8       |    |

| ·· <b>····</b> | Output voltage       |                                         |        |     |           | V  |

| Vон            | High                 | $I_{OH} = -100 \mu A$                   | 2.4    |     |           |    |

| Vol            | Low                  | $I_{OL} = 1.6 \text{mA}$                |        |     | 0.45      |    |

|                | Leakage              |                                         |        | 1   |           | μΑ |

| IDL            | Data bus             | $V_{OUT} = 0.45V$<br>$V_{OUT} = V_{CC}$ |        |     | -50<br>10 |    |

| hi.            | Input                | $V_{\rm IN} = V_{\rm CC}$               |        |     | 10        |    |

| lcc            | Power supply current |                                         |        | 45  | 80        | mA |

|                | Capacitance          | $T_A = 25^{\circ}C; V_{CC} = GND = 0V$  |        |     |           | pF |

| CIN            | Input                | $f_c = 1 MHz$                           |        |     | 10        |    |

| CI/O           | I/O                  | Unmeasured pins returned to GND         |        |     | 20        |    |

MP8251-I

MP8251

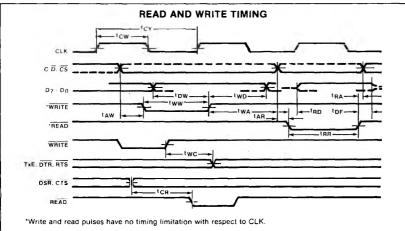

#### AC ELECTRICAL CHARACTERISTICS $T_A = 0^{\circ}$ C to $+70^{\circ}$ C; $V_{CC} = 5.0V \pm 5\%$ ; GND = 0V.

|                   | PARAMETER                                               | TEST CONDITIONS        | LIMITS   |          |           | UNIT       |

|-------------------|---------------------------------------------------------|------------------------|----------|----------|-----------|------------|

|                   |                                                         |                        | Min Typ  |          | Max       |            |

| BUS PA<br>Read Cy | RAMETERS <sup>1</sup><br>/cle                           |                        |          |          |           |            |

| tar               | Address stable before READ (CS, C/D)                    |                        | 50       |          |           | ns         |

| tRA               | Address hold time for READ (CS, C/D)                    |                        | 5        |          |           | ns         |

| tRR               | READ pulse width                                        |                        | 430      |          |           | ns         |

| tRD               | Data delay from READ                                    | CL = 100pF             |          |          | 350       | ns         |

| tDF               | READ to data floating                                   | C <sub>L</sub> = 100pF |          |          | 200       | ns         |

|                   |                                                         | $C_L = 15 pF$          | 25       |          | 1         | ns         |

| tRV               | Recovery time between WRITES2                           |                        | 6        |          |           | tcy        |

| Write Cy          | /cle                                                    |                        |          |          |           |            |

| taw               | Address stable before WRITE                             |                        | 20       |          |           | ns         |

| twA               | Address hold time for WRITE                             |                        | 20       |          |           | ns         |

| tww               | WRITE pulse width                                       |                        | 400      |          |           | ns         |

| tow               | Data set-up time for WRITE                              |                        | 200      |          | t         | ns         |

| twp               | Data hold time for WRITE                                | <u> </u>               | 40       |          |           | ns         |

| OTHER             | TIMINGS                                                 |                        |          |          |           |            |

| tcy               | Clock period <sup>3</sup>                               |                        | 0.420    |          | 1.35      | μs         |

| tφw               | Clock pulse width                                       |                        | 220      |          | 0.7tcy    | ns         |

| tR, tF            | Clock rise and fall time                                |                        | 0        |          | 50        | ns         |

| tDTx              | TxD delay from falling edge of TxC                      | C <sub>L</sub> = 100pF |          |          | 1         | μS         |

| tsex              | Rx data set-up time to sampling pulse                   | C <sub>L</sub> = 100pF | 2        |          | <u> </u>  | μs         |

| tHRx              | Rx data hold time to sampling pulse                     | C <sub>L</sub> = 100pF | 2        |          | <u> </u>  | μs         |

| f <sub>Tx</sub>   | Transmitter input clock frequency                       |                        |          |          | f         |            |

|                   | 1x baud rate                                            |                        | DC       |          | 56        | kHz        |

|                   | 16x and 64x baud rate                                   |                        | DC       |          | 520       | kHz        |

| trew              | Transmitter input clock pulse width<br>1x baud rate     |                        | 10       |          | Į         |            |

|                   | 16x and 64x baud rate                                   |                        | 12       |          |           | tcy<br>tcy |

| t <sub>TPD</sub>  | Transmitter input clock pulse delay                     |                        |          |          |           |            |

|                   | 1x baud rate                                            |                        | 15       |          |           | tcy        |

|                   | 16x and 64x baud rate                                   |                        | 3        |          |           | tcy        |

| f <sub>Rx</sub>   | Receiver input clock frequency                          |                        |          |          |           |            |

|                   | 1x baud rate<br>16x and 64x baud rate                   |                        | DC<br>DC |          | 56<br>520 | kHz<br>kHz |

| tRPW              | Receiver input clock pulse width                        |                        |          |          |           |            |

|                   | 1x baud rate                                            |                        | 12       | 1        |           | tcy        |

|                   | 16x and 64x baud rate                                   |                        | 1        |          |           | tcy        |

| <b>t</b> RPD      | Receiver input clock pulse delay                        |                        |          |          |           |            |

|                   | 1x baud rate<br>16x and 64x baud rate                   |                        | 15<br>3  |          |           |            |

| t <sub>Tx</sub>   | TxRDY delay from center of data bit                     | C <sub>L</sub> = 50pF  |          |          | 16        | tcy<br>tcy |

| t <sub>Rx</sub>   | RxRDY delay from center of data bit                     |                        |          | <b> </b> | 20        | tcy        |

| tis               | Internal SYNDET delay from center of data bit           |                        |          |          | 25        | tcy        |

| tes               | Internal SYNDET set-up time before falling edge of RxC  |                        |          |          | 16        | tcy        |

| tTxE              | TxEMPTY delay from center of data bit                   | C <sub>L</sub> = 50pF  |          |          | 16        |            |

| twc               | Control delay from rising edge of WRITE (TxE, DTR, RTS) |                        |          |          | 16        | tcy        |

|                   | Control to READ set up time (DSR, CTS)                  |                        |          | ō        | 16        | tcy<br>tcy |

NOTES

1. AC timings measured at  $V_{OH} = 2.0V$ ,  $V_{OL} = 0.8V$ , and with test load circuit. 2. This recovery time is for initialization only, when MODE, SYNC1, SYNC2, COMMAND

and first DATA BYTES are written into the USART. Subsequent writing of both

COMMAND and DATA are only allowed when TxRDY = 1.

3. The TxC and RxC frequencies have the following limitations with respect to CLK: for 1x baud rate, fTx or fRx  $\leq$  1/30 tcv)

for 16x and 64x baud rate,  $f_{Tx}$  or  $f_{Rx} \leq 1/4.5~t_{CY})$

MP8251-I

MP8251

#### TIMING WAVEFORMS

MP8251-I

MP8251

#### TIMING WAVEFORMS (Cont'd)

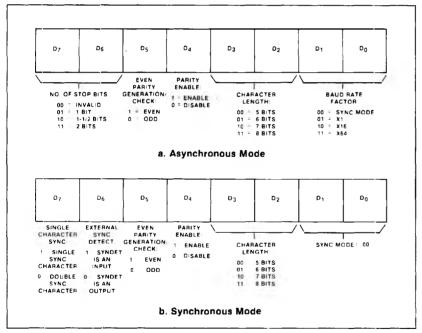

#### MODE INSTRUCTION CONTROL WORD FORMAT

#### COMMAND INSTRUCTION CONTROL WORD FORMAT

| D7                                              | D <sub>6</sub>                            | D5                                       | D4                                    | D3                                                     | D2                                        | D <sub>1</sub>                      | D <sub>D</sub>                |

|-------------------------------------------------|-------------------------------------------|------------------------------------------|---------------------------------------|--------------------------------------------------------|-------------------------------------------|-------------------------------------|-------------------------------|

| ENTER<br>HUNT<br>MODE<br>(EH)                   | INTERNAL<br>RESET<br>(IR):<br>1 - RETURNS | REQUEST<br>TO SEND<br>(RTS):<br>1 FORCES | ERROR<br>RESET<br>(ER):<br>1 = RESETS | SEND<br>BREAK<br>CHARACTER<br>(SBRK):                  | RECEIVE<br>ENABLE<br>(RxE):<br>1 - ENABLE | DATA<br>TERMINAL<br>READY<br>(DTR): | TRANSMIT<br>ENABLE<br>(TxEN): |

| 1 - ENABLES<br>SEARCH<br>FOR SYNC<br>CHARACTERS | MP 8251 TO<br>MODE<br>INSTRUCTION         | ATS OUTPUT                               | PE. GE<br>& FE<br>ERROR<br>FLAGS      | 1 FORCES<br>TXD OUTPUT<br>LOW<br>0 NORMAL<br>OPERATION | 0 = DISABLE                               | 1 FORCES<br>DTR OUTPUT<br>LOW       | 0 DISABLI                     |

#### STATUS READ WORD FORMAT

### MP8251 STATUS

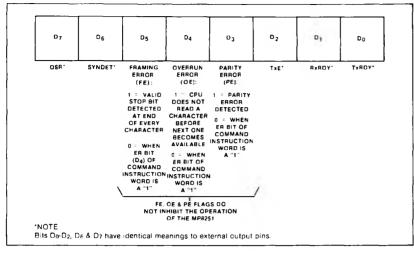

The MP8251 has provisions for allowing the programmer to read the status of the device at any time during the functional operation. When the  $C/\overline{D}$  input is a high-level, a normal read operation is executed to read this status information. The figure below shows the bits in the Status Read Word format. Since some of the status word bits have identical meaning to external output pins, the MP8251 can be used in a completely polled environment or in an interrupt driven environment.

MP8251

MP8251-I

#### TYPICAL DATA BLOCK TRANSFER