# **OPA628**

# Low Distortion Wideband OPERATIONAL AMPLIFIER

### **FEATURES**

- EXCELLENT DIFFERENTIAL GAIN: 0.015%

- EXCELLENT DIFFERENTIAL PHASE: 0.015°

- LOW DISTORTION: 90dB SFDR

- TWO-TONE THIRD-ORDER INTERCEPT: 60dBm

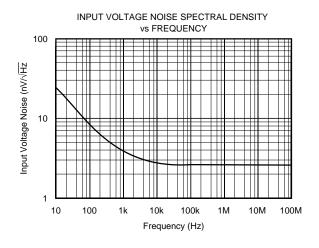

- LOW NOISE: 2.5nV/√Hz

- LOW NOISE FIGURE: 9dB

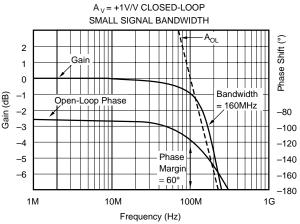

- BANDWIDTH (Gain = +1): 160MHz

- 0.1dB GAIN FLATNESS: 30MHz

- LOW OFFSET VOLTAGE: 500µV

### DESCRIPTION

The OPA628 is a low distortion, wideband operational amplifier. It features low differential gain error of 0.015% and low differential phase error of 0.015° at NTSC and PAL frequencies with a 150 $\Omega$  load (a back-terminated 75 $\Omega$  cable). The 0.1dB gain flatness to 30MHz, and the excellent differential gain and phase make the OPA628 ideal for broadcast quality video applications. In addition, the spurious free dynamic range of 90dB makes the OPA628 an excellent choice to buffer the input of precision Analog-to-Digital converters. It can also be used to provide a buffer for the output of precision high speed Digital-to-Analog converters. The two-tone third-order intercept of the OPA628 is 60dBm.

The OPA628 is a unity gain stable, voltage feedback operational amplifier. It has all of the benefits associated with voltage feedback amplifiers including high input impedance, high common mode rejection, and symmetrical differential input flexibility. The unity gain bandwidth of the OPA628 is 160MHz. The low noise of  $2.5 \text{nV}/\sqrt{\text{Hz}}$  and low noise figure of 9dB ( $R_{\text{S}} = 50\Omega$ ) make the OPA628 very useful in precision applications requiring wide dynamic range.

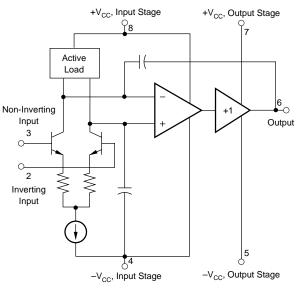

The superior distortion performance of the OPA628 is achieved by its multistage architecture which provides high open-loop gain. The distortion performance is

### **APPLICATIONS**

- BROADCAST QUALITY VIDEO

- MEDICAL IMAGING

- LOW NOISE PREAMPLIFIER

- PRECISION ADC/DAC BUFFER

- TELECOMMUNICATIONS

- ANALYTICAL INSTRUMENTS

- ACTIVE FILTERS

- DC RESTORATION CIRCUITS

additionally enhanced by separating the power supplies to the input and output stages requiring four power supply connections as shown in the block diagram below. This separation of supplies eliminates the effects of package and wire bond parasitic capacitance and inductance. The OPA628 is powered with  $\pm$ 5VDC supplies for low power dissipation. The OPA628 is available in 8-pin SOIC package. The temperature range is -40°C to +85°C.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©1993 Burr-Brown Corporation

## SPECIFICATIONS

### ELECTRICAL

At V\_{CC} =  $\pm 5$  VDC, R\_L=100\Omega, G = +2, and T\_A = +25°C, unless otherwise noted.

| PARAMETER                               | CONDITIONS                                                           | OPA628AU |         |           |          |

|-----------------------------------------|----------------------------------------------------------------------|----------|---------|-----------|----------|

|                                         |                                                                      | MIN      | ТҮР     | MAX       | UNITS    |

| INPUT NOISE                             |                                                                      |          |         |           |          |

| Voltage: $R_S = 0\Omega$                | $f_0 = 100Hz$                                                        |          | 8.3     |           | nV/√Hz   |

|                                         | $f_0 = 1 kHz$                                                        |          | 3.5     |           | nv/√Hz   |

|                                         | $f_0 = 10 \text{kHz}$                                                |          | 2.6     |           | nV/√Hz   |

|                                         | $f_0 = 100 \text{kHz}$                                               |          | 2.5     |           | nV/√Hz   |

|                                         | $f_0 = 1MHz$ to 100MHz                                               |          | 2.5     |           | nV/√Hz   |

|                                         | $f_B = 100$ Hz to 10MHz                                              |          | 8.1     |           | μVrms    |

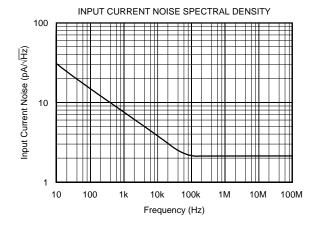

| Current                                 | $f_{\Omega} = 100$ kHz to 100MHz                                     |          | 2.2     |           | pA/√Hz   |

| Noise Figure                            | $R_{\rm S} = 50\Omega$ , $f_{\rm O} = 1$ MHz to 100MHz               |          | 9.3     |           | dB       |

| Noise Figure                            | $R_{\rm S} = 5022, R_{\rm O} = 110112 10 10010112$                   |          | 9.5     |           | uв       |

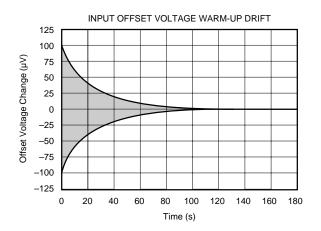

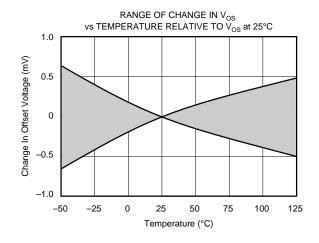

| OFFSET VOLTAGE                          |                                                                      |          |         |           |          |

| Input Offset Voltage                    | V <sub>CM</sub> = 0VDC                                               |          | ±0.5    | ±1        | mV       |

| Average Drift                           | $T_A = T_{MIN}$ to $T_{MAX}$                                         |          | ±6      |           | μV/°C    |

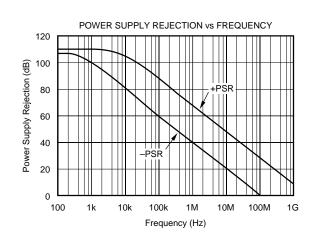

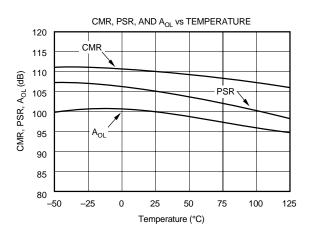

| Supply Rejection (PSRR)                 | $\pm V_{CC} = \pm 4.5V$ to $\pm 5.5V$                                | 90       | 105     |           | dB       |

| Over Specification Temperature          | $\pm V_{CC} = \pm 4.5V$ to $\pm 5.5V$ , $T_A = T_{MIN}$ to $T_{MAX}$ |          | 100     |           | dB       |

|                                         |                                                                      |          | 100     |           | 42       |

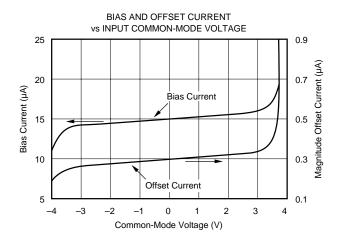

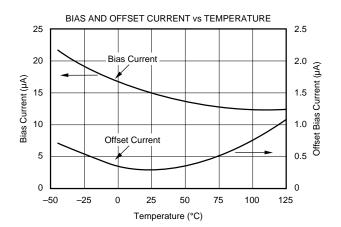

| INPUT BIAS CURRENT                      |                                                                      |          |         |           |          |

| Input Bias Current                      | V <sub>CM</sub> = 0VDC                                               |          | 15      | 30        | μA       |

| Over Specification Temperature          | $V_{CM} = 0VDC, T_A = T_{MIN}$ to $T_{MAX}$                          |          | 22      |           | μA       |

| Input Offset Current                    | $V_{CM} = 0VDC$                                                      |          | ±0.3    | <u>+2</u> | μΑ       |

| Over Specification Temperature          | $T_A = T_{MIN}$ to $T_{MAX}$                                         |          | ±0.8    |           | μA       |

|                                         |                                                                      |          |         |           |          |

| INPUT IMPEDANCE                         |                                                                      |          | 20 11 2 |           | kO II nE |

| Differential                            | Open–Loop                                                            |          | 30    2 |           | kΩ    pF |

| Common-Mode                             |                                                                      |          | 10    6 |           | MΩ    pF |

| INPUT VOLTAGE RANGE                     |                                                                      |          |         |           |          |

| Common-Mode Input Range                 |                                                                      |          | ±2.5    |           | V        |

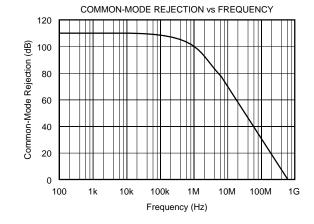

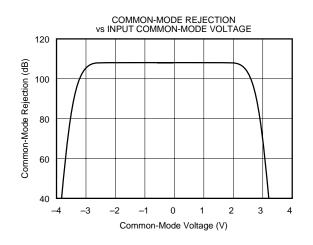

| Common-Mode Rejection (CMRR)            | $V_{CM} = \pm 2.5 V$                                                 | 90       | 110     |           | dB       |

| Over Specification Temperature          | $V_{CM} = \pm 2.5V$ , $T_A = T_{MIN}$ to $T_{MAX}$                   | 00       | 105     |           | dB       |

|                                         | $v_{CM} = \pm 2.5 v$ , $T_A = T_{MIN} to T_{MAX}$                    |          | 105     |           | ub .     |

| OPEN-LOOP GAIN, DC                      |                                                                      |          |         |           |          |

| Open-Loop Voltage Gain                  |                                                                      | 90       | 100     |           | dB       |

| Over Specification Temperature          | $T_A = T_{MIN}$ to $T_{MAX}$                                         |          | 96      |           | dB       |

| FREQUENCY RESPONSE                      |                                                                      |          |         |           |          |

|                                         | 0-1                                                                  |          | 100     |           |          |

| Closed-Loop Bandwidth                   | Gain = +1V/V                                                         |          | 160     |           | MHz      |

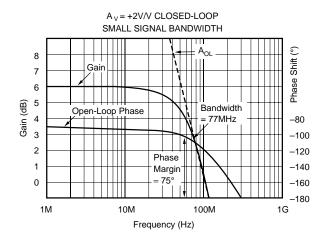

| (–3dB)                                  | Gain = +2V/V                                                         |          | 77      |           | MHz      |

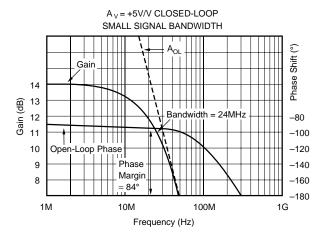

|                                         | Gain = +5V/V                                                         |          | 24      |           | MHz      |

| Bandwidth 0.1dB Flat                    | Gain = +2V/V                                                         |          | 30      |           | MHz      |

| Differential Gain                       | 3.58MHz, Gain = +2, V <sub>O</sub> = 1.4V Ramp                       |          | 0.015   |           | %        |

| Differential Phase                      | 3.58MHz, Gain = +2, $V_0$ = 1.4V Ramp                                |          | 0.015   |           | degrees  |

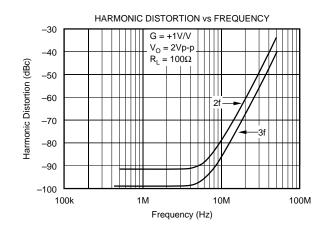

|                                         | $R_{L} = 100\Omega, G = +1V/V, f = 5MHz, V_{O} = 2Vp-p$              |          | 0.010   |           | augioco  |

|                                         | Second Harmonic                                                      |          | -91     |           | dBc      |

|                                         | Third Harmonic                                                       |          | -98     |           | dBc      |

|                                         |                                                                      |          | -90     |           | UDC      |

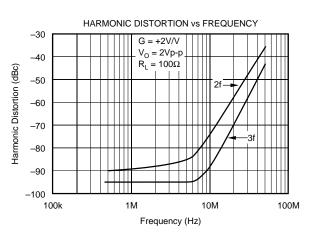

| r i i i i i i i i i i i i i i i i i i i | $R_L = 500\Omega$ , $G = +2V/V$ , $f = 5MHz$ , $V_O = 2Vp-p$         |          |         |           |          |

|                                         | Second Harmonic                                                      |          | -90     |           | dBc      |

|                                         | Third Harmonic                                                       |          | -97     |           | dBc      |

| R                                       | $L = 500\Omega$ , G = +2V/V, f = 10MHz, V <sub>O</sub> = 2Vp-p       |          |         |           |          |

|                                         | Second Harmonic                                                      |          | -83     |           | dBc      |

|                                         | Third Harmonic                                                       |          | -87     |           | dBc      |

| 3rd-Order Intercept                     | $f_{C} = 5MHz, G = +2$                                               |          | 70      |           | dBm      |

| 3rd-Order Intercept                     | $f_{\rm C} = 10$ MHz, G = +2                                         |          | 60      |           | dBm      |

| Two-tone 3rd-Order Intercept            | $f_{\rm C} = 5 \text{MHz}, G = +2$                                   |          | 60      |           | dBm      |

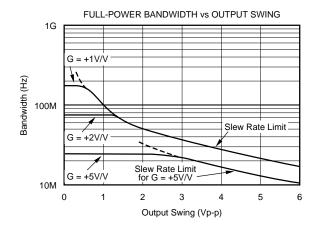

| Full Power Response <sup>(1)</sup>      | $V_{\rm C} = 5Vp-p$ , Gain = +1V/V                                   |          | 20      |           | MHz      |

| i an i ower ivesponse                   |                                                                      |          |         |           |          |

| Claur Data                              | $V_0 = 2Vp-p$ , Gain = +1V/V                                         |          | 49      |           | MHz      |

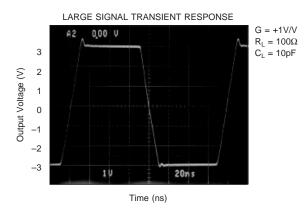

| Slew Rate                               | 2V Step, Gain = $-1V/V$                                              |          | 310     |           | V/µs     |

| Overshoot                               | 2V Step, Gain = -1V/V                                                |          | 2       |           | %        |

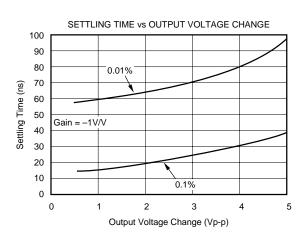

| Settling Time: 0.10%                    | 2V Step, Gain = -1V/V                                                |          | 20      |           | ns       |

| 0.01%                                   |                                                                      |          | 64      |           | ns       |

| Overload Recovery Time <sup>(2)</sup>   |                                                                      |          | 60      |           | ns       |

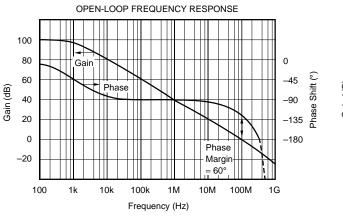

| Phase Margin                            | Gain = +1V/V                                                         |          | 60      |           | degrees  |

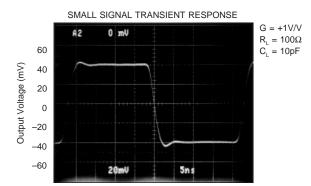

| Rise Time                               | Gain = +1V/V, 10% to 90%                                             |          |         |           | Ĭ        |

| Small Signal                            | $V_{\rm O} = 100 \mathrm{mVp-p}$                                     |          | 3       |           | ns       |

| Large Signal                            | $V_0 = 6Vp-p$                                                        |          | 15      |           | ns       |

|                                         |                                                                      |          |         |           | -        |

| RATED OUTPUT                            |                                                                      |          |         |           |          |

| Voltage Output                          | $f_0 = 1MHz, R_L = 100\Omega$                                        | ±3       |         |           | V        |

| Over Specification Temperature          | $f_0 = 1$ MHz, $R_L = 100\Omega$ , $T_A = T_{MIN}$ to $T_{MAX}$      |          | ±3      |           | V        |

|                                         | $f_0 = 1$ MHz, $R_L = 50\Omega$                                      |          | ±3      |           | V        |

| Output Resistance                       | 1MHz, Gain = +1V/V                                                   |          | 0.0005  |           | Ω        |

| Load Capacitance Stability              | $Gain = +1V/V, V_0 = 2Vp-p$                                          |          | 20      |           | pF       |

| Short Circuit Current                   | Continuous, Source                                                   |          | +180    |           | mA       |

|                                         |                                                                      |          |         |           |          |

| Short Circuit Current                   | Continuous, Sink                                                     |          | -130    |           | mA       |

## SPECIFICATIONS (CONT)

### ELECTRICAL

At V<sub>CC</sub> =  $\pm$ 5VDC, R<sub>L</sub>=100 $\Omega$ , G = +2, and T<sub>A</sub> = +25°C, unless otherwise noted.

| PARAMETER           | CONDITIONS                                       | OPA628AU |     |      |       |

|---------------------|--------------------------------------------------|----------|-----|------|-------|

|                     |                                                  | MIN      | ТҮР | МАХ  | UNITS |

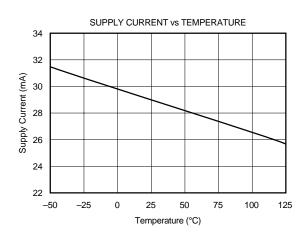

| POWER SUPPLY        |                                                  |          |     |      |       |

| Rated Voltage       | ±V <sub>CC</sub>                                 |          | ±5  |      | VDC   |

| Derated Performance | ±V <sub>CC</sub>                                 | ±4.5     |     | ±6   | VDC   |

| Current, Quiescent  | $I_{O} = 0$ mADC                                 |          | 29  | 32   | mA    |

| Current, Quiescent  | $I_{O} = 0$ mADC, $T_{A} = T_{MIN}$ to $T_{MAX}$ |          | 31  | 35   | mA    |

| TEMPERATURE RANGE   |                                                  |          |     |      |       |

| Specification: AU   | T <sub>MIN</sub> and T <sub>MAX</sub>            | -40      |     | +85  | °C    |

| Storage: AU         | Ambient Temperature                              | -55      |     | +125 | °C    |

| θ <sub>JA</sub> AU  | Junction-to-Ambient                              |          | 100 |      | °C/W  |

NOTES: (1) Full power response = slew rate/( $2\pi$ Vpeak). (2) Time for output to resume linear operation after saturation.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT  | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|----------|--------------------|------------------------------------------|

| OPA628AU | SO-8 Surface Mount | 182                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

### ABSOLUTE MAXIMUM RATINGS

| Supply                                    | ±7VDC                        |

|-------------------------------------------|------------------------------|

| Internal Power Dissipation <sup>(1)</sup> | See Applications Information |

| Differential Input Voltage                |                              |

| Input Voltage Range                       | See Applications Information |

| Storage Temperature Range: AP, AU         | –55°C to +125°C              |

| Lead Temperature (soldering, SOIC 3s)     |                              |

| Output Short Circuit to Ground (+25°C)    | Continuous to Ground         |

| Junction Temperature (T <sub>J</sub> )    | +175°C                       |

NOTE: (1) Packages must be derated based on specified  $\theta_{\rm JA}$  . Maximum  $\rm T_J$  must be observed.

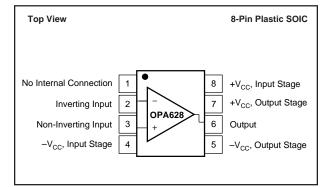

### **PIN CONFIGURATION**

### ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

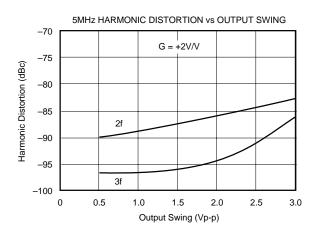

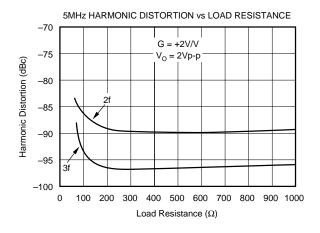

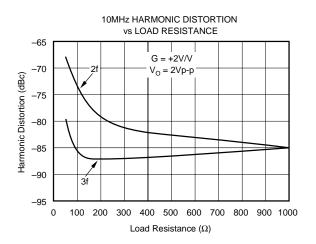

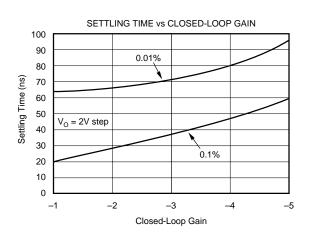

## **TYPICAL PERFORMANCE CURVES**

At  $V_{CC}$  = ±5VDC, R<sub>L</sub>=100 $\Omega$ , G = +2, and T<sub>A</sub> = +25°C, unless otherwise noted.

At  $V_{CC}$  = ±5VDC, R<sub>L</sub>=100 $\Omega$ , G = +2, and T<sub>A</sub> = +25°C, unless otherwise noted.

At  $V_{CC}$  =  $\pm 5 VDC,~R_L$  =100 $\Omega,~G$  = +2, and  $T_A$  = +25°C, unless otherwise noted.

At  $V_{CC}$  = ±5VDC, R<sub>L</sub>=100 $\Omega$ , G = +2, and T<sub>A</sub> = +25°C, unless otherwise noted.

At V<sub>CC</sub> =  $\pm$ 5VDC, R<sub>L</sub>=100 $\Omega$ , G = +2, and T<sub>A</sub> = +25°C, unless otherwise noted.

# DISCUSSION OF PERFORMANCE

The OPA628's classical operational amplifier architecture employs true differential and fully symmetrical inputs allowing optimal performance in either inverting or noninverting circuit applications. All traditional circuit configurations and op amp theory apply to the OPA628. The use of low drift thin film resistors allows internal operating currents to be laser trimmed at wafer level to optimize AC performance such as distortion, bandwidth and settling time, as well as DC parameters such as input offset voltage. The result is a wideband, high frequency monolithic operational amplifier with a gain-bandwidth product of 150MHz, a spurious free dynamic range (SFDR) of 90dB, and input offset voltage of  $500\mu$ V.

The layout considerations described in the "Printed Circuit Board Guidelines" section must be followed to achieve the best possible performance of the OPA628.

#### DIFFERENTIAL GAIN AND PHASE

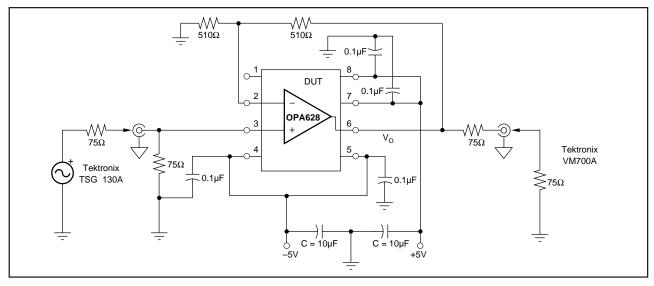

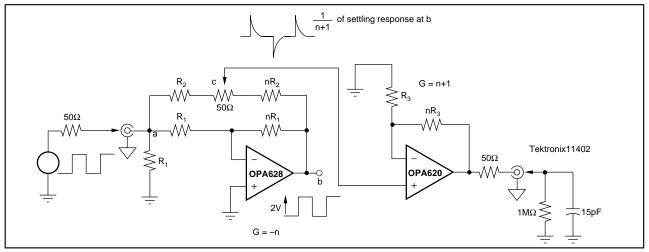

Differential Gain (DG) and Differential Phase (DP) are among the more important specifications for video applications. DG is defined as the percent change in closed-loop gain over a specified change in output voltage level. DP is defined as the change in degrees of the closed-loop phase over the same output voltage change. Both DG and DP are specified at the NTSC sub-carrier frequency of 3.58MHz and the PAL subcarrier of 4.43MHz. All NTSC measurements were performed using a Tektronix model VM700A Video Measurement Set. All PAL measurements were performed using a Rohde & Schwarz Video Analyzer UAF.

DG and DP of the OPA628 were measured with the amplifier in a gain of +2V/V with 75 $\Omega$  input impedance and the output back-terminated in 75 $\Omega$ . The input signal selected

from the generator was a 0V to 1.4V modulated ramp with sync pulse. With these conditions the test circuit shown in Figure 1 delivered a 100IRE modulated ramp to the 75 $\Omega$ input of the video analyzer. The signal averaging feature of the analyzer was used to establish a reference against which the performance of the amplifier was measured. Signal averaging was also used to measure the DG and DP of the test signal in order to eliminate the generator's contribution to measured amplifier performance. Typical performance of the OPA628 is 0.015% differential gain and 0.015° differential phase to both NTSC and PAL standards. Increasing the closed-loop gain degrades the DP and DG.

#### **GAIN FLATNESS**

Small signal  $\pm 0.1$ dB gain flatness can be achieved up to 30MHz in a non-inverting gain of  $\pm 2$ V/V through careful layout of the printed circuit board and frequency shaping of the feedback network. Frequency shaping is achieved empirically by placing a small capacitor in parallel with either the feedback resistor or the input resistor of the OPA628 to compensate for printed circuit parasitic capacitance. A capacitor in the range of approximately 1pF to 20pF is suggested. Printed circuit board layout design will determine if the capacitor should be placed across the feedback resistor or the input resistor.

Small signal  $\pm 0.1$ dB gain flatness of greater than 30MHz can be achieved at a gain of  $\pm 1$ V/V. To eliminate the effects of package lead inductance, a small value resistor should be included in the feedback path. Maximizing gain flatness for a particular layout requires optimization of the feedback resistor; an approximate value is 50 $\Omega$  to 75 $\Omega$ .

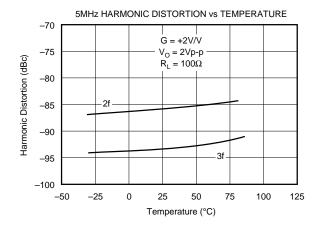

#### DISTORTION

The OPA628's Harmonic Distortion characteristics when driving a  $100\Omega$  load are shown vs frequency and vs voltage output in the Typical Performance Curves. Distortion can be further optimized by decreasing output loading as also

FIGURE 1. Configuration For Testing Differential Gain/Phase.

shown in Typical Performance Curves. Include the contribution of the feedback resistance when calculating the effective load resistance at the amplifier output. A high performance spectrum analyzer such as the HP3585B should be used to measure distortion.

Two-tone, third-order intermodulation distortion (IM) is an important parameter for many RF amplifier applications. The specification table shows the OPA628's two-tone, third order IM intercept at 5MHz and 10MHz. For these measurements, tones were spaced 200kHz apart. This data is particularly useful for determining the magnitude of the third-order IM products. The magnitude of the third-order IM products can be easily calculated from the expression:

Third IM =  $2(OPI^{3}P - P_{O})$ where  $OPI^{3}P$  = third-order output intercept, dBm  $P_{O}$  = output level/tone, dBm/tone Third IM = third-order intermodulation ratio below each output tone, dB

As an example, with  $OPI^{3}P = 60dBm$ , for  $P_{O} = 10dBm$ , the third order IM = 2(60 - 10) = 100dB below either 10dBm tone. The OPA628's low IM makes the device an excellent choice for a variety of RF signal processing applications. In order to obtain the full low distortion performance of the OPA628, it is imperative to follow the recommendations described in the "Printed Circuit Board Guidelines" section.

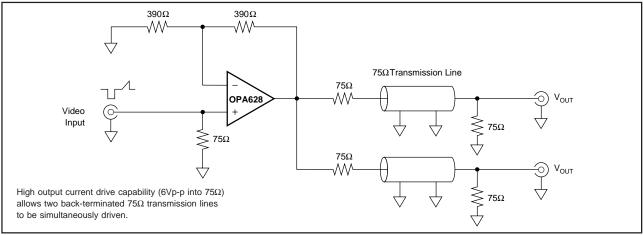

#### **OUTPUT DRIVE CAPABILITY**

The OPA628 has been optimized for low distortion performance with back terminated  $50\Omega$  and  $75\Omega$  loads ( $R_{LOAD} = 100\Omega$  and  $150\Omega$ , respectively). However, it is capable of driving 6Vpp into a  $50\Omega$  load with a sacrifice in distortion. This high-output drive capability makes the OPA628 an ideal choice for a wide range of RF, IF, and video applications. All transmission lines should be terminated with the characteristic impedance of the transmission line.

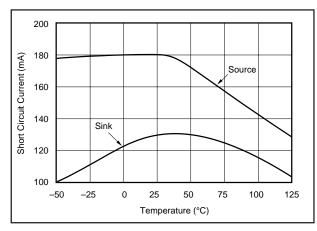

Internal current-limiting circuitry limits output current to about 130mA at 25°C. This prevents damage from acciden-

tal shorts to common and eliminates the need for external current-limiting circuitry. Although the device can withstand momentary shorts to either power supply, it is not recommended.

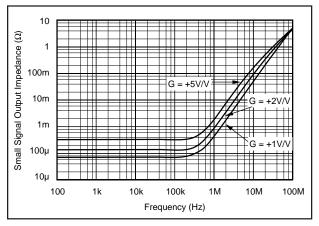

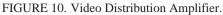

Many demanding high-speed applications such as ADC/ DAC buffers require op amps with low wideband output impedance. For example, low output impedance is essential when driving the signal-dependent capacitances at the inputs of flash A/D converters. As shown in Figure 2, the OPA628 maintains very low closed-loop output impedance over frequency. Closed-loop output impedance increases with frequency since loop gain is decreasing with frequency.

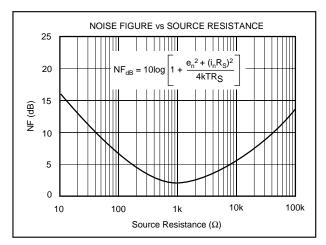

#### **NOISE FIGURE**

The OPA628's voltage and current noise spectral densities are specified in the Typical Performance Curves. For RF applications, however, Noise Figure (NF) is often the preferred noise specification since it allows system noise performance to be more easily calculated. The OPA628's Noise Figure vs Source Resistance is shown in Figure 3 for frequencies above 1MHz.

FIGURE 2. Small Signal Output Impedance vs Frequency.

FIGURE 3. Noise Figure vs Source Resistance.

#### SETTLING TIME

Settling time is defined as the total time required, from the input signal step, for the output to settle to within the specified error band around the final value. This error band is expressed as a percentage of the value of the output transition, a 2V step. Thus, settling time to 0.01% requires an error band of  $\pm 200\mu$ V centered around the final value of 2V.

Settling time, specified in an inverting gain of one, is only 64ns to 0.01% for a 2V step. Settling time increases with closed-loop gain and output voltage change as described in the Typical Performance Curves. Preserving settling time requires critical attention to the details as mentioned under "Printed Circuit Board Guidelines." The amplifier also recovers quickly from input overloads. Overload recovery time to linear operation from a 50% overload is typically only 60ns. Settling time measurements for the OPA628 were performed in the circuit configuration of Figure 5. A sampling oscilloscope was used with signal averaging.

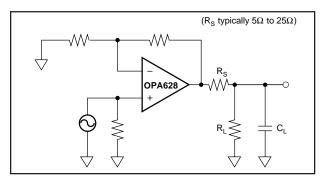

#### CAPACITIVE LOADS

Capacitive loads will decrease the OPA628's phase margin which may cause high frequency peaking or oscillations. Capacitive loads greater than 20pF should be buffered by connecting a small resistance, usually  $5\Omega$  to  $25\Omega$ , in series with the output as shown in Figure 4. This is particularly important when driving high capacitance loads such as flash A/D converters.

FIGURE 4. Driving Capacitive Loads.

In general, capacitive loads should be minimized for optimum high frequency performance. Coax lines can be driven if the cable is properly terminated. The capacitance of coax cable (29pF/ft for RG-58) will not load the amplifier when the coaxial cable or transmission line is terminated in its characteristic impedance.

#### COMPENSATION

The OPA628 is internally compensated and is stable in unity gain with a phase margin of approximately  $60^{\circ}$ . However, the unity gain buffer is the most demanding circuit configuration for loop stability and oscillations are most likely to occur in this gain. If possible, use the device in a noise gain of two or greater to improve phase margin and reduce the susceptibility to oscillation. (Note that, from a stability standpoint, an inverting gain of -1V/V is equivalent to a noise gain of 2V/V.) Gain and phase response for other gains are shown in the Typical Performance Curves.

The high-frequency response of the OPA628 in a good layout is very flat with frequency. However, some circuit configurations, such as those where large feedback resistances are used, can produce high-frequency gain peaking. This peaking can be minimized by connecting a small capacitor in parallel with the feedback resistor. This capacitor compensates for the closed-loop, high frequency, transfer function zero that results from the time constant formed by the input capacitance of the amplifier (typically 2pF after PC board mounting), and the input and feedback resistors. The selected compensation capacitor may be a trimmer, a fixed capacitor, or a planned PC board capacitance. The capacitance value is strongly dependent on circuit layout and closed-loop gain. Using small resistor values will preserve the phase margin and avoid peaking by keeping the break frequency of this zero sufficiently high. When high closedloop gains are required, a three-resistor attenuator (tee network) is recommended to avoid using large value resistors with large time constants.

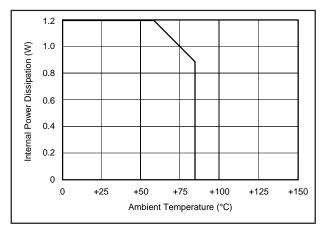

#### THERMAL CONSIDERATIONS

The OPA628 does not require a heat sink for operation in most environments. The use of a heat sink, however, will reduce the internal thermal rise and will result in cooler, more reliable operation. At extreme temperatures and under full load conditions a heat sink is necessary. See "Maximum Power Dissipation" curve, Figure 6.

The internal power dissipation is given by the equation  $P_D = P_{DQ} + P_{DL}$ , where  $P_{DQ}$  is the quiescent power dissipation and  $P_{DL}$  is the power dissipation in the output stage due to the load. (For  $\pm V_{CC} = \pm 5V$ ,  $P_{DQ} = 10V \times 32mA = 320mW$ , max). For the case where the amplifier is driving a grounded load ( $R_L$ ) with a DC voltage ( $V_{OUT}$ ) the maximum valueof  $P_{DL}$  occurs at  $V_{OUT} = V_{CC}/2$ , and is equal to  $P_{DL}$ , max = ( $V_{CC}$ )<sup>2</sup>/4 $R_L$ . Note that it is the voltage across the output transistor, and not the load, that determines the power dissipated in the output stage.

When the output is shorted to common  $P_{DL} = 5V \times 180 \text{mA}$ = 900mW. Thus,  $P_D$ , max = 320mW + 900mW  $\approx 1.2$ W.

FIGURE 5. Settling Time Test Circuit.

Note that the short circuit condition represents the maximum amount of internal power dissipation that can be generated. Thus, the "Maximum Power Dissipation" curve starts at 1.2W and is derated based on a 175°C maximum junction temperature and the junction-to-ambient thermal resistance,  $\theta_{JA}$ , of the package. The variation of short circuit current with temperature is shown in Figure 7.

FIGURE 6. Maximum Power Dissipation.

FIGURE 7. Short Circuit Current vs Temperature.

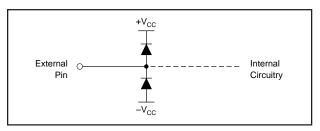

#### INPUT PROTECTION

Static damage has been well recognized for MOSFET devices, but any semiconductor device deserves protection from this potentially damaging source. The OPA628 incorporates on-chip ESD protection diodes as shown in Figure 8. This eliminates the need for the user to add external protection diodes, which can add capacitance and degrade AC performance.

FIGURE 8. Internal ESD Protection.

All pins on the OPA628 are internally protected from ESD by means of a pair of back-to-back reverse-biased diodes to either power supply as shown. These diodes will begin to conduct when the input voltage exceeds either power supply by about 0.7V. This situation can occur with loss of the amplifier's power supplies while a signal source is still present. The diodes can typically withstand a continuous current of 30mA without destruction. To insure long term reliability, however, diode current should be externally limited to approximately 10mA whenever possible.

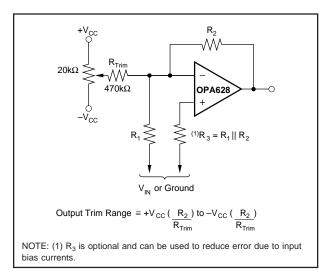

#### **OFFSET VOLTAGE ADJUSTMENT**

The OPA628's input offset voltage is laser-trimmed and will require no further adjustment for most applications. However, if additional adjustment is needed, the circuit in Figure 9 can be used without degrading offset drift with temperature. Avoid external adjustment whenever possible since extraneous noise, such as power supply noise, can be inadvertently coupled into the amplifier's inverting input terminal. Remember that additional offset errors can be created by

the amplifier's input bias currents. Whenever possible, match the impedance seen by both inputs as is shown with  $R_3$ . This will reduce error due to the amplifier's input bias current.

FIGURE 9. Offset Voltage Trim.

#### SPICE MODELS

Computer simulation using SPICE is often useful when analyzing the performance of analog circuits and systems. This is particularly true for Video and RF amplifier circuits where parasitic capacitance and inductance can have a major effect on circuit performance. SPICE models are available for the OPA628. Contact Burr-Brown Applications Department to receive a SPICE diskette.

#### **RELIABILITY DATA**

Reliability reports are available upon request for each of the package options offered.

#### PRINTED CIRCUIT BOARD GUIDELINES

The printed circuit board layout is critical to obtaining the full performance of the OPA628, particularly optimum distortion and gain flatness. The guidelines below should be employed to design the OPA628 printed circuit board.

1. Establish the primary ground plane on the IC side of the PC board. The primary ground plane is the lowest impedance ground plane, it should be as wide as possible with minimal interruptions. Connect all unused space on both sides of the board to the ground plane. The ground plane should extend beneath the body of the IC on **both** sides of the board. A 2-ounce copper ground plane is recommended. The input signal ground return, the load return, and the power supply common should all be connected to the same physical point to avoid ground loops which can cause unwanted feedback.

- 2. The entire physical circuit should be as small as practical. All signal and power supply paths should be as short and direct as possible to minimize stray capacitance and inductance which are detrimental to high frequency performance. Minimize signal trace impedance by keeping traces as wide and short as possible. Stray capacitance should be minimized, especially at high impedance nodes such as the amplifier's input terminals. In addition, stray signal coupling from the output of the amplifier back to the input should be minimized.

- 3. In general, the use of surface mount components improves performance over through-hole components by minimizing parasitics. (However, it should be noted that use of the DIP version of the OPA628 will not compromise amplifier performance.) If circuit elements with leads are used, the leads should be kept as short as possible (6mm) to minimize lead inductance. Resistors used in feedback networks should have values of a few hundred ohms for best performance. Shunt capacitance problems limit the acceptable resistance range to about  $1,000\Omega$  on the high end and to a value that is within the amplifier's output drive limits on the low end. Remember that output current must be provided by the amplifier to drive its own feedback network as well as to drive its load.

- 4. As with any low distortion, wide bandwidth amplifier, power supply bypassing is extremely critical and must always be used. The system power supplies should be well bypassed at the board level with a minimum of 2.2µF tantalum capacitors. In addition, all four power supply leads should be locally bypassed to ground as close as possible to the amplifier pins. Surface mount 0.1µF capacitors will provide the best performance for local bypassing. Johanson 0.1µF capacitors (part number 250R18B104ZP4W) are used on the OPA628 demonstration board. All power supply bypass capacitors should be low impedance designs and should be located on the primary ground plane side of the PC board for the lowest impedance connection to ground. Properly bypassed and modulation free power supply lines allow optimum amplifier performance.

- 5. The OPA628 should be soldered directly into the PC board for best performance.

### **APPLICATIONS**

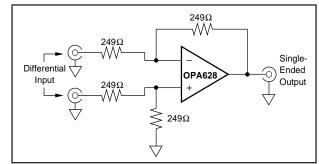

FIGURE 11. Differential Input Buffer Amplifier (G = 2V/V).

FIGURE 12. Low Distortion Unity Gain Difference Amplifier.

**OPA628**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated