National Semiconductor

### PRELIMINARY March 1996

# PC87415 PCI-IDE DMA Master Mode Interface Controller

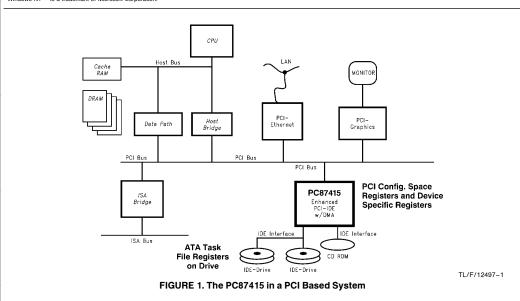

## **1.0 General Description**

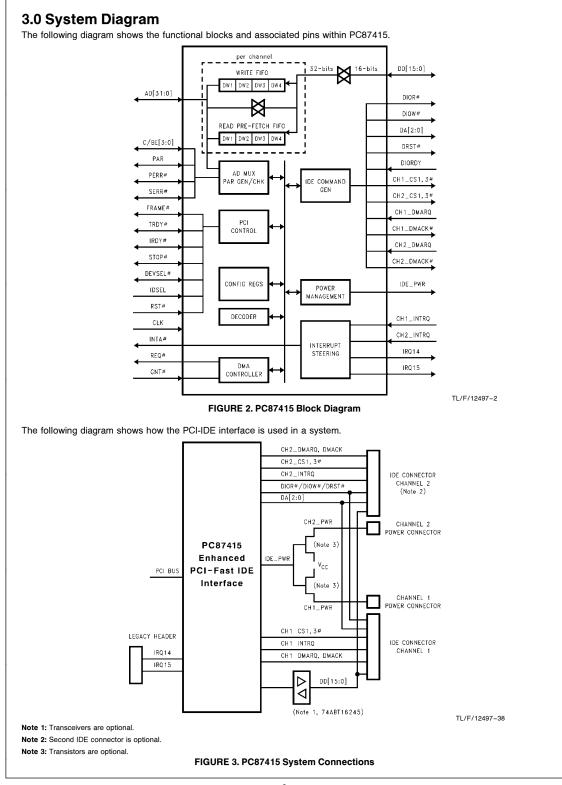

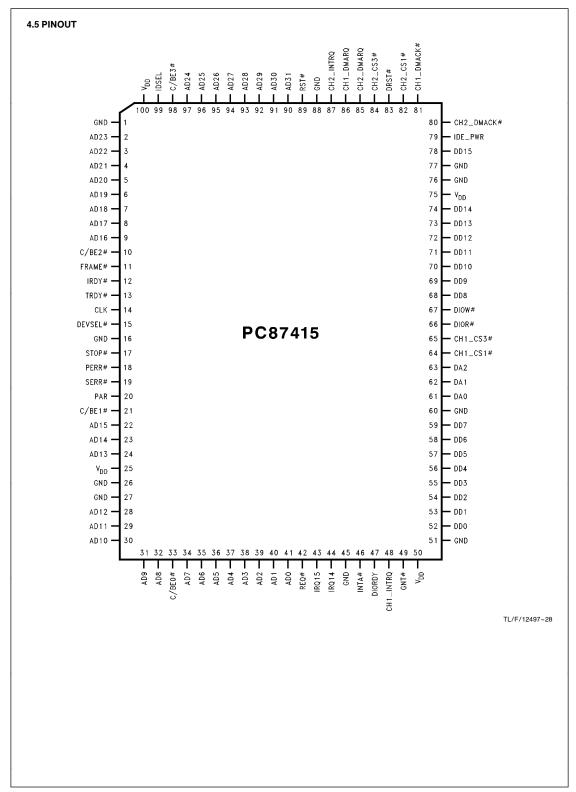

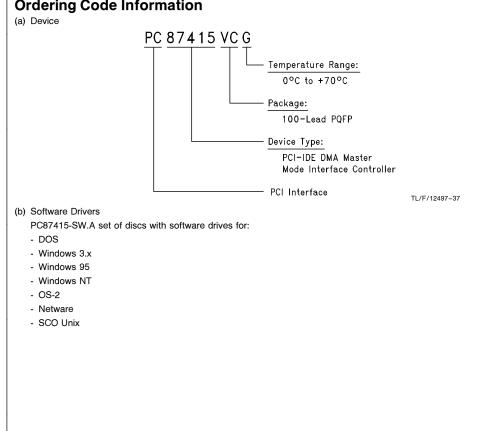

The Enhanced PCI-IDE Interface is a single-chip controller packaged in a 100-pin PQFP. It provides 2 IDE channels for interfacing up to 4 IDE drives, or 2 IDE drives and CD-ROM directly on the PCI Local bus. An enhanced DMA controller on-chip increases system performance by providing full scatter/gather data transfers between IDE devices and svstem memory without CPU intervention. Four levels of both write posting and read prefetching per channel allow the host CPU to run concurrently with IDE cycles. Programmable timing functions provide maximum flexibility of timing parameters per drive for optimizing the data transfer rate per drive. Both PC compatible addressing and PCI compliant addressing are supported by re-mapping the base addresses. A power control feature allows turning off power to the IDE cables.

The Enhanced PCI-IDE Interface connection to the PCI bus is virtually "glue-less", with only one additional TTL data buffer (optional). This high-integration solution reduces component count, eases board design, reduces cost and increases reliability

The Enhanced PCI-IDE supports faster ATA devices using PIO modes 1, 2, 3, and 4 as well as DMA modes 0, 1, and 2. It comes with a full suite of software drivers for DOS 5.0-6.x, Windows® 3.x, Windows® 95, Windows NT™, OS/2 2.x, Novell® NetWare™ 3.1x-4.x, and SCO UNIX® 3.x.

TRI-STATE® is a registered trademark of National Semiconductor Corpo NATCHDOG™ is a registered trademark of National Semiconductor Corporation Novell® is a registered trademark of Novell nc.

NetWare™ is a trademark of Novell, Inc.

Unix<sup>®</sup> is a registered trademark of AT&T Bell Laboratories. Windows<sup>®</sup> and Windows<sup>®</sup> 95 are registered trademarks of Microsoft Corporation. Windows NT™ is a trademark of Microsoft Corporation.

- 2.0 Features

- PCI bus interface for up to 4 IDE devices

- 33 MHz, 32-bit PCI bus data path with full parity error reporting

- 16.7 MByte/sec maximum IDE transfer rate

- Support for 2 IDE channels (@ 2 IDE devices per channel)

- Primary or secondary IDE addressing (1F0x/170x) in PC compatible mode

- Re-mappable base registers for full PCI compliance

- Concurrent channel operation (PIO & DMA modes)

- 4 Double Word write FIFO per channel

- 4 Double Word read prefetch FIFO per channel

- Enhanced DMA mode with scatter/gather capability

- ANSI ATA Modes 0 through 4 PIO support (internal DMA not selected)

- IORDY handshaking for PIO

- ANSI ATA Modes 0 through 2 Multiword DMA support (internal DMA selected)

- Individually programmable command and recovery timing for reads and writes per channel/drive for command, control and data

- Individually programmable data sector size for read prefetches per channel

- PC compatible interrupt routing of IRQ14 and IRQ15

- Hardware and software chip enable/disable

- Optional Power Control for IDE Drives

- Fully static logic design

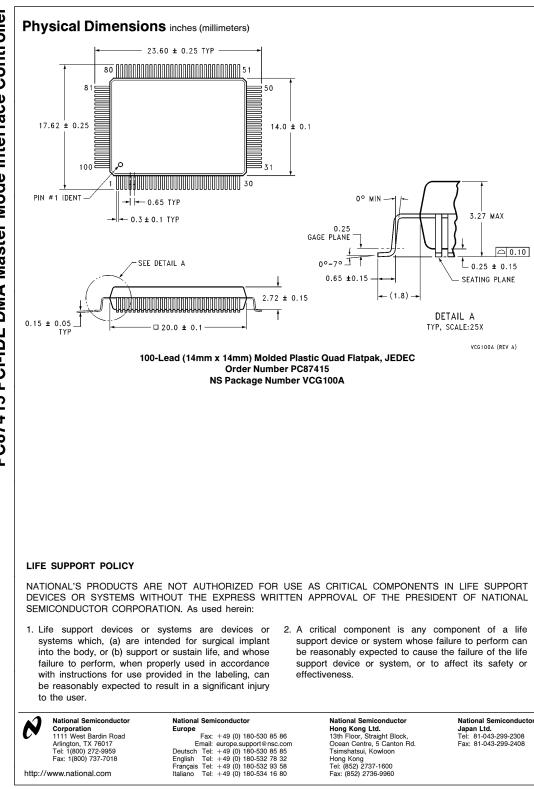

- 100-pin PQFP package

© 1996 National Semiconductor Corporation TL/F/12497 RRD-B30M46/Printed in U. S. A

# **Table of Contents** 1.0 GENERAL DESCRIPTION 2.0 FEATURES 3.0 SYSTEM DIAGRAM 4.0 PIN DESCRIPTION 4.1 PCI Interface 4.2 IDE Interface 4.3 Power Control 4.4 Power and Ground 4.5 Pinout 5.0 CONFIGURATION REGISTERS 6.0 BUS MASTER IDE CONTROL AND STATUS REGISTERS 7.0 FUNCTIONAL DESCRIPTION 7.1 PCI Interface 7.1.1 Commands 7.1.2 Termination 7.1.2.1 Target Abort in Target Mode 7.1.2.2 Retry in Target Mode 7.1.2.3 Target Abort in Master Mode 7.1.2.4 Retry in Master Mode 7.1.2.5 Disconnect in Master Mode 7.1.2.6 Master Abort in Master Mode 7.2 Data Buffers 7.2.1 Write Posting 7.2.2 Prefetch 7.2.3 Two Channel Buffer Protocol 7.3 IDE Interface 7.3.1 IDE Protocol 7.3.1.1 PIO Single Sector Reads 7.3.1.2 PIO Block Mode Reads 7.3.1.3 PIO Single Sector Writes 7.3.1.4 PIO Block Mode Writes 7.3.1.5 DMA Mode 7.3.2 Independent Timing per Drive 7.3.3 Flow Control 7.3.3.1 PIO 7.3.3.1.1 IORDY 7.3.3.1.2 Pseudo DMA 7.3.3.2 DMA 7.3.4 Interrupt Routing 7.3.5 Prefetching 7.3.6 Legacy/Native Mapping Scheme

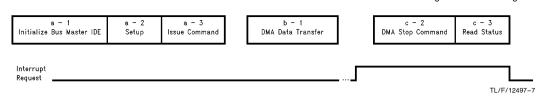

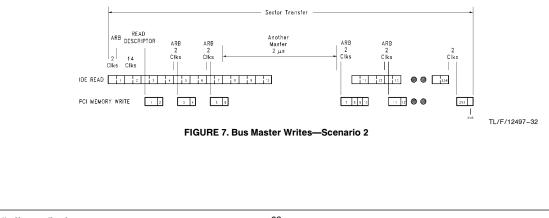

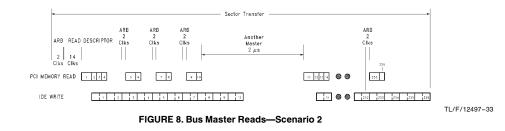

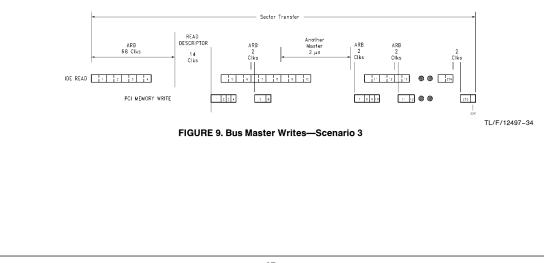

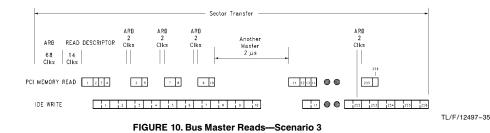

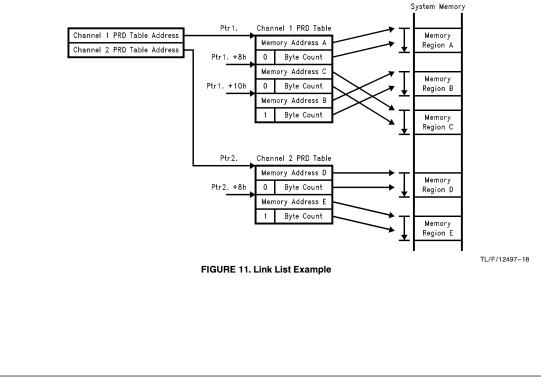

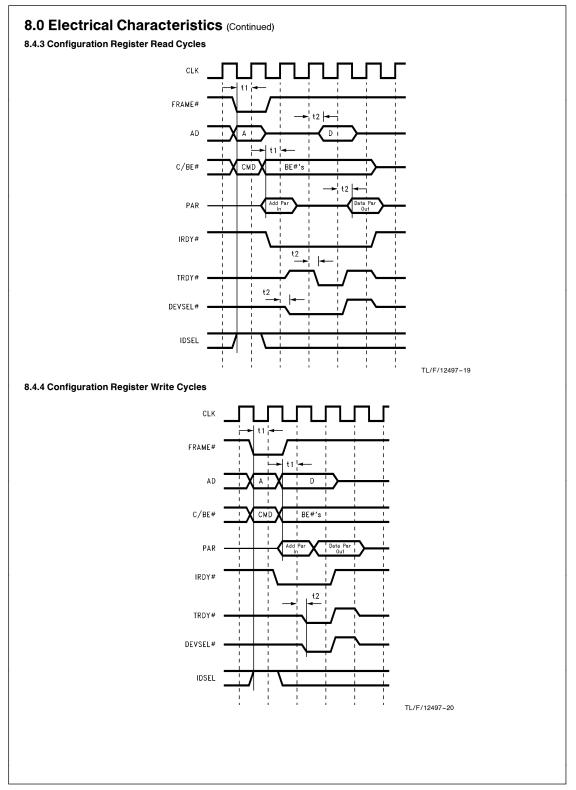

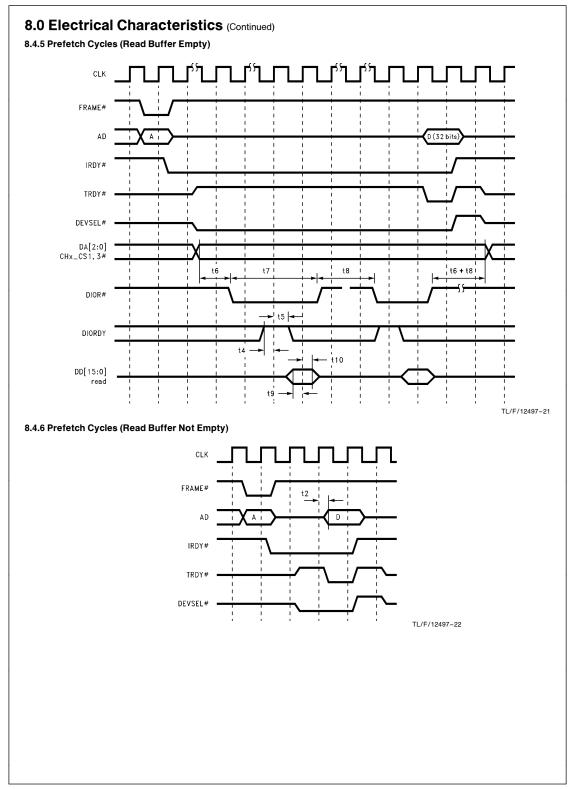

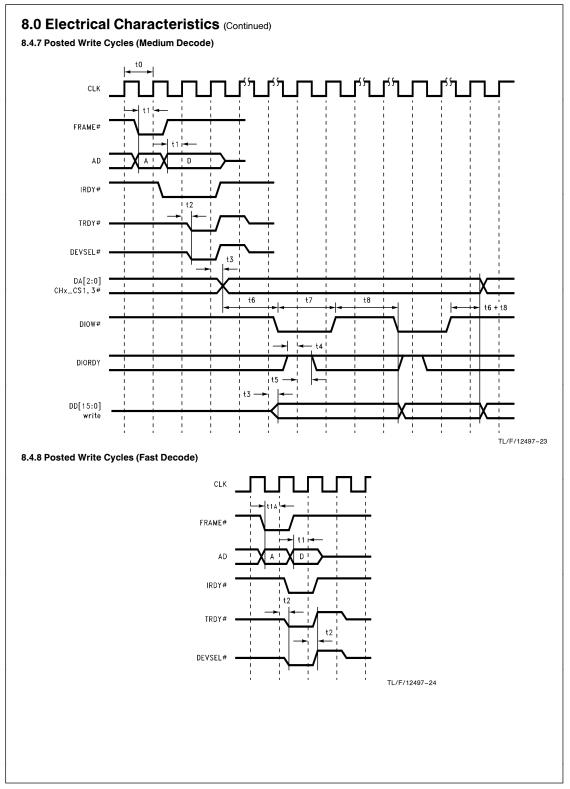

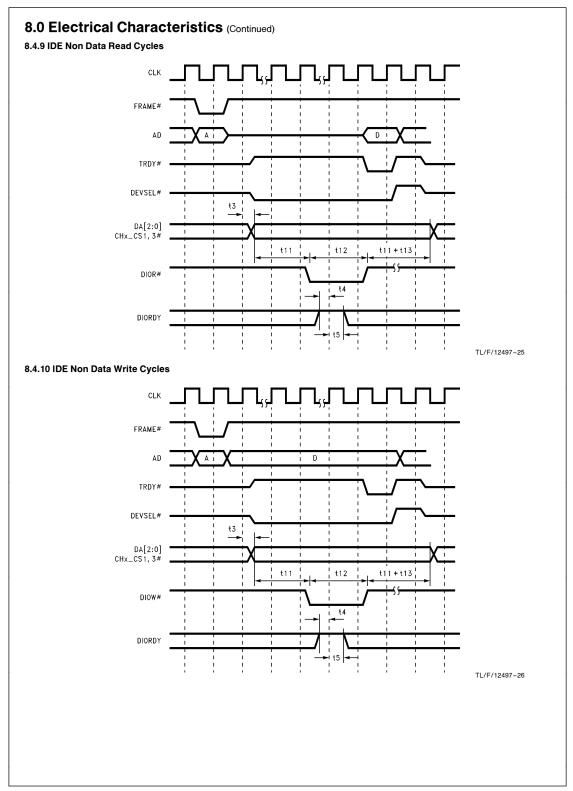

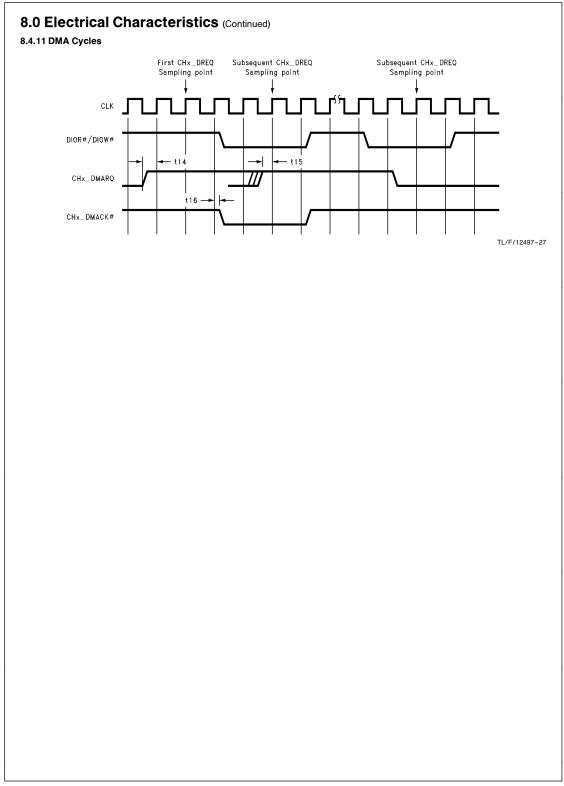

7.0 FUNCTIONAL DESCRIPTION (Continued) 7.4 DMA Controller 7.4.1 DMA Engine 7.4.1.1 Alignment 7.4.2 DMA Engine Protocol 7.4.2.1 Scenario 1 7.4.2.1.1 Bus Master Writes 7.4.2.1.2 Bus Master Reads 7.4.2.2 Scenario 2 7.4.2.2.1 Bus Master Writes 7.4.2.2.2 Bus Master Reads 7.4.2.3 Scenario 3 7.4.2.3.1 Bus Master Writes 7.4.2.3.2 Bus Master Reads 7.4.2.4 PCI Bus Request 7.4.2.4.1 PCI Master Reads 74242 PCI Master Writes 7.4.3 Master Aborts 7.4.4 Target Aborts 7.4.5 Data Synchronization 7.4.5.1 Normal 7.4.5.2 Byte Count is Less than IDE transfer size 7.4.5.3 Byte Count is Greater than IDE transfer size 7.4.5.4 Transfer in Progress 7.4.6 Bus Master Programming Sequence 8.0 ELECTRICAL CHARACTERISTICS 8.1 Absolute Maximum Ratings 8.2 Recommended Operating Conditions 8.3 DC Electrical Characteristics 8.4 AC Timing Specifications 8.4.1 PCI Timing Specifications 8.4.2 ATA/IDE Timing Specifications 8.4.3 Configuration Register Read Cycles 8.4.4 Configuration Register Write Cycles 8.4.5 Prefetch Cycles (Read Buffer Empty) 8.4.6 Prefetch Cycles (Read Buffer Not Empty) 8.4.7 Posted Write Cycles (Medium Decode) 8.4.8 Posted Write Cycles (Fast Decode) 8.4.9 IDE Non Data Read Cycles 8.4.10 IDE Non Data Write Cycles 8.4.11 DMA Cycles 9.0 APPLICATION INFORMATION 9.1 Power Control for IDE Drives 9.2 Native Mode Interrupt Support 9.3 DMA Bus Master Control Status Register 10.0 ERRATA

10.1 Target Mode

| AD[31:0]  | I/O |                                   |              |                       | Description                                                                                                                          |

|-----------|-----|-----------------------------------|--------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|           |     | MULTIPLEXED                       | ADDRESS      | S AND DATA.           | The direction of these pins are defined below:                                                                                       |

|           |     | Phase                             | Target       | Bus Master            |                                                                                                                                      |

|           |     | Address Phase                     | Input        | Output                |                                                                                                                                      |

|           |     | Data Phase:<br>-Read              | Output       | Input                 |                                                                                                                                      |

|           |     | -Write                            | Input        | Output                |                                                                                                                                      |

| C/BE[3:0] | Ι   | COMMAND/BY                        | TE ENABL     | <b>E</b> are multiple | ked Bus commands and Byte enables.                                                                                                   |

| PAR       | 1/0 | PARITY is even output when AD     |              |                       | nd C/BE[3:0]. PAR is an input when AD[31:0] is an input; it is a                                                                     |

| FRAME#    | 1/0 | CYCLE FRAME                       | is driven b  | y the initiator to    | o indicate the beginning and duration of an access.                                                                                  |

| TRDY#     | I/O | TARGET READ                       | Y indicates  | that the curre        | nt data phase of the transaction is ready to be completed.                                                                           |

| RDY#      | I/O | INITIATOR REA                     | DY indicat   | tes that the inlti    | ator is ready to complete the current data phase of the transac                                                                      |

| STOP#     | 0   |                                   |              |                       | equesting the initiator to stop the current transaction.                                                                             |

| DEVSEL#   | 1/0 | DEVICE SELEC<br>the current acces |              | ctively driven, ir    | ndicates the driving device has decoded its address as the targe                                                                     |

| DSEL      | Ι   |                                   |              |                       | ed as a chip select during configuration read and write transacti-<br>upper address lines AD[31:11].                                 |

| PERR#     | I/O |                                   |              |                       | a parity errors during all PCI transactions, except a Special Cycl<br>PAR are inputs, it is an input when AD[31:0] and PAR are outpu |

| SERR#     | 0   |                                   | other sys    | tem error wher        | dress parity errors, data parity errors on the Special Cycle<br>re the result will be catastrophic. When reporting address parity    |

| NTA#      | 0   | INTERRUPT. Int                    | errupt req   | uest A.               |                                                                                                                                      |

| REQ#      | 0   | <b>REQUEST</b> indica             | ates to the  | bus arbiter tha       | t this device wants to use the bus and become a bus master.                                                                          |

| GNT#      | Ι   | GRANT indicate                    | s to this de | evice that acces      | ss to the bus has been granted.                                                                                                      |

| CLK       | Ι   | CLOCK. 33 MHz                     | PCI Clock    | κ.                    |                                                                                                                                      |

| RST#      | I   | RESET. PCI Res                    | et.          |                       |                                                                                                                                      |

| Name                   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DD[15:0]               | 1/0  | <b>DRIVE DATA BUS.</b> The 16-bit bi-directional data bus to the drive. The lower 8 bits are used for non data 8-bit transfers (e.g., registers, ECC bytes).                                                                                                                                                                                                                          |

| DA[0]/<br>TEST#        | 1/0  | <b>DRIVE ADDRESS LINE 0 OR TEST.</b> The DA0 address line is asserted by the host to access a register or data port in the drive. It may also be used for testing: during PCI Reset, the rising edge of RST# samples this pin. If "low", all device output pins are forced to a TRI-STATE® level.                                                                                     |

| DA[1]/<br>ENABLE       | 1/0  | <b>DRIVE ADDRESS LINE 1 OR ENABLE.</b> During normal operation, the DA1 address line is asserted by the host to access a register or data port in the drive. During PCI Reset, the rising edge of RST# samples this pin and places its value in the Command Register bit-0.                                                                                                           |

| DA[2]/<br>LEGACY#      | 1/0  | <b>DRIVE ADDRESS LINE 2 OR LEGACY.</b> Dining normal operation, the DA2 address line is asserted by the host to access a register or data port in the drive. During PCI Reset, the rising edge of RST# samples this pin and places its value in the Programming Interface Register bits 0 and 2.                                                                                      |

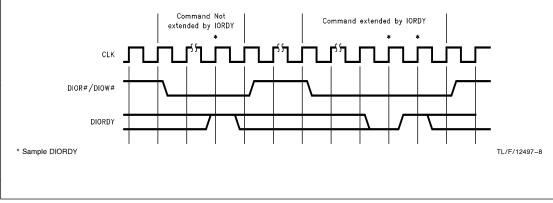

| DIORDY                 | I    | <b>DRIVE I/O CHANNEL READY.</b> When the drive is not ready to respond to a data transfer request, this signal is negated (low) to extend the disk transfer cycle of any register access (read or write). When DIORDY is not negated, it remains in a high impedance state.                                                                                                           |

| DIOR#                  | 0    | <b>DRIVE I/O READ.</b> The read strobe signal for both channels. The falling edge of DIOR # enables data from a register or the data port of the drive onto the PCI-IDE chip.                                                                                                                                                                                                         |

| DIOW#                  | 0    | <b>DRIVE I/O WRITE.</b> The write strobe signal for both channels. The rising edge of DIOW # clocks data from the PCI-IDE chip into the register or the data port of the drive.                                                                                                                                                                                                       |

| DRST#                  | 0    | <b>DRIVE RESET.</b> This signal from the PCI-IDE chip is asserted after power up or under software control (see Control Register bits Table A). It is active for as long as the PCI Reset signal, or if the reset bit in the Control Register is set.                                                                                                                                 |

| CH1_CS1#,<br>CH1_CS3#  | 0    | <b>CHANNEL 1 CHIP SELECT 1 AND 3.</b> CH1_CS1 # is the chip select signal to select the Command Block Registers. CH1_CS3 # is the chip select signal to select the Control Block Registers.                                                                                                                                                                                           |

| CH2_CS1#,<br>CH2_CS3#  | 0    | <b>CHANNEL 2 CHIP SELECT 1 AND 3.</b> CH2_CS1 # is the chip select signal to select the Command Block Registers. CH2_CS3 # is the chip select signal to select the Control Block Registers.                                                                                                                                                                                           |

| CH1_INTRQ<br>CH2_INTRQ | I    | <b>DRIVE INTERRUPTS.</b> These signals are used to interrupt the host system. CH1INTRQ is asserted only when the drive(s) on channel 1 has a pending interrupt, and the host has cleared nIEN in the drive's Device Control Register. CH2INTRQ is asserted only when the drive(s) on channel 2 has a pending interrupt, and the host has cleared nIEN in the Device Control Register. |

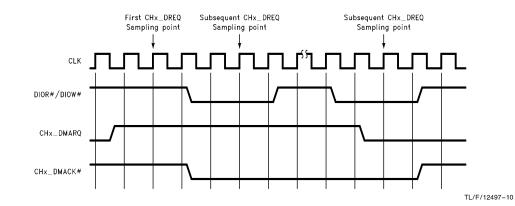

| CH1<br>DMARQ           | I    | <b>CHANNEL 1 DMA REQUEST.</b> This signal is used when using the internal DMA controller. When this signal is asserted, the selected drive on channel 1 is ready to transfer data.                                                                                                                                                                                                    |

| CH2<br>DMARQ           | I    | <b>CHANNEL 2 DMA REQUEST.</b> This signal is used when using the internal DMA controller. When this signal is asserted, the selected drive on channel 2 is ready to transfer data.                                                                                                                                                                                                    |

| CH1<br>DMACK#          | 0    | <b>CHANNEL 1 DMA ACKNOWLEDGE.</b> This signal is used when using the internal DMA controller. When asserted, it signals the selected drive on channel 1 that data has been accepted, or that data is available.                                                                                                                                                                       |

| CH2<br>DMACK#          | 0    | <b>CHANNEL 2 DMA ACKNOWLEDGE.</b> This signal is used when using the internal DMA controller. When asserted, it signals the selected drive on channel 2 that data has been accepted, or that data is available.                                                                                                                                                                       |

| IRQ14                  | 0    | IRQ14 mirrors CH1_INT if Legacy mode is enabled.                                                                                                                                                                                                                                                                                                                                      |

|                        | 0    | IRQ15 mirrors CH2_INT if Legacy mode is enabled.                                                                                                                                                                                                                                                                                                                                      |

| Name            | e    | Туре  | Description                                                                                                                                                                                                                                                                |

|-----------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDE_P           | WR   | 0     | <b>IDE Power.</b> During power up, this signal is used to disable power to the IDE cables. It may also be programmed on or off (see Control Register bits 3 and 18). It is active for as long as the PCI reset signal, or if the reset bit in the Control Register is set. |

| 4.4 PC          | OWER | AND G | ROUND                                                                                                                                                                                                                                                                      |

| Name            | Туре |       | Description                                                                                                                                                                                                                                                                |

| GND             | Ι    | VSS   | s or GROUND                                                                                                                                                                                                                                                                |

| V <sub>DD</sub> | Ι    | + 5   | V                                                                                                                                                                                                                                                                          |

|                 |      |       |                                                                                                                                                                                                                                                                            |

|                 |      |       |                                                                                                                                                                                                                                                                            |

Г

| Reg. #<br>(HEX) | R/W        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00-01           | R/W        | VENDOR ID—100Bh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 02–03           | R/W        | DEVICE ID—0002h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 02-03           | R/W<br>R/W | <ul> <li>COMMAND REGISTER (CMD). The command register provides coarse control over the device's ability to generate and respond to PCI cycles.</li> <li>Bit 0: IO Space. This bit is used to enable the device to respond to PCI I/O cycles. The default value is the sampled value of the ENABLE pin (sampled on the rising edge of RST #).</li> <li>0: Device is disabled</li> <li>1: Device is enabled</li> <li>Bit 1: Not used. 0 during reads.</li> <li>Bit 2: Bus Master. Controls the device's ability to act as a master on the PCI bus.</li> <li>0: Device cannot be bus master. This will disable all DMA operations even if internal DMA is enabled. (default value)</li> <li>1: Device can become a bus master. If this bit is set and internal DMA is enabled then the device can become a bus master.</li> <li>Bit 3-5: Not used. 000 during reads</li> <li>Bit 6: Parity Error (PERR #) response</li> <li>0: Ignore parity error</li> <li>Bit 7: Not used. 0 during reads</li> <li>Bit 8: System Error (SERR #) response</li> </ul>                                                                                                                                                                                                                                                                                                                                                 |

|                 |            | <ul> <li>Bit 0. System End (SEAR # ) response</li> <li>0: Disable system error checking (default)</li> <li>1: Enable system error checking</li> <li>Bit 9: Not used. 0 during reads. Fast back-to-back transactions to same agent.</li> <li>Bit 10–15: Not used. 000000 during reads.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 06-07           | R/W        | STATUS REGISTER (SR). The status register is used to record status information for PCI bus related events.<br>Reads to this register behave normally. Writes to this register cause bit(s) to be reset. A bit is reset whenever the<br>register is written with a "1" in the corresponding bit location.<br>Bit 0–6: Reserved<br>Bit 7: Always 0.<br>Bit 8: Data Parity Detected.<br>0: No parity detected<br>1: Parity detected<br>Bit 9–10: DEVSEL # timing<br>00: Reserved<br>01: Medium decode (default)<br>Bit 11: Signaled Target Abort<br>0: The device did not terminate a transaction with target abort.<br>1: The device has terminated a transaction with target abort.<br>Bit 12: Receive Target Abort<br>0: The device has not received a target abort<br>1: Transaction was not terminated with a master abort<br>1: Transaction has been terminated with a master abort<br>Bit 14: Signaled System Error (SERR #)<br>0: System error was not signaled<br>1: System error was not signaled<br>1: System error was signaled<br>Bit 15: Detected Parity Error (PERR #)<br>0: No parity error detected<br>1: Parity error detected |

| (HEX)    | R/W    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08       | R      | REV ID-01h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 09       | R/W    | PROGRAMMING INTERFACE (PIF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |        | <ul> <li>Bit 0: This bit determines what addresses channel 1 responds to. The default value is the sampled value of the LEGACY # pin (sampled on the rising edge of RST#).</li> <li>0: Channel 1 responds to addresses 1F0-1F7 and 3F6. Base registers 0 and 1 (10h-17h) are not used—legacy mode</li> <li>1: Channel 1 responds to addresses programmed in base register 0 and 1—native mode</li> <li>Bit 1: Always 1. Channel 1 has programmable selection of modes. Bit 0 determines which mode (default). This bit is read only.</li> <li>Bit 2: This bit determines what addresses channel 2 responds to. The default value is the sampled value of the LEGACY # pin (sampled on the rising edge of RST#).</li> <li>0: Channel 2 responds to addresses 170-177 and 376. Base registers 2 and 3 (18h-1Fh) are not used—legacy mode</li> <li>1: Channel 2 responds to addresses programmed in base register 2 and 3—native mode</li> <li>Bit 3: Always 1. Channel 2 has programmable selection of modes. Bit 2 determines which mode (default). This bit is read only.</li> <li>Bit 4-6: Reserved</li> <li>Bit 4-6: Reserved</li> <li>Bit 7 Always 1. Indicating that the device supports Master IDE.</li> </ul> |

| 0.0      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0A<br>0B | R<br>R | SUB-CLASS CODE—01h (IDE controller) CLASS CODE—01h (Mass Storage controller)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0C       | п      | Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0D       | R/W    | LATENCY TIMER. This register specifies, in units of PCI bus clocks, the value of the 8 most significant bits of an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 00       | 10.44  | 11-bit Latency Timer for this device when the internal DMA controller is used and the device is a bus master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0E       | R      | HEADER TYPE—00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0F       | R      | BIST—00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10–13    | R/W    | BASE ADDRESS REGISTER 0 (BAR0). Used for channel 1 data/command block accesses if channel 1 is programmed to be in native mode. The device decodes 8 bytes of address space for data/command block accesses. This register is always read/write, regardless of the setting of the Native/Legacy bit in the PIF.<br>Bit 0: always 1<br>Bit 1: always 0<br>Bit 2: always 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14–17    | R/W    | BASE ADDRESS REGISTER 1 (BAR1). Used for channel 1 control block access if channel 1 is programmed to be in native mode. The device decodes 4 bytes of address space for control block accesses. This register is always read/write, regardless of the setting of the Native/Legacy bit in the PIF.<br>Bit 0: always 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18–1B    | R/W    | Bit 1: always 0<br>BASE ADDRESS REGISTER 2 (BAR2). Used for channel 2 data/command block accesses if channel 2 is<br>programmed to be in native mode. The device decodes 8 bytes of address space for data/command block<br>accesses. This register is always read/write, regardless of the setting of the Native/Legacy bit in the PIF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |        | Bit 0: always 1<br>Bit 1: always 0<br>Bit 2: always 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Reg. #<br>(HEX) | R/W | Description                                                                                                                                                                                                                                                                                                                               |

|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1C-1F           | R/W | BASE ADDRESS REGISTER 3 (BAR3). Used for channel 2 control block access if channel 2 is programmed to be in native mode. The device decodes 4 bytes of address space for control block accesses. This register is always read/write, regardless of the setting of the Native/Legacy bit in the PIF.<br>Bit 0: always 1<br>Bit 1: always 0 |

| 20–23           | R/W | BASE ADDRESS REGISTER 4 (BAR4). Used to address the Bus Master IDE control and status registers.<br>Bit 0: always 1<br>Bit 1: always 0<br>Bit 2: always 0<br>Bit 3: always 0                                                                                                                                                              |

| 24-3B           |     | NOT USED                                                                                                                                                                                                                                                                                                                                  |

| 3C              | R/W | INTERRUPT LINE (default is 0Eh)                                                                                                                                                                                                                                                                                                           |

| 3D              | R   | INTERRUPT PIN<br>Bit 0: Always 1. Designates INTA.<br>Bit 1-7: 0000000                                                                                                                                                                                                                                                                    |

| 3E-3F           |     | NOT USED                                                                                                                                                                                                                                                                                                                                  |

|                 |     |                                                                                                                                                                                                                                                                                                                                           |

|                 |     |                                                                                                                                                                                                                                                                                                                                           |

| Reg. #<br>(HEX) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-42           | R/W | CONTROL REGISTER (CTRL). Default value is 0000000h (after Reset)<br>Bit 0: Reserved<br>Bit 1: 0 (Always): Reserved<br>Bit 2: 0 = Software reset to CH1/CH2 off<br>1 = Software reset to CH1/CH2 on<br>Bit 3: 0 = IDEPWR set on<br>1 = IDEPWR set off<br>Note: Bit 18 must be set to "1" to allow Bit 3 to toggle IDEPWR.                                                                                                                                                                                                                                                                                                                                                                                         |

|                 |     | B18 B3 IDE_PWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |     | 0X1 (Default at power up reset)101 (IDE_PWR set to on)110 (IDE_PWR set to off)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |     | (*) Asserted for t_25 s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 |     | Bit 4: 0 = Map CH1_INT according to legacy/native mapping scheme<br>1 = Map CH1_INT to INTA regardless if in legacy mode<br>Bit 5: 0 = Map CH2_INT according to legacy/native mapping scheme<br>1 = Map CH2_INT to INTA regardless if in legacy mode<br>Bit 6: 0 = INTA # unmasked<br>1 = INTA # masked<br>Bit 7: 0 = Write to vendor ID and device ID registers disabled<br>1 = Write to vendor ID and device ID registers enabled<br>Bit 8: 0 = Channel 1 interrupt unmasked<br>1 = Channel 1 interrupt unmasked<br>Bit 9: 0 = Channel 2 interrupt masked<br>Bit 10: 0 = PCI Base Address Register 2 and 3 enabled<br>1 = PCI data phase WATCHDOG™ timer disabled<br>1 = PCI data phase WATCHDOG timer enabled |

|                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reg. #<br>(HEX) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-42            | R/W | CONTROL REGISTER—(Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (Continued)     |     | <ul> <li>Bit 12: 0 = All accesses mapped to Base Address Register 10 and 14 bypass the data buffers</li> <li>1 = IDE device accesses (Control Register bit 14 = 0) to offset 0 of the base address window register 10 and 14 are buffered</li> <li>Bit 13: 0 = All accesses mapped to Base Address Register 18 and 1C bypass the data buffers</li> <li>1 = IDE device accesses (Control Register bit 15 = 0) to offset 0 of the base address window register 18 and 1C are buffered</li> <li>Bit 14: 0 = IDE device mapped to base address window registers 10 and 14</li> <li>1 = Non-IDE device mapped to base address window registers 18 and 1C</li> <li>1 = IDE device mapped to base address window registers 18 and 1C</li> <li>1 = Non-IDE device mapped to base address window registers 18 and 1C</li> <li>1 = Non-IDE device mapped to base address window registers 18 and 1C</li> <li>1 = Non-IDE device mapped to base address window registers 18 and 1C</li> <li>1 = Non-IDE device mapped to base address window registers 18 and 1C</li> <li>1 = Non-IDE device mapped to base address window registers 18 and 1C</li> <li>1 = Non-IDE device mapped to base address window registers 18 and 1C</li> <li>1 = Non-IDE device mapped to base address window registers 18 and 1C</li> </ul> |

|                 |     | 1 = Channel 1 prefetch buffer enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 |     | Bit 17: 0 = Channel 2 prefetch buffer disabled<br>1 = Channel 2 prefetch buffer enabled<br>Bit 18: 0 = Reset/idle State.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |     | 1 = IDE_PWR has power on/off function<br>Bit 19: Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |     | Bit 19: Reserved<br>Bit 29: $0 =$ Channel 1 drive 1 IORDY handshaking for flow control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |     | 1 = Channel 1 drive 1 DMARQ/DMACK handshaking for flow control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 |     | Bit 21: 0 = Channel 1 drive 2 IORDY handshaking for flow control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                 |     | <ul> <li>1 = Channel 1 drive 2 DMARQ/DMACK handshaking for flow control</li> <li>Bit 22: 0 = Channel 2 drive 1 IORDY handshaking for flow control</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |     | 1 = Channel 2 drive 1 DMARQ/DMACK handshaking for flow control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 |     | Bit 23: $0 =$ Channel 2 drive 2 IORDY handshaking for flow control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

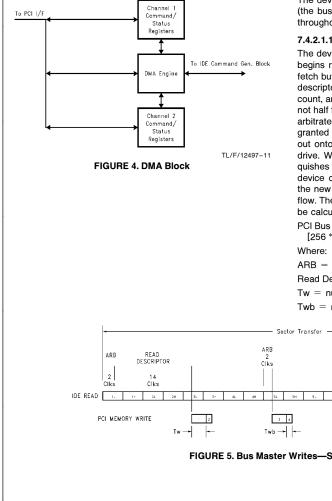

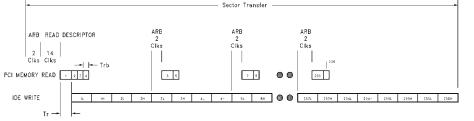

|                 |     | 1 = Channel 2 drive 2 DMARQ/DMACK handshaking for flow control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |