# **Side-Airbag Sensor Dual Interface**

## **Description**

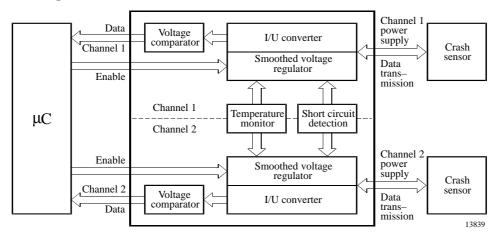

The U6268B is an interface IC for remote automotive sensors. It links the crash sensors in the driver- and passenger door with the main airbag unit in the dashboard. Two identical channels supply the external sensors and receive digital information from them via one active wire each. The interface supplies the external sensors with a pre-regulated smoothed voltage, the external units transmit the digital information back to the

interface by current modulation.

As the device is for safety critical applications, highest data transmission security is mandatory. With high immunity against cross-coupling between the two channels, the U6228B is tailored for the harsh automotive environment.

#### **Features**

- Two identical interface channels

- Provides a pre-regulated smoothed voltage and a supply current up to 50 mA for the sensors

- Receives data from the sensors by current modulation with a transmission rate of 60 kBaud (transmission bandwidth 500 kHz)

- Current modulation provides high noise immunity for data transfer

- TTL-compatible input activate the sensor

- Data output can be directly connected to a microcontroller input

- Operation supply voltage range 5.7 V  $\leq$  V<sub>S</sub>  $\leq$  40 V

- ESD protection according to MIL-STD-883C test method 3015.7

- High-level EMI protection

### **Benefits**

Voltage supply and data transmission with one active wire over long distances

## **Ordering Information**

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| U6268B               | SO16    |         |

## **Block Diagram**

Figure 1. Block diagram

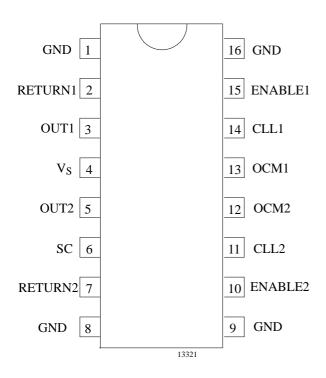

### **Pin Description**

Figure 2. Pinning

| Pin  | Symbol  | Function                                                                                                    |

|------|---------|-------------------------------------------------------------------------------------------------------------|

| 1    | GND     | Ground and reference pin                                                                                    |

| 2    | RETURN1 | Return line of the external unit, internally connected to GND via a line-protection transistor              |

| 3    | OUT1    | Voltage-stabilized supply output and current-modulation input                                               |

| 4    | $V_{S}$ | Supply voltage of the IC                                                                                    |

| 5    | OUT2    | Voltage stabilized supply output and current modulation input                                               |

| 6    | SC      | Smooth time constant for slow voltage change at both OUT pins                                               |

| 7    | RETURN2 | Return line of the external unit, internally connected to GND via a line-protection transistor              |

| 8, 9 | GND     | Ground and reference pin                                                                                    |

| 10   | ENABLE1 | Controls OUT1 voltage,<br>ENABLE1 High means OUT1<br>active, ENABLE1 Low or open<br>means OUT1 switched off |

| 11   | CLL2    | Current logic level output, low<br>at high OUT2 current,<br>monitoring via OCM2                             |

| 12   | OCM2    | Analog current output, representing 1/10 current of OUT2                                                    |

| 13   | OCM1    | Analog current output, representing 1/10 current of OUT1                                                    |

| 14   | CLL1    | Current logic level output, low<br>at high OUT1 current, moni-<br>toring via OCM1                           |

| 15   | ENABLE2 | Controls OUT2 voltage,<br>ENABLE2 High means OUT2<br>active, ENABLE1 Low or open<br>means OUT2 switched off |

| 16   | GND     | Ground and reference pin                                                                                    |

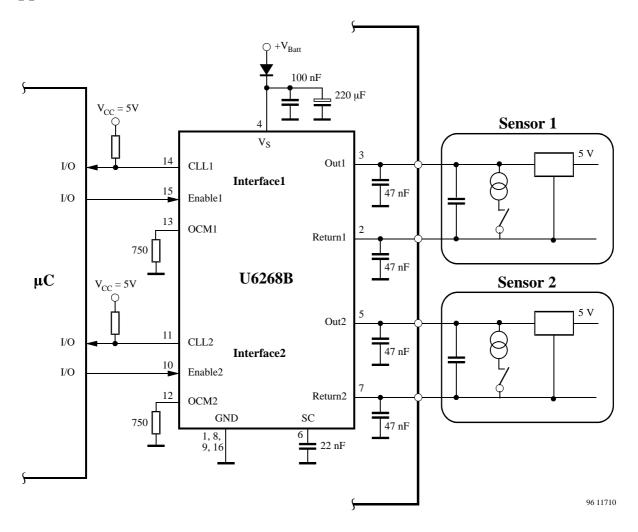

Figure 3. Application circuit

## **Functional Description**

### $V_S$

The IC and the external units are powered via the  $V_S$  Pin 4. This pin is connected to the battery via a reverse battery protection diode. An electrolythic capacitor of 22  $\mu F$  smoothes the voltage and absorbes positive and negative transients.

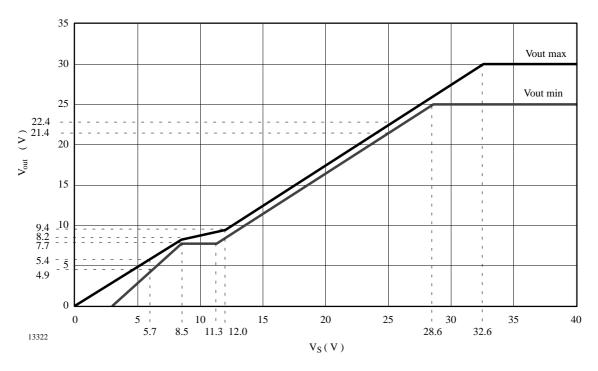

### OUT1, OUT2

OUTx provides a smoothed, very slowly changing supply

voltage for the external units and monitors the output current. During normal operating conditions, the OUTx voltage is typ. 3 V below  $V_S$ , and changes very slowly with a varying battery voltage in order to suppress disturbances in the data transmission. At low  $V_S$  (5.7 to 8.5 V), the OUTx voltage is typ. 0.5 V below  $V_S$ . This voltage difference is reduced in order to ensure sufficient supply voltage for the external unit between OUTx and RETURNx. The output current capability is 50 mA. The internal pull-down current at OUTx is typically 3 mA.

Figure 4. Output voltage with tolerances vs. supply voltage

The data transmission from the external unit to the interface IC is carried out on the same line by varying the current level. The quiescent current consumption of the external unit is about 5 to 15 mA. This current level is interpreted as logic high level at CLL-pin. The external unit can switch on an additional current of 30 mA, interpreted by the interface as logic low. The current changes within approximately 1  $\mu s$ , sufficient for a transmission rate of about 60 kBaud, requiring a transmission bandwidth of about 500 kHz for the current-monitoring subcircuit and the OCM output. For a good current transmission behaviour, the dynamic resistance of OUTx may not exceed 12  $\Omega$  inside the bandwidth range (total of 15  $\Omega$  for OUTx and RETURN).

The OUTx- voltage can be switched off by ENABLEx = LOW to reset the external unit and to reduce power dissipation during fault conditions.

The OUT pins are overtemperature- and short-circuit protected. A reverse polarity diode at Pin  $V_S$  (Pin 4) ensures that no current is fed back to the  $V_{Batt}$ -system in the case of a short between OUTx and  $V_{Batt}$ . A minimum capacity of 33 nF is required at the pins OUTx .

#### **ENABLE1, ENABLE2**

ENABLEx is a microcontroller-compatible input which switches the related output on or off.

- Low or open circuit applied to ENABLEx switches the related OUTx and RETURNx off (high impedance). A sink current at Pin OUTx discharges the capacitive load.

- High applied to ENABLEx switches the related OUTx and RETURNx on to supply the external unit.

#### OCM1, OCM2

The output current of OUTx is monitored with a transmission factor of 0.1 to the OCMx. With a resistor from OCM to GND, the current is converted to a voltage. The electrical characteristics are specified by  $R_{OCM}=750~\Omega.$  The CLL-current threshold, the OUT-current limitation and the OUT-current detection can be changed by varying  $R_{OCM}$  in a range from  $500~\Omega$  to  $1~k\Omega.$

The current monitoring enables to detect overcurrent conditions at OUTx (short circuit to GND or RETURNx) and to detect low current conditions at OUTx (short circuit to  $V_{Batt}$  or open load).

The internal pull-down current at the OUTx creates no OCMx-current. During enable, the minimum voltage at OCMx is the saturation voltage of an internal NPN-transistor with typically 0.1 V. The maximum voltage at OCM is limited by an internal clamping diode to 5.3 V.

#### CLL1, CLL2

The current at Pin OUTx is logical evaluated and ready to use for a microcontroller input. With this stage, the

# **U6268B**

logic data transmission from the external unit to the interface is completed.

CLLx is the output stage of a comparator with an internal threshold and with the OCMx input. A OCMx-voltage higher than 2.4 V creates a logic low at CLLx, and a OCMx-voltage lower than 1.43 V creates a logic high at CLLx. The comparator has an internal hysteresis with typically 0.4 V.

With the pull-down resistor  $R_{OCMx}=750~\Omega$  at OCMx, the correct OUTx-current threshold related to the logical output CLLx is ensured. The CLLx is 'low' if the OUTx-current is higher than 27.3 mA, and the CLLx is 'high', if the OUTx-current is lower than 19.1 mA. The comparator has an internal hysteresis of typically 5 mA. The tolerance of the  $R_{OCM}$  resistor is assumed to be 0%.

The CLL-pin is an open-collector output and needs a pull-up resistor of typically 2  $k\Omega$  to the 5-V supply. For ESD protection, a 7-V Zener diode is implemented.

### **RETURN 1, RETURN 2**

The RETURNx pin provides a low-ohmic connection to GND via a switched open-collector NPN-transistor. If ENABLEx is high, RETURNx is switched on with a saturation voltage less than 0.5 V at  $I_{RETURNx} \le 50$  mA. If ENABLEx is low or open, RETURNx is a current sink with  $\le 2$  mA. RETURNx is current-limited at typically 150 mA.

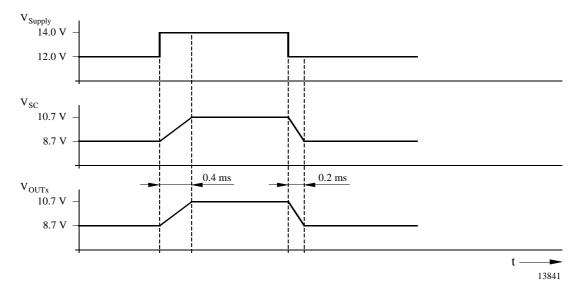

#### SC

The smooth capacitor is designed to realize the long-time constant for the slow voltage change at OUTx for both interface channels. The capacity is typ. 22 nF. At the rising edge of  $V_{Batt}$ , the maximum slew rate is  $V_{OUTx} = 5 \text{ V/ms}$ , and at the falling edge of  $V_{Batt}$ , the maximum slew rate is  $V_{OUTx} = 10 \text{ V/ms}$ .

#### **GND-Pins**

By means of a GND bond from the chip to Pin 1 and Pin 8, high ground breakage security is achieved and lowest voltage drop and ground shift between IC- and circuit ground is provided. The four GND pins and the die pad are directly connected to the copper leadframe, resulting in a very low thermal resistance,  $R_{thJC}$ . In order to achieve a good thermal resistance,  $R_{thJA}$ , a good copper connec-

tion from the four GND pins to the metal parts of the modul housing is also recommended.

### **Power Dissipation**

Worst case calculation of the supply current Is:

$$I_S = 1,278 \times (I_{OUT1} + I_{OUT2}) + 18 \text{ mA}$$

Worst case calculation of the IC's power dissipation P<sub>V</sub>:

$$\begin{split} P_V = & \left(V_S \times I_S\right) - \left[\left(V_S - V_{diff} - V_{ret\text{-}sat}\right) \times \left(I_{OUT1} + I_{OUT2}\right) \\ + & R_{OCM} \times \left(\left(I_{OUT1}^2 + I_{OUT2}^2\right) / 81\right)\right] \end{split}$$

$\begin{array}{ll} V_S &= \text{supply voltage 5.7 to 25 V} \\ \text{voltage difference } V_S \text{ to } V_{OUTx} \\ V_{diff} &= 3.6 \text{ at } 12 \text{ V} \leq V_S \leq 25 \text{ V} \\ V_{diff} &= 0.8 \text{ at } 5.7 \text{ V} \leq V_S \leq 8.5 \text{ V} \\ V_{ret\text{-sat}} = 0.5 \text{ V} \text{ saturation voltage return} \end{array}$

$I_{OUTx}$  = output current at Pin OUTx = 0 to 60 mA

$R_{OCM}$  = resistor at Pin OCMx

### **Selective Overtemperature Protection**

An overtemperature protection is integrated which generates a switch-off signal at a chip temperature of typically  $T_i = 160$ °C and a switch-on signal at typically  $T_i = 150$ °C.

In case of a detected overtemperature, only the corresponding channel is disabled. The other channel stays enabled.

The RETURNx is switched off if the voltage at RETURNx is higher than 2 V (short-circuit comparator threshold) and overtemperature is detected.

The OUTx is switched off if the voltage at OCMx is higher than 4.6 V (overcurrent detection level) and overtemperature is detected. The OCM voltage monitors the output current at OUTx via the current ratio of 0.1. The overcurrent-detection level of OUTx can be varied by changing the OCMx resistor. If OUTx is switched off by overtemperature and overcurrent detection, the CLLx output remains logic low (overcurrent).

As the IC is only overtemperature-protected for short-circuit conditions at RETURNx or OUTx, it has to be checked in each application that the chip temperature does not exceed  $T_{jmax} = 150^{\circ}\text{C}$  in normal operation.

#### **Test Hint**

The overtemperature signal can be activated by connecting ENABLE1 or ENABLE2 to  $9\ V/\ 10\ mA$ .

## **Absolute Maximum Ratings**

| Parameters                                                                                          | Symbol                                    | Min.                | Тур. | Max.     | Unit     |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------|------|----------|----------|

| Supply voltage                                                                                      | $V_{S}$                                   | -0.6                |      | 40       | V        |

| Voltage at pins CLL1, CLL2, ENABLE1, ENABLE2                                                        |                                           | -0.3                |      | 6        | V        |

| Voltage at SC                                                                                       | $V_{SC}$                                  | -0.3                |      | 30       | V        |

| Voltage at OCM1, OCM2                                                                               | V <sub>OCMx</sub>                         | -0.3                |      | 6.8      | V        |

| Voltage at RETURN1, RETURN2                                                                         | V <sub>RETURNx</sub>                      | -1                  |      | 27       | V        |

| Voltage at OUT1, OUT2                                                                               | V <sub>OUTx</sub>                         | -1                  |      | 40       | V        |

| Current at supply (both channels OUTx and RETURNx shorted)                                          | $I_{S}$                                   |                     |      | 240      | mA       |

| Current at logical pins: CLL1, CLL2<br>ENABLE1, ENABLE2                                             | I <sub>CCLx</sub><br>I <sub>ENABLEx</sub> |                     |      | 3<br>0.1 | mA<br>mA |

| Current at SC (SC related to GND or V <sub>Batt</sub> )                                             | $I_{SC}$                                  | -110                |      | 220      | μΑ       |

| Current at pins to external unit OUT1, OUT2, RETURN1, RETURN2                                       |                                           | internal<br>limited |      |          |          |

| ESD classification Human body model (100 pF, 1.5 k $\Omega$ ) Machine model (200 pF, 0.0 $\Omega$ ) | All pins                                  | ±2000<br>±200       |      |          | V<br>V   |

| Ambient temperature range                                                                           | T <sub>amb</sub>                          | -40                 |      | 95       | °C       |

| Junction temperature range                                                                          | $T_{j}$                                   | -40                 |      | 150      | °C       |

| Storage temperature range                                                                           | T <sub>stg</sub>                          | -55                 |      | 125      | °C       |

## **Thermal Resistance**

| Parameters                                            | Symbol     | Value | Unit |

|-------------------------------------------------------|------------|-------|------|

| Junction to pin                                       | $R_{thJC}$ | 36    | k/W  |

| Junction ambient is reachable with a big pad size for | $R_{thJA}$ | 65    | k/W  |

| GND near a screw or the metal housing                 |            |       |      |

## **Electrical Characteristics**

$T_{amb} = -40$  to 95°C and  $T_j = -40$  to 150°C, operation supply voltage range 5.7 to 18 V continuously,  $\leq$  25 V for max. 25 min,  $\leq$  40 V for up to 500 ms. The current values are based on the 750  $\Omega$  0% resistor at OCM1/OCM2

| Parameters             | Test Conditions / Pins                                                                        | Symbol         | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------------------------------------------------------------|----------------|------|------|------|------|

| Supply current         | Outputs disabled, $V_S \le 18 \text{ V}$                                                      | $I_S$          |      |      | 8    | mA   |

| $T_j \ge 125^{\circ}C$ | Outputs disabled, $V_S \le 40 \text{ V}$                                                      | $I_S$          |      |      | 14   | mA   |

|                        | One output enabled, $V_S \le 18 \text{ V}$                                                    | $I_S$          |      |      | 13   | mA   |

|                        | Both outputs enabled, $V_S \le 18 \text{ V}$                                                  | I <sub>S</sub> |      |      | 18   | mA   |

|                        | Output load $2 \times 15$ mA, $V_S \le 18$ V                                                  | $I_S$          |      |      | 56   | mA   |

|                        | Output load $2 \times 28$ mA, $V_S \le 18$ V                                                  | $I_S$          |      |      | 90   | mA   |

|                        | Output load $2 \times 50$ mA, $V_S \le 18$ V                                                  | $I_S$          |      |      | 146  | mA   |

|                        | Output load $2 \times 60 \text{ mA}$ ,<br>$V_S \le 18 \text{ V } (T_j > 125^{\circ}\text{C})$ | $I_S$          |      |      | 171  | mA   |

|                        | Both channels OUTx and RETURNx shorted, $V_S \le 18 \text{ V}$                                | $I_S$          |      |      | 200  | mA   |

| <b>Function SC</b>     |                                                                                               |                |      |      |      |      |

5 (12)

| Parameters                                                     | Test Conditions / Pins                                                                          | Symbol                 | Min.         | Тур. | Max.     | Unit     |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------|--------------|------|----------|----------|

| Voltage at SC                                                  | $V_S = 5.7 \text{ V}$                                                                           | V <sub>SC</sub>        | 5.1          | -71  | 5.3      | V        |

| Voltage at SC                                                  | $V_S = 12.5 \text{ V}$                                                                          | V <sub>SC</sub>        | 9            |      | 9.4      | V        |

| Maximal voltage at SC                                          | $V_S = 40 \text{ V}$                                                                            | V <sub>SCmax</sub>     |              |      | 30       | V        |

| SC-discharge current                                           | Voltage SC = $V_{SC} - 3 V$<br>5.7 V $\leq V_S \leq 40 V$                                       | I <sub>SC_dis</sub>    | 33           |      | 82       | μΑ       |

| SC-charge current                                              | $   Voltage SC = V_{SC} - 3 V $ $   5.7 V \le V_S \le 40 V $                                    | I <sub>SC_ch</sub>     | -58          |      | -20      | μΑ       |

| Function OUT1 and OUT                                          | 2 (see figure 4)                                                                                |                        |              |      |          |          |

| Voltage difference,                                            | $I_{OUTx} = 5 \text{ to } 50 \text{ mA}$                                                        |                        |              |      |          |          |

| $V_S$ to $V_{OUTx}$                                            | $5.7 \text{ V} \le \text{V}_{\text{S}} \le 8.5 \text{ V}$                                       | V <sub>diff_low</sub>  | 0.3          |      | 0.8      | V        |

|                                                                | $12 \text{ V} \leq \text{V}_{\text{S}} \leq 25 \text{ V}$                                       | V <sub>diff_high</sub> | 2.6          |      | 3.6      | V        |

| Output voltage OUTx                                            | $8.5 \text{ V} \le \text{V}_{\text{S}} \le 11.3 \text{ V}$                                      | V <sub>OUT_med</sub>   | 7.7          |      |          | V        |

| Maximal voltage at OUTx                                        | $V_S = 40 \text{ V}$                                                                            | V <sub>OUT_max</sub>   | 25           |      | 30       | V        |

| Current mirror ratio,                                          | $V_S \le 40 \text{ V}, I_{OUTx} = 5 \text{ to } 15 \text{ mA}$                                  |                        | 0.09         |      | 0.12     |          |

| $I_{OCMx}/I_{OUTx}$                                            | $V_S \le 25 \text{ V}, I_{OUTx} = 15 \text{ to } 50 \text{mA}$                                  | I <sub>OUT_ratio</sub> | 0.10         |      | 0.11     |          |

|                                                                | $V_S \le 40 \text{ V}, I_{OUTx} = 15 \text{ to } 50 \text{mA}$                                  |                        | 0.097        |      | 0.11     |          |

| Linearity of mirror ratio I <sub>OCMx</sub> /I <sub>OUTx</sub> |                                                                                                 | Ratio_lin              | -5           |      | 5        | %        |

| Dynamic resistance<br>OUTx                                     | $V_S \le 40 \text{ V I}_{OUT} = 15 \text{ to } 50 \text{ mA}$                                   | R <sub>OUT</sub>       | 2            |      | 12       | Ω        |

| Dynamic resistance<br>OUTx + RETURNx                           | $V_S \le 40 \text{ V I}_{OUT} = 15 \text{ to } 50 \text{ mA}$                                   | R <sub>Dyn</sub>       | 4            |      | 15       | Ω        |

| OUTx current limitation                                        | $V_S \le 18 \text{ V}$                                                                          | I <sub>OUT_lim</sub>   | -80          |      | -60      | mA       |

| (OUTx short to GND)                                            | $V_S \le 40 \text{ V}$                                                                          |                        | -105         |      | -60      | mA       |

| Overcurrent detection level general                            | $T_j < 125^{\circ}C$                                                                            | I <sub>OUT_det</sub>   | -70          |      | -51      | mA       |

| Overcurrent detection level                                    | $T_j \ge 125^{\circ}C$<br>Always valid: current limitation is higher than overcurrent detection | I <sub>OUT_det</sub>   | -60          |      | -51      | mA       |

| Maximum OUTx current (OUTx short to GND)                       | $V_S = 14 \text{ V}$ , OCMx shorted to GND                                                      | I <sub>OUT_max</sub>   | -140         |      | -85      | mA       |

| Leakage current at disabled OUTx                               | OUT short to GND $V_S \le 25 \text{ V}$<br>OUT short to GND $V_S \le 38.5 \text{ V}$            | I <sub>OUT_leak</sub>  | -0.02<br>-12 |      |          | mA<br>mA |

| Leakage voltage at disabled OUTx                               | OUT open $V_S \le 38.5 \text{ V}$                                                               | V <sub>OUT_leak</sub>  |              |      | 4.3      | V        |

| Internal pull-down current                                     | $V_{S} \le 18 \text{ V}$ $V_{S} \le 40 \text{ V}$                                               | I <sub>OUT_sink</sub>  | 1.8<br>2.5   |      | 4<br>4.5 | mA<br>mA |

| Supply rejection-ratio                                         | $V_{SC} = 7.6 \text{ V}$                                                                        | V <sub>rej_mV</sub>    |              |      | 80       | mV       |

| Supply rejection-ratio                                         | Variation of V <sub>S</sub> 8.4 to 40 V<br>in 10 µs                                             | V <sub>rej_dB</sub>    | 51.9         |      |          | dB       |

| Minimum capacity at<br>OUTx for phase margin                   |                                                                                                 | C <sub>OUT_min</sub>   | 33           |      |          | nF       |

| Delay time with Cout = 47 nF                                   | Switching on ENABLE = 1 to 90% V <sub>OUT</sub> reached                                         | Enable_on              | 3            |      | 30       | μs       |

| Court - 77 III                                                 | Switching off ENABLE = 0 to 10% V <sub>OUT</sub> reached                                        | Enable_off             | 30           |      | 100      | μs       |

| Function OCM1, OCM2                                            |                                                                                                 |                        |              | _    |          |          |

| Parameters                                     | Test Conditions / Pins                                                                 | Symbol                       | Min. | Тур. | Max. | Unit |

|------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------|------|------|------|------|

| Voltage threshold CLL-                         | CLLx low-level voltage threshold                                                       | V <sub>CLL_L</sub>           | 1.75 | Typ. | 2.4  | V    |

| comparator comparator                          | CLLx high-level voltage threshold                                                      | VCLL_L<br>V <sub>CLL_H</sub> | 1.43 |      | 1.9  | v    |

| Comparator                                     | Voltage hysteresis                                                                     | V <sub>CLL_hys</sub>         | 0.26 |      | 0.6  | v    |

| Minimal voltage at OCMx                        | $I_{OUT} = 0$ to 5 mA                                                                  | V <sub>OCM_min</sub>         |      |      | 0.5  | V    |

| Current-limitation level                       | $V_S \le 40 \text{ V OUTx short to GND}$                                               | V <sub>OCM_lim</sub>         | 4.3  |      | 5.3  | V    |

| Overcurrent-detection level                    | $V_S \le 40 \text{ V}$                                                                 | V <sub>OCM_det</sub>         | 4.2  |      | 4.9  | V    |

| Current limitation minus overcurrent detection | V <sub>OCM_lim</sub> - V <sub>OCM_over</sub>                                           | Δ_lim_OCM                    | 0.15 |      | 0.5  | V    |

| Intern. pull-down current                      |                                                                                        | I <sub>OCM_sink</sub>        | 0.1  |      | 0.45 | mA   |

| Function RETURN1, RET                          | ΓURN2                                                                                  |                              |      |      |      |      |

| Enable high saturation voltage                 | $I_{RETURN} = 50 \text{ mA}$                                                           | V <sub>ret_sat</sub>         |      |      | 0.5  | V    |

| Dynamic resistance                             | $dI \ge 10 \text{ mA}$                                                                 | R <sub>ret</sub>             | 2    |      | 8    | Ω    |

| Current limitation                             | Enable high, V <sub>RETURNx</sub> = 2 V                                                | I <sub>ret_lim</sub>         | 60   |      | 150  | mA   |

| RETURNx is always                              | Enable high, $V_{RETURNx} \le 18 \text{ V}$                                            | I <sub>ret_lim</sub>         | 70   |      | 200  | mA   |

| higher than current limitation OUTx            | Enable low $V_{RETURNx} \le 18 \text{ V}$                                              | $I_{ret\_lim}$               | 0.8  |      | 2    | mA   |

| Overcurrent-detection level                    | Threshold comparator, switch-off return                                                | I <sub>ret_low</sub>         | 1.4  |      | 2    | V    |

|                                                | Threshold comparator, switch-on return                                                 | I <sub>ret_high</sub>        | 1.1  |      | 1.5  | V    |

|                                                | Hysteresis                                                                             | I <sub>ret_hys</sub>         | 0.2  |      | 0.7  | V    |

| Delay time<br>C <sub>RETURN</sub> = 47 nF      | Switching on I <sub>RETURN</sub> at 50 mA<br>Switching off I <sub>RETURN</sub> at 1 mA | t <sub>dRet_on</sub>         | 3    |      | 30   | μs   |

| RETORIV                                        | Z KLICKIV                                                                              | t <sub>dRet_off</sub>        | 30   |      | 90   | μs   |

| Function CLL1, CLL2 (C                         | LLx with 2 kΩ to 5 V)                                                                  |                              | 1    | '    | '    |      |

| I <sub>OUT</sub> threshold CLL                 | $R_{OCM} = 750 \Omega$                                                                 |                              |      |      |      |      |

| comparator                                     | CLL low-level threshold                                                                | $I_{CLL\_L}$                 | 23.3 |      | 27.3 | mA   |

|                                                | CLL high-level threshold                                                               | $I_{CLL\_H}$                 | 19.1 |      | 22.3 | mA   |

|                                                | Hysteresis                                                                             | I <sub>CLL_hys</sub>         | 3.5  |      | 8.2  | mA   |

| CLL saturation voltage                         | $I_{CLL} \le 2.5 \text{ mA}$                                                           | V <sub>CLL_sat</sub>         |      |      | 0.4  | V    |

| CLL leakage current                            | $V_{CLL} \le 6.5 \text{ V}$                                                            | I <sub>CLL_leak</sub>        |      |      | 1    | μΑ   |

| Response time to current                       | I <sub>OUT</sub> to CLL rise                                                           | t <sub>Cll_rise</sub>        | 0.1  |      | 2    | μs   |

| change                                         | I <sub>OUT</sub> to CLL fall                                                           | t <sub>Cll_fall</sub>        | 0.1  |      | 2    | μs   |

|                                                | Max. difference between rise and fall time                                             | $t_{\Delta	ext{-rise-fall}}$ |      |      | 1    | μs   |

| CLL output switching                           | Rise                                                                                   | t <sub>CLL_rise</sub>        |      |      | 1    | μs   |

| speed                                          | Fall                                                                                   | t <sub>CLL-fall</sub>        |      |      | 1    | μs   |

| Current transmission rate                      |                                                                                        |                              | 60   |      |      | kHz  |

| Current transmission 3 dB bandwidth            |                                                                                        |                              | 500  |      |      | kHz  |

| Function ENABLE1, ENA                          | ABLE2                                                                                  |                              | 1    | 1    | 1    | 1    |

| Enable low–level threshold                     |                                                                                        | V <sub>Enable_off</sub>      | 2    |      | 6.5  | V    |

| Enable high-level threshold                    |                                                                                        | V <sub>Enable_on</sub>       | -0.3 |      | 0.8  | V    |

| Parameters                | Test Conditions / Pins                              | Symbol              | Min. | Тур. | Max. | Unit |

|---------------------------|-----------------------------------------------------|---------------------|------|------|------|------|

| Enable input pull-down    |                                                     | I <sub>Enable</sub> | 10   |      | 100  | μΑ   |

| current (to ensure output |                                                     |                     |      |      |      |      |

| disabled during power-off |                                                     |                     |      |      |      |      |

| and reset of micro-       |                                                     |                     |      |      |      |      |

| controller)               |                                                     |                     |      |      |      |      |

| Power dissipation         |                                                     |                     |      |      |      |      |

| Power dissipation 1       | $V_S = 18 \text{ V},$                               | Pdis1               |      |      | 1    | W    |

| $T_i \ge 125^{\circ}C$    | $I_{OUT1} = 28 \text{ mA},$                         |                     |      |      |      |      |

| ,                         | I <sub>OUT2</sub> at overcurrent detection level    |                     |      |      |      |      |

|                           | or                                                  |                     |      |      |      |      |

|                           | $I_{OUT2} = 28 \text{ mA},$                         |                     |      |      |      |      |

|                           | I <sub>OUT1</sub> at overcurrent detection level    |                     |      |      |      |      |

| Power dissipation 2       | $V_S = 18 \text{ V},$                               | Pdis2               |      |      | 0.75 | W    |

| $T_j \ge 125^{\circ}C$    | $I_{OUT1} = I_{OUT2} = 28 \text{ mA}$               |                     |      |      |      |      |

| Selective overtemperature | protection                                          |                     |      |      |      |      |

| Logic AND connected       | Switch off                                          | Temp_off            | 155  |      | 165  | °C   |

| with overcurrent detec-   | Switch on                                           | Temp_on             | 145  |      | 155  | °C   |

| tion (RETURNx, OUTx)      | Hysteresis                                          | Temp_hys            | 5    |      | 20   | °C   |

| Time delay until over-    | $V_S = 25 \text{ V}, T_{amb} = 125^{\circ}\text{C}$ | t <sub>del</sub>    | 100  |      |      | ms   |

| temperature shut-down     | OUT1 = OUT2 = GND                                   |                     |      |      |      |      |

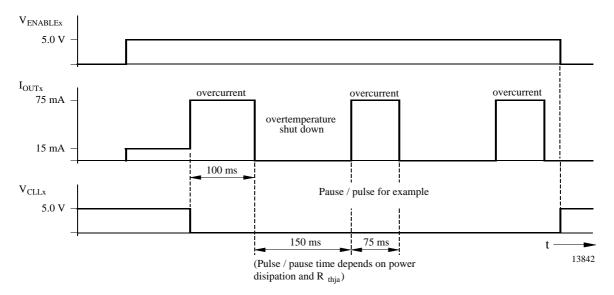

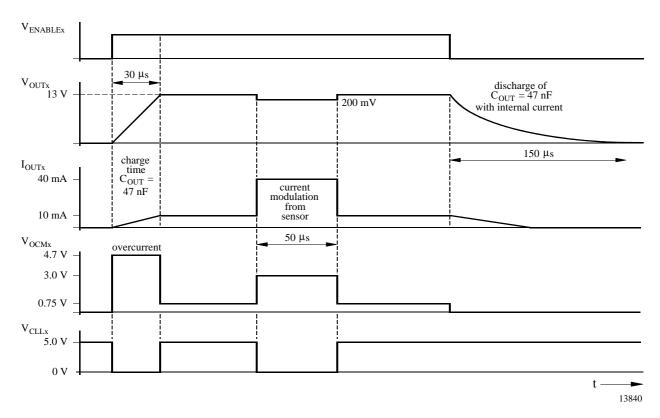

## **Timing Diagrams**

Figure 5. Variation of power supply

Figure 6. Overcurrent protection

Figure 7. Data transmission

# **Application Circuit**

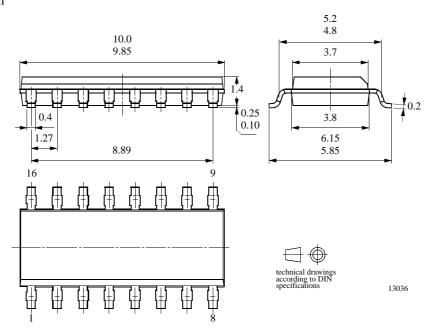

## **Package Information**

Package SO16 Dimensions in mm

# **U6268B**

## **Ozone Depleting Substances Policy Statement**

It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423