## **Phase Control Circuit for Industrial Applications**

#### Description

The UAA145 is a bipolar integrated circuit, designed to provide phase control for industrial applications. It permits the number of components in thyristor drive circuits to be drastically reduced. The versatility of the device is further enhanced by the provision of a large number of pins giving access to internal circuit points.

#### Features

- Separate pulse output synchronized by mains half wave

- Output pulse-width is freely adjustable

- Phase angle variable from  $>0^{\circ}$  to  $<180^{\circ}$

- High-impedance phase shift input

- Less than 3° pulse symmetry between two half-cycles or phase of different integrated circuits

- Output pulse blocking

#### Applications

- Industrial power control

- Silicon controlled rectifier

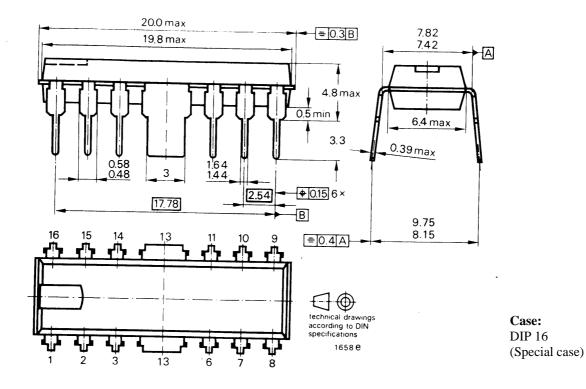

Package: DIP16 (special case)

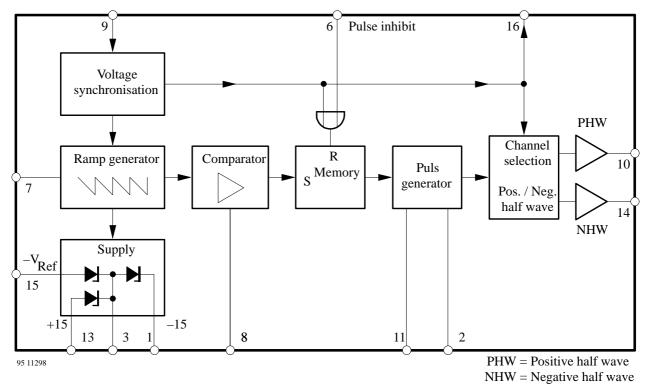

#### **Block Diagram**

Figure 1. Block diagram

#### **General Description**

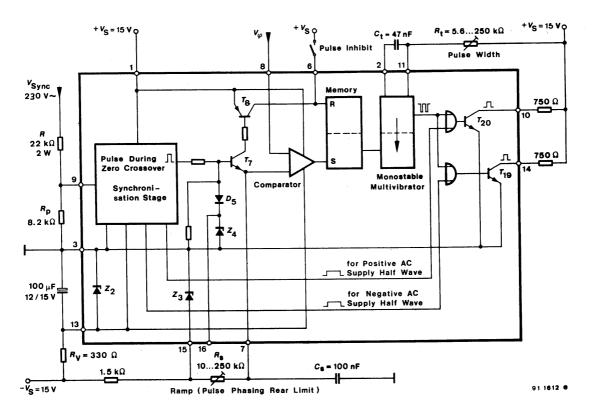

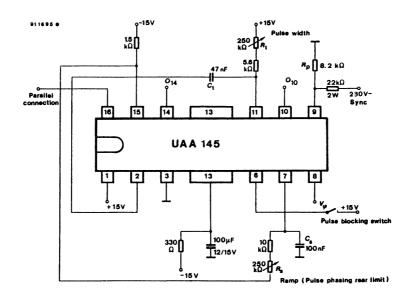

The operation of the circuit is best explained with the help of the block diagram shown in figure 1. It comprises a synchronizing stage, ramp generator, voltage com-parator, pulse generator, channel selecting stage and two output amplifiers. The circuit diagram in figure 2 also shows the external components and terminal connections necessary for operation of the circuit.

As can be seen from figure 2, the circuit requires two supply rails i.e. a + 15 V and a - 15 V. The positive voltage is applied directly to Pin 1, while an external series resistor in each line is used to connect the negative voltage Pin 13 and Pin 15. In the following circuit description each section of the block diagrams is discussed separately.

#### Synchronization Stage

Pin 9 is connected, via a voltage divider (22 k $\Omega$  and  $R_p$ ), to the ac line (sync. signal source). A pulse is generated during each zero crossover of the sync. input. The pulse duration depends on the resistance  $R_p$  and has a value of 50 to 100  $\mu$ s. (figure 2).

In addition to providing zero voltage switching pulses this section of the circuit generates blocking signals for use in the channel selecting stage.

#### **Ramp Generator**

Transistor T<sub>7</sub> amplifies the zero-crossover switching pulses. During the sync process capacitor C<sub>S</sub> at Pin 7 is charged to the operating voltage of reference diode Z<sub>4</sub>, i.e., to approximately 8.5 V, the charging time being always less than the duration of the sync pulse. The capacitor discharges via resistor R<sub>S</sub> during each half-cycle. The discharge voltage is of the same magnitude as the charge voltage, and is determined by Z<sub>3</sub>. To ensure an approximately linear ramp waveform, the voltage is allowed to decay up to ca. 0.7 C<sub>s</sub>R<sub>s</sub>. Because Z-diodes Z<sub>3</sub> and Z<sub>4</sub> have the same temperature characteristics, the timing of the ramp zero crossover point in relation to that of the sync. pulse is constant, and consequently the pulse phasing rear limit is also very stable.

Figure 2. Block diagram and basic circuit

#### **Comparator (Differential Amplifier) and Memory**

In the (voltage) comparator stage, the ramp voltage is compared with the shift voltage  $V_{\boldsymbol{\phi}}$  applied to Pin 8. The comparator switches whenever the instantaneous ramp voltage is the same as the shift voltage (corresponding to the desired phase angle), thereby causing the memory to be set, i.e. the integrated thyristor in memory is to be turned on. The time delay between the signal input and the comparator output signal is proportional to the required phase angle. Design of the circuit is such that the memory content is reset only during the instant of zero crossover, the reset signal always overriding the set signal. This effectively prevents the generation of additional output pulses and causes any pulse already started to be immediately inhibited on application of an inhibit signal to Pin 6. The memory content can also be reset via Pin 6. Thus the memory ensures that any noise (negative voltage transients) superimposed on the shift signal at Pin 8 cannot give rise to the generation of multiple pulses during the half-cycle.

#### Pulse Generator (Monostable Multivibrator)

The memory setting pulse also triggers a monostable stage. The duration of the pulse produced by the monostable is determined by  $C_t$  and  $R_t$ , connected to Pin 2 and Pin 11.

#### **Channel Selection and Output Amplifier**

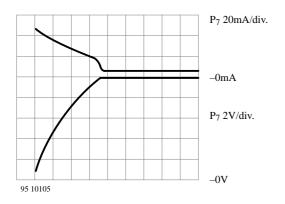

A pulse is produced at either output Pin 10 or Pin 14 if transistor  $T_{20}$  or  $T_{19}$  respectively is cut-off. The pulses derived from the pulse generator are applied to the output transistors via OR gates controlled by the half-cycle signals derived from the sync stage. During the positive half-cycle no signal is applied from the sync stage to  $T_{19}$ so that an output pulse is produced at Pin 14. The same is valid for Pin 10 during the negative half-cycle.

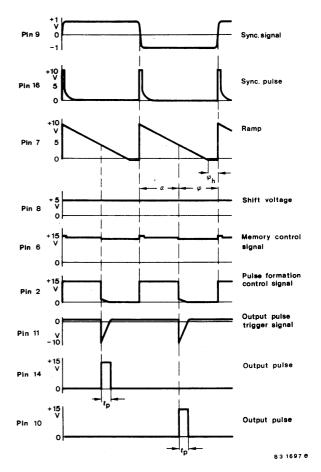

#### **Pulse Diagram**

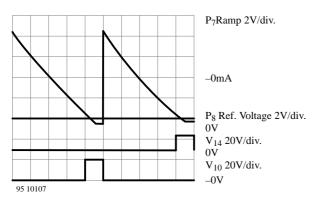

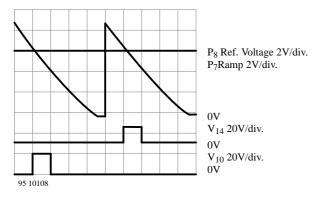

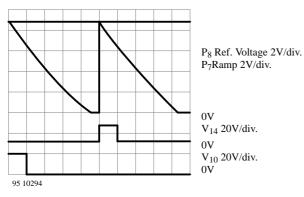

Figure 3 shows the pulse voltage waveforms measured at various points of the circuit, all signals being time referenced to the sync signal shown at the top. The input circuit limits any signal applied to  $\pm 0.8$  V at Pin 9. The sync pulse can be measured at Pin 16, whereas the ramp waveform and the pulse phasing rear limit ( $\phi_h$ ) are at Pin 7. The time relationship between the shift voltage applied to Pin 8 and the ramp waveform is indicated by dotted lines. A pulse trigger signal is produced whenever the ramp crosses the shift level. The memory control

pulse can be monitored by means of an oscilloscope applied to Pin 6. The Pin 11 pulse waveform is that at  $C_t$ , and the waveforms at Pin 10 and Pin 11 are those of the output pulses.

Figure 3. Pulse diagram

#### **Influence of External Components, Syncronization Time**

An ideal 0 to  $180^{\circ}$  shift range and perfect half-cycle pulse timing symmetry are attained, if the sync pulse duration is kept short. However, there is a lower pulse duration limit, which is governed by the time required to charge capacitor C<sub>s</sub> (figure 5).

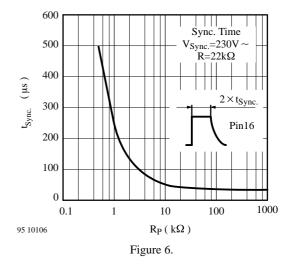

As can be seen, it takes about 35  $\mu$ s to charge C<sub>s</sub>. The sync time can be altered by adjustment of R<sub>p</sub>, the relationship between R<sub>p</sub> and the sync time being shown in figure 6. The ratio of R and R<sub>p</sub> determines the width of internal sync pulse, t<sub>sync</sub>, at Pin 16. The pulse shape is valid only for sync pulse of 230 V~. The lower the sync voltage, longer is the sync pulse.

A minimum of 50 µs (max. 200 µs) input sync pulse is required for a pulse symmetry of  $\Delta \phi \leq \pm 3^{\circ}$ .

# **UAA145**

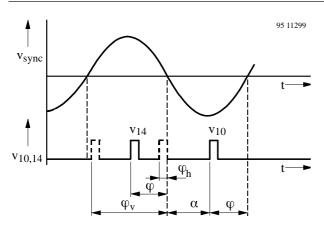

Figure 4. Pulse phasing

Figure 5. Charging time 10 µs/div.

#### **Pulse Phasing Limits**

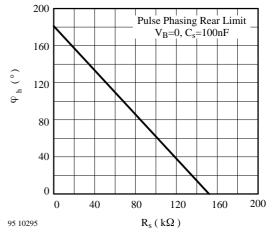

The pulse phasing front limit is determined by limiting the maximum shift voltage applied to Pin 8 which is thus adjustable by external circuitry. This can be done by connecting a Z-diode between Pin 8 and Pin 3. The pulse phasing rear limit,  $\phi_h$ , is the residual phase angle of the output pulses when the shift voltage  $V_{\phi}$  is zero. Since  $\phi_h$  coincides with the zero crossover point of the ramp, it can be adjusted by variation of the time constant  $C_s R_s$ (figure 14). Figure 10 shows the pulse phasing rear limit plotted as a function of  $R_s$ .

#### **Pulse Blocking**

The output pulses can be blocked via Pin 6, the memory content being erased whenever Pin 6 is connected to  $+V_S$  (Pin 1). This effectively de-activates the pulse generator; any output pulse in the process of generation is interrupted.

Pulse blocking can be accomplished either via relay contacts or a PNP switching transistor (figure 14).

Semiconductors

#### **Output Pulse Width**

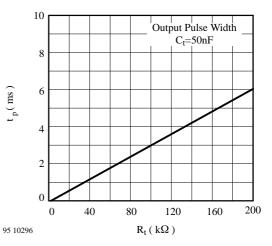

The output pulse width can be varied by adjustment of  $R_t$  and  $C_t$ . In figure 11 pulse width is shown plotted as a function of  $R_t$  for  $C_t = 50$  nF.

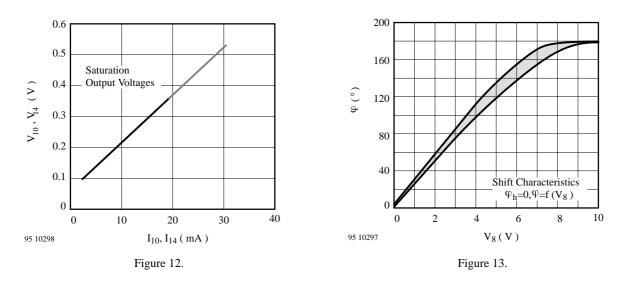

The output pulse always finishes at zero crossover. This means that if there is a minimum pulse width requirement (for example, when the load is inductive) provision must be made for a corresponding pulse phasing rear limit. The output stages are arranged so that the transistors are cut off when a pulse is produced. Consequently, the thyristor trigger pulse current flows via the external load resistors, this current being passed by the transistors during the period when no output pulse is produced. During this period the output voltage drops to the transistor saturation level and is therefore load dependent. Figure 12 shows the relationship between saturation voltage and load current.

#### **Shift Characteristic**

In figure 13 the angle of phase shift is shown plotted as a function of the voltage applied to Pin 8 for a pulse phasing rear limit of approximately  $0^{\circ}$ . Because the ramp waveform is a part of the exponential function, the shift curve is also exponential.

The limitation of the shift voltage to approximately 8.5 V is due to the internal Z-diode Z<sub>4</sub>, which has a voltage spread of 7 to 9 V.

The waveforms in figures 7 to 9 show the output pulse phase shift as a function of  $V_{\phi}$ . It can be seen from the oscillograms, the instants at which pulses are released coincide with the intersections of the ramp and the shift voltage.

Figure 7. Output pulses phase shift 2 ms/div

Figure 8. Output pulses phase shift 2 ms/div

Figure 9. Output pulses phase shift 2 ms/div

Figure 11.

# **UAA145**

TEMIC Semiconductors

#### **Absolute Maximum Ratings**

Reference point Pin 3,  $T_{amb} = 25^{\circ}C$ , unless otherwise specified

| Parameters                                         | Symbol           | Value                     | Unit                 |        |

|----------------------------------------------------|------------------|---------------------------|----------------------|--------|

| Positive supply voltage                            | Pin 1            | Vs                        | 18                   | V      |

| Shift voltage                                      | Pin 8            | $V_{\phi}$<br>$-V_{\phi}$ | V <sub>S1</sub><br>5 | V<br>V |

| Reverse voltage, control input                     | Pin 11           | -V <sub>IR</sub>          | 15                   | V      |

| Negative supply current                            | Pin 13<br>Pin 15 | -I <sub>S</sub>           | 25<br>5              | mA     |

| Synchronization current                            | Pin 9            | ± I <sub>sync</sub>       | 20                   | mA     |

| Control input pulse current                        | Pin 11           | II                        | 3                    | mA     |

| Output currents                                    | Pin 10<br>Pin14  | I <sub>O</sub>            | 20<br>20             | mA     |

| Total power dissipation<br>Tamb $\leq 70^{\circ}C$ |                  | P <sub>tot</sub>          | 550                  | mW     |

| Junction temperature                               |                  | Tj                        | 125                  | °C     |

| Ambient temperature range                          |                  | T <sub>amb</sub>          | -25 to +70           | °C     |

| Storage temperature range                          |                  | T <sub>stg</sub>          | -25 to +125          | °C     |

#### **Thermal Resistance**

| Parameters       | Symbol            | Value | Unit |

|------------------|-------------------|-------|------|

| Junction ambient | R <sub>thJA</sub> | 100   | K/W  |

| Junction case    | R <sub>thJC</sub> | 35    |      |

### TEMIC Semiconductors

#### **DC** Characteristics

| Parameters                              | Test Conditions / Pin                                                                                         |               | Symbol                               | Min.       | Тур. | Max.       | Unit |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------|------------|------|------------|------|

| Positive supply current                 | V <sub>S</sub> = 16 V                                                                                         | Pin 1         | IS                                   | 12         |      | 30         | mA   |

| Voltage limitation                      | $-I_{S13} = 15 \text{ mA}$<br>$-I_{S15} = 3.5 \text{ mA}$                                                     | Pin 15        | -V <sub>Z2</sub><br>-V <sub>Z3</sub> | 7.0<br>7.0 |      | 9.0<br>9.0 | V    |

|                                         | $V_{\rm S} = 13  {\rm V},  {\rm V}_9 = 0  {\rm V}$                                                            |               | V <sub>Z4</sub>                      | 7.0        |      | 9.0        |      |

| Input current                           |                                                                                                               | Pin 8<br>nA   | Ι <sub>φ</sub>                       |            |      | 10         | μΑ   |

| C <sub>t</sub> -potential shift current | $V_{S} = V_{12} = 13 \text{ V}, \\ V_{I7} = 3 \text{ V}, I_{\phi 8} = 5 \text{ V}, \\ I_{9} = 0.3 \text{ mA}$ |               | II                                   | 4.5        |      |            | mA   |

| C <sub>t</sub> -charging current        |                                                                                                               | Pin 2<br>1 ms | -II                                  | 10         |      | 30         | mA   |

| C <sub>S</sub> -charging current        |                                                                                                               |               | -II                                  | 20         |      | 62         | mA   |

| Output saturation voltage               |                                                                                                               | Pin 10        | V <sub>Osat</sub>                    |            | 0.3  | 1.0        | V    |

|                                         | $I_{14} = 20 \text{ mA},$<br>$I_9 = 0.3 \text{ mA}$                                                           | Pin 14        | V <sub>Osat</sub>                    |            | 0.3  | 1.0        |      |

$V_{S1} = 13$  to 16 V,  $-I_{S13} = 15$  mA, reference point Pin 3, figure 2,  $T_{amb} = 25^{\circ}$ C, unless otherwise specified

#### **AC Characteristics**

$T_{amb}$ = 25°C, figures 2, 4 and 14

| Parameters                | Test Conditions / Pin |        | Symbol         | Min. | Type. | Max. | Unit |

|---------------------------|-----------------------|--------|----------------|------|-------|------|------|

| Rise time                 |                       | Pin 10 | t <sub>r</sub> |      |       | 0.5  | μs   |

|                           |                       | Pin 14 |                |      |       | 0.5  |      |

| Pulse width               | figure 11             | Pin 10 | tp             | 0.1  |       | 4    | ms   |

|                           |                       | Pin 14 | tp             | 0.1  |       | 4    |      |

| Pulse phasing difference  | f = 50 Hz             |        | Δφ             |      |       | ± 3  | 0    |

| for two half-waves        |                       |        |                |      |       |      |      |

| Inter IC phasing          | f = 50 Hz             |        | Δφ             |      |       | ± 3  | 0    |

| difference                |                       |        |                |      |       |      |      |

| Pulse phasing front limit | f = 50 Hz, figure 4   |        | $\phi_v$       | 177  |       |      | 0    |

| Pulse phasing rear limit  | f = 50 Hz, figures 4  | and 10 | $\phi_h$       |      |       | 0    | 0    |

Angle of current flow  $\phi=0$  to 177° at  $V_{\phi8}$  = 0.2 to 7.5 V,  $\phi_h$  = 0°, figures 4 and 13

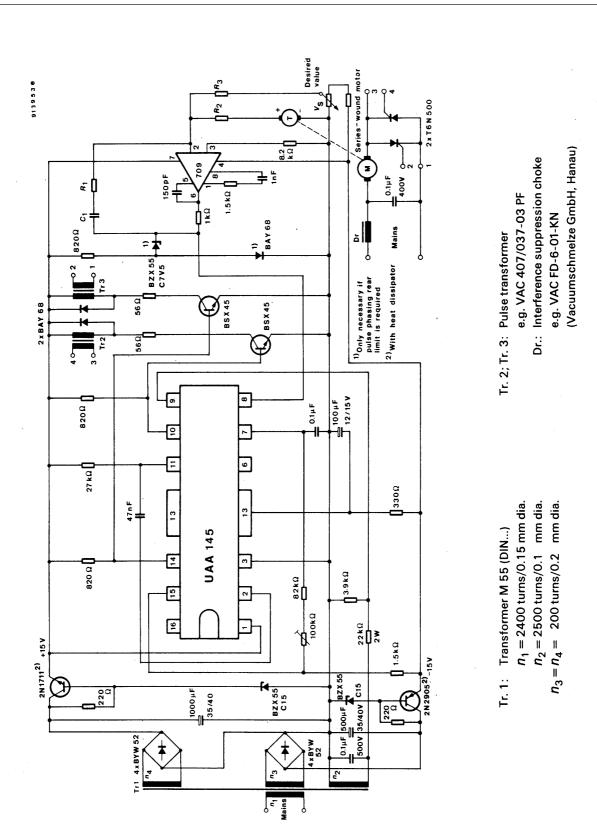

Figure 14. Test circuit for ac characteristics

#### Applications

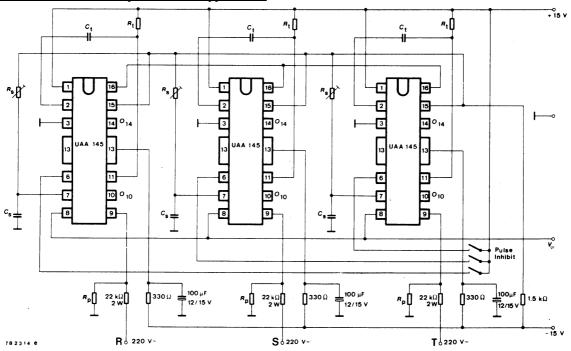

Parallel connection for three-phase current applications

Figure 15. Parallel connection for three-phase current applications. For polyphase operation connect all Pins 15 and Pins 16.

To ensure good pulse phasing symmetry as well as identical shift characteristics in three-phase applications, when three devices are employed, two parallel connection pins (figure 15) are provided on each device. Besides the supply pins, the input pins 15 and 16 are to be paralleled. If this is done, then all the  $Z_4$  and  $Z_3$  diodes are connected in parallel so that the reference voltage

effective for all three devices becomes that of the Z-diode with the lowest operating voltage. In this way all the  $C_S$  capacitors are charged and discharged to the same voltage levels. By symmetrical adjustment of the time constants with resistors  $R_S$ , good pulse phasing symmetry and identical shift characteristics are attained.

Figure 16. Speed control with tacho-generator

EMIC

Semiconductors

### **Dimensions in mm**

#### **Ozone Depleting Substances Policy Statement**

It is the policy of **TEMIC TELEFUNKEN microelectronic GmbH** to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice. Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423