# MOS INTEGRATED CIRCUIT $\mu$ PD78P9014

# 8-bit Single-Chip Microcontroller

$\mu$ PD78P9014 is a product in the  $\mu$ PD789014 Subseries of compact, general-purpose microcontrollers in the 78K/ 0S Series.

In addition to an 8-bit CPU, this product has substantial hardware such as on-chip I/O ports, timers, serial interface, and interrupt controls.

This PROM product incorporates one-time PROM that can be written only once.

Since user can write programs, this microcontroller is best suited for evaluation during development, multi-product small-volume production, and rapid start up.

These user's manuals contain detailed descriptions of the functions. Be sure to read them before designing.

# $\mu\text{PD78P9014}$ Subseries User's Manual: U11187E 78K/0S Series User's Manual - Instruction: U11047E

#### FEATURES

- Pin compatible with mask ROM products (except for the VPP pin)

- On-chip one-time PROM: 8K bytes

- On-chip high-speed RAM: 256 bytes

- Can change the minimum instruction execution time to the fast speed (0.4  $\mu$ s) and the low speed (1.6  $\mu$ s)

- I/O ports: 22

- Serial interface: 1 channel

Can select the three-wire serial I/O mode or the UART mode

- Timers: 3 channels

- 8-bit timer/event counter: 2 channels

- Watchdog timer: 1 channel

- Operation possible at the same power supply voltage as in mask ROM products (VDD = 1.8 to 5.5 V)

- Compatible with the QTOP<sup>TM</sup> microcontroller

**Remarks** QTOP microcontroller is the name of the on-chip one-time PROM microcontroller fully supported by the NEC write service (sealing from the write, screening, inspection).

#### **APPLICATION FIELDS**

Compact household appliances, remote controls, games, etc.

#### **ORDERING INFORMATION**

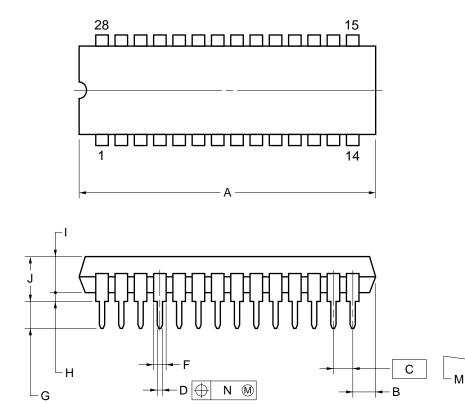

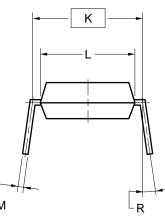

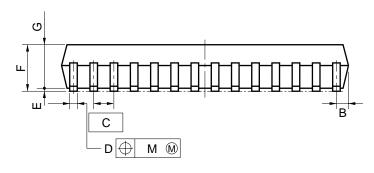

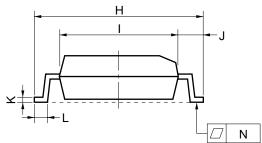

| Part N | umber   | Package                              |

|--------|---------|--------------------------------------|

| μPD78  | P9014CT | 28-pin plastic shrink DIP (400 mils) |

| μPD78  | P9014GT | 28-pin plastic SOP (375 mils)        |

The information in this document is subject to change without notice.

# OVERVIEW OF THE FEATURES

| Item                          |                | Function                                                                                        |  |  |

|-------------------------------|----------------|-------------------------------------------------------------------------------------------------|--|--|

| On-chip memory                | One-time PROM  | 8K bytes                                                                                        |  |  |

|                               | High-speed RAM | 256 bytes                                                                                       |  |  |

| General-purpose registers     |                | 8 bits × 8 registers                                                                            |  |  |

| Minimum instruction execu     | ition time     | 0.4 $\mu$ s or 1.6 $\mu$ s (main system clock: 5.0 MHz operation)                               |  |  |

| Instruction set               |                | <ul><li>16-bit calculations</li><li>Bit manipulation (set, reset, test)</li></ul>               |  |  |

| I/O ports                     |                | CMOS I/O: 22                                                                                    |  |  |

| Serial interface              |                | Can select the three-wire serial I/O mode or the UART mode: 1 channel                           |  |  |

| Timers                        |                | <ul><li> 8-bit timer/event counter: 2 channels</li><li>Watchdog timer: 1 channel</li></ul>      |  |  |

| Timer output                  |                | 2                                                                                               |  |  |

| Vector interrupt source       | Maskable       | Internal: 6, External: 3                                                                        |  |  |

|                               | Nonmaskable    | Internal: 1                                                                                     |  |  |

| Power supply voltage          |                | V <sub>DD</sub> = 1.8 to 5.5 V                                                                  |  |  |

| Ambient operating temperature |                | $T_{A} = -40 \text{ to } +85^{\circ}\text{C}$                                                   |  |  |

| Package                       |                | <ul> <li>28-pin plastic shrink DIP (400 mils)</li> <li>28-pin plastic SOP (375 mils)</li> </ul> |  |  |

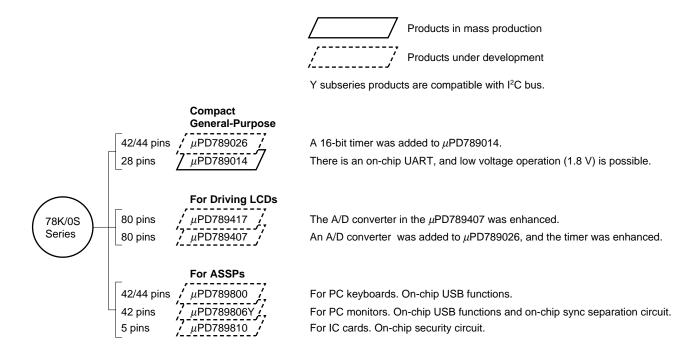

#### 78K/0S Series Expansion

The following shows the 78K/0S Series products development. Subseries names are shown inside frames.

The following lists the main functional differences between subseries products.

| Subseries            | Function   | ROM      |       | Timers |       |     | 8-bit | 10-bit | 8-bit | Serial Interface                           | 1/0 | Minimum         |

|----------------------|------------|----------|-------|--------|-------|-----|-------|--------|-------|--------------------------------------------|-----|-----------------|

| Name                 |            | Capacity | 8-bit | 16-bit | Watch | WDT | A/D   | A/D    | D/A   | Ochar Interface                            | 1/0 | V <sub>DD</sub> |

| Compact,<br>general- | μPD789026  | 4K-16K   | 1ch   | 1ch    | -     | 1ch | -     | -      | -     | 1ch (UART :1 ch)                           | 34  | 1.8 V           |

| purpose              | μPD789014  | 2K-4K    | 2ch   | _      |       |     |       |        |       |                                            | 22  |                 |

| For LCD              | μPD789417  | 12K-24K  | 3ch   | 1ch    | 1ch   | 1ch | -     | 7ch    | -     | 1ch (UART : 1ch)                           | 43  | 1.8 V           |

| driving              | μPD789407  | 12K-24K  |       |        |       |     | 7ch   | _      |       |                                            |     |                 |

| For ASSP             | μPD789800  | 8K       | 2ch   | _      | -     | 1ch | -     | _      | -     | 2ch (USB : 1ch)                            | 31  | 4.0 V           |

|                      | μPD789806Y | 16K      | 2ch   | _      | -     | 1ch | _     | I      | -     | 2ch (USB : 1ch,<br>I <sup>2</sup> C : 1ch) | 20  | 4.5 V           |

|                      | μPD789810  | 6K       | -     | _      | -     | 1ch | -     | -      | -     | _                                          | 1   | 1.8 V           |

#### CONTENTS

- 1. PIN CONNECTION DIAGRAM (Top View) ... 5

- 2. BLOCK DIAGRAM ... 7

- 3. DIFFERENCES BETWEEN THE  $\mu$ PD78P9014 AND MASK ROM PRODUCTS ... 8

- 4. PIN FUNCTION LIST ... 9

- 4.1 Pins in the Normal Operating Mode ... 9

- 4.2 Pins in the PROM Programming Mode ... 10

- 4.3 Pin I/O Circuit and Unused Pin Connections ... 11

- 5. MEMORY SPACE ... 12

- 6. OVERVIEW OF THE INSTRUCTION SET ... 13

- 6.1 Legend ... 13

- 6.2 Operation List ... 15

- 7. PROM PROGRAMMING ... 20

- 7.1 Operating Modes ... 20

- 7.2 PROM writing procedure ... 21

- 7.3 PROM reading procedure ... 22

- 7.4 One-Time PROM Product Screening ... 23

- **\* 8. ELECTRICAL SPECIFICATIONS** ... 24

- \* 9. CHARACTERISTIC CURVES (REFERENCE VALUES) ... 39

- 10. PACKAGE DRAWINGS ... 40

- **\*** 11. RECOMMENDED SOLDERING CONDITIONS ... 42

APPENDIX A. DEVELOPMENT TOOLS ... 43

APPENDIX B. RELATED DOCUMENTS ... 44

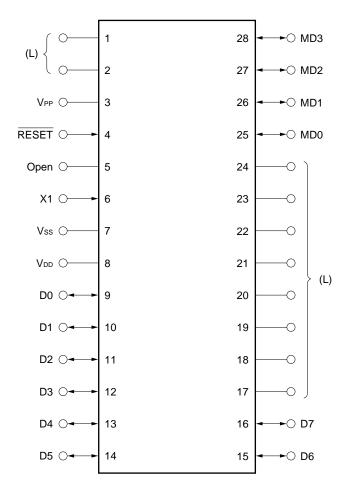

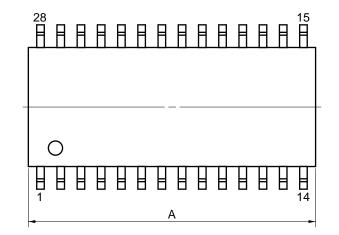

- 1. PIN CONNECTION DIAGRAM (Top View)

- (1) Normal operating modes

- 28-pin plastic shrink DIP (400 mils) μPD78P9014CT

- 28-pin plastic SOP (375 mils) μPD78P9014GT

#### Caution Directly connect VPP to Vss.

| ASCK        | : Asynchronous Serial Clock  | SI0      | : Serial Input             |

|-------------|------------------------------|----------|----------------------------|

| INTP0-INTP2 | : Interrupt from Peripherals | SO0      | : Serial Output            |

| P00-P07     | : Port0                      | TIO, TI1 | : Timer Input              |

| P10-P17     | : Port1                      | TO0, TO1 | : Timer Output             |

| P20-P22     | : Port2                      | TxD      | : Transmit Data            |

| P30-P32     | : Port3                      | Vdd      | : Power Supply             |

| RESET       | : Reset                      | Vpp      | : Programming Power Supply |

| RxD         | : Receive Data               | Vss      | : Ground                   |

| SCK0        | : Serial Clock               | X1, X2   | : Crystal                  |

- (2) PROM programming mode

- 28-pin plastic shrink DIP (400 mils) μPD78P9014CT

- 28-pin plastic SOP (375 mils) μPD78P9014GT

#### Cautions 1. (L) : Individually connect to Vss via a pull-down resistor.

- 2. Vss : Connect to ground.

- 3.  $\overline{\text{RESET}}$  : Set to the low level.

- 4. Open : Leave open.

| D0-D7   | : Data Bus                | Vdd | : Power Supply             |

|---------|---------------------------|-----|----------------------------|

| MD0-MD3 | : Programming Mode Select | Vpp | : Programming Power Supply |

| RESET   | : Reset                   | Vss | : Ground                   |

|         |                           | X1  | : Programming Clock Input  |

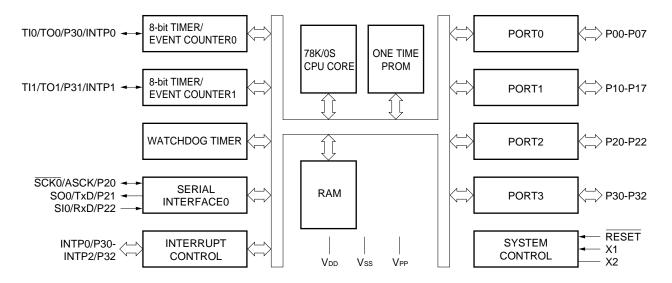

## 2. BLOCK DIAGRAM

#### 3. DIFFERENCES BETWEEN THE $\mu \text{PD78P9014}$ AND MASK ROM PRODUCTS

$\mu$ PD78P9014 is a product with an on-chip one-time PROM that can only be written once. Table 3-1 lists the differences between the  $\mu$ PD78P9014 and mask ROM products.

#### Table 3-1. Differences Between the $\mu$ PD78P9014 and Mask ROM Products

| Item           |                | One-Time PROM Product | Mask ROM Products |           |  |

|----------------|----------------|-----------------------|-------------------|-----------|--|

|                | eni            | μPD78P9014            | μPD789011         | μPD789012 |  |

| On-chip memory | ROM            | 8K bytes              | 2K bytes          | 4K bytes  |  |

|                | High-speed RAM | 256 bytes             | 128 bytes         |           |  |

# 4. PIN FUNCTION LIST

# 4.1 Pins in the Normal Operating Mode

# (1) Port pins

| Pin Name | I/O | Function                                                                                                                                                                          | On Reset | Alternate Function Pin |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------|

| P00-P07  | I/O | Port 0<br>8-bit I/O port<br>Input/output specifiable bit-wise<br>When used as an input port, on-chip pull-up resistor can be used<br>by software.<br>LEDs can be directly driven. | Input    | -                      |

| P10-P17  | I/O | Port 1<br>8-bit I/O port<br>Input/output specifiable bit-wise<br>When used as an input port, on-chip pull-up resistor can be used<br>by software.<br>LEDs can be directly driven. | Input    | _                      |

| P20      | I/O | Port 2<br>3-bit I/O port                                                                                                                                                          | Input    | ASCK/SCK0              |

| P21      |     | Input/output specifiable bit-wise<br>When used as an input port, on-chip pull-up resistor can be used                                                                             |          | TxD/SO0                |

| P22      |     | by software.<br>LEDs can be directly driven.                                                                                                                                      |          | RxD/SI0                |

| P30      | I/O | Port 3<br>3-bit I/O port                                                                                                                                                          | Input    | INTP0/TI0/TO0          |

| P31      |     | Input/output specifiable bit-wise<br>When used as an input port, on-chip pull-up resistor can be used                                                                             |          | INTP1/TI1/TO1          |

| P32      |     | by software.<br>LEDs can be directly driven.                                                                                                                                      |          | INTP2                  |

# (2) Pins not in the ports

| Pin Name              | I/O    | Function                                                                                                                     | On Reset | Alternate Function Pin |

|-----------------------|--------|------------------------------------------------------------------------------------------------------------------------------|----------|------------------------|

| INTP0 <sup>Note</sup> | Input  | External interrupt input whose valid edge can be specified (rising                                                           |          | P30/TI0/TO0            |

| INTP1 <sup>Note</sup> |        | edge, falling edge, or both the rising and falling edges)                                                                    |          | P31/TI1/TO1            |

| INTP2 <sup>Note</sup> |        |                                                                                                                              |          | P32                    |

| SI0 <sup>Note</sup>   | Input  | Serial data input in the serial interface                                                                                    | Input    | P22/RxD                |

| SO0                   | Output | Serial data output in the serial interface                                                                                   | Input    | P21/TxD                |

| SCK0Note              | I/O    | Serial clock I/O for the serial interface                                                                                    | Input    | P20/ASCK               |

| RxD <sup>Note</sup>   | Input  | Serial data input for the asynchronous serial interface                                                                      | Input    | P22/SI0                |

| TxD                   | Output | Serial data output for the asynchronous serial interface                                                                     | Input    | P21/SO0                |

| ASCK <sup>Note</sup>  | Input  | Serial clock input for the asynchronous serial interface                                                                     | Input    | P20/SCK0               |

| TI0 <sup>Note</sup>   | Input  | External count clock input to the 8-bit timer (TM0)                                                                          |          | P30/INTP0/TO0          |

| TI1 Note              |        | External count clock input to the 8-bit timer (TM1)                                                                          |          | P31/INTP1/TO1          |

| ТО0                   | Output | 8-bit timer output                                                                                                           | Input    | P30/INTP0/TI0          |

| TO1                   |        |                                                                                                                              |          | P31/INTP1/TI1          |

| RESET                 | Input  | System reset input                                                                                                           | Input    | _                      |

| X1                    | Input  | Crystal connection for the main system clock oscillation                                                                     | -        | -                      |

| X2                    | -      |                                                                                                                              | -        | _                      |

| Vdd                   | -      | Positive power supply                                                                                                        | _        | _                      |

| Vpp                   | _      | High voltage applied when writing or verifying programs.<br>In the normal operating mode, this is directly connected to Vss. | _        | -                      |

| Vss                   | -      | Ground potential                                                                                                             | -        | _                      |

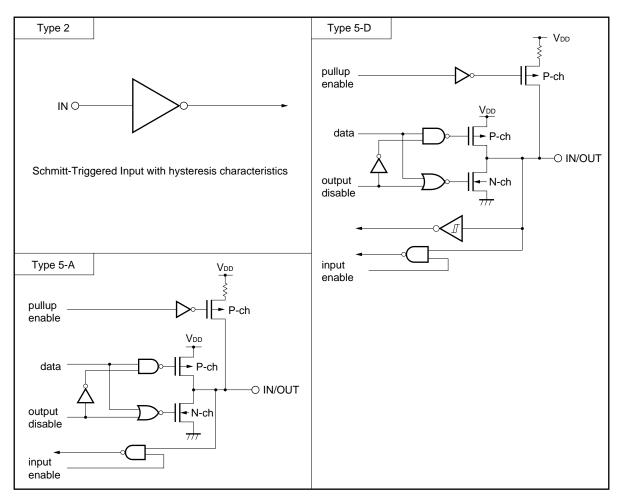

\* Note These pins are input through Schmitt triggers. (See Type 5-D in Figure 4-1, "Pin I/O Circuit Types.")

# 4.2 Pins in the PROM Programming Mode

|   | Pin Name | I/O   | Function                                                                                                           |

|---|----------|-------|--------------------------------------------------------------------------------------------------------------------|

|   | RESET    | Input | Connect to Vss.                                                                                                    |

|   | Vpp      | Input | High voltage applied when setting the PROM programming mode and when writing a program or verifying.               |

| * |          |       | If +5.5 V is applied to the V_DD pin and +12.5 V is applied to the V_PP pin, the PROM programming mode is entered. |

|   | MD0-MD3  | I/O   | Select the operating mode when in the PROM programming mode.                                                       |

|   | D0-D7    | I/O   | Data bus                                                                                                           |

|   | X1       | Input | Clock input for address updating in the PROM programming mode                                                      |

|   | Vdd      | -     | PROM programming mode setting and the positive power supply                                                        |

|   | Vss      | -     | Ground potential                                                                                                   |

# 4.3 Pin I/O Circuit and Unused Pin Connections

Table 4-1 shows the types of the I/O circuits of each pin and the connections for unused pins. See Figure 4-1 for the structure of each type of I/O circuit.

| Pin Name          | I/O Circuit Type | I/O | Recommended Connection for Unused Pin              |

|-------------------|------------------|-----|----------------------------------------------------|

| P00-P07           | 5-A              | I/O | Connect to VDD or VSS through a separate resistor. |

| P10-P17           |                  |     |                                                    |

| P20/ASCK/SCK0     | 5-D              |     |                                                    |

| P21/TxD/SO0       | 5-A              | ]   |                                                    |

| P22/RxD/SI0       | 5-D              | 1   |                                                    |

| P30/INTP0/TI0/TO0 |                  |     | Connect to Vss through a separate resistor.        |

| P31/INTP1/TI1/TO1 |                  |     |                                                    |

| P32/INTP2         |                  |     |                                                    |

| RESET             | 2                | -   | -                                                  |

| Vpp               | _                | -   | Connect directly to Vss.                           |

Table 4-1. Types of Pin I/O Circuits

#### Figure 4-1. Summary of the Pin I/O Circuits

## 5. MEMORY SPACE

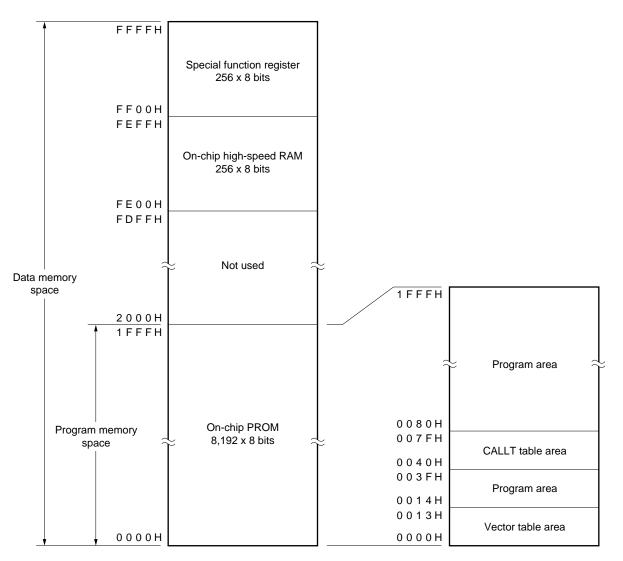

Figure 5-1 shows the  $\mu$ PD78P9014 memory map.

#### 6. OVERVIEW OF THE INSTRUCTION SET

The  $\mu$ PD78P9014 instruction set is shown in the table below.

#### 6.1 Legend

#### 6.1.1 Operand identifiers and methods of use

Operands are described in "Operand" column of each instruction in accordance with the description method of the instruction operand identifier (refer to the assembler specifications for detail). When there are two or more description methods, select one of them. Alphabetic letters in capitals and symbols, #, !, \$, and [] are keywords and must be described as they are. Each symbol has the following meaning.

| <ul> <li># : Immediate data specification</li> </ul> | • \$ | : Relative address specification |

|------------------------------------------------------|------|----------------------------------|

|------------------------------------------------------|------|----------------------------------|

- ! : Absolute address specification •

- [ ] : Indirect address specification

In the case of immediate data, describe an appropriate numeric value or a label. When using a label, Be sure to describe the #, !, \$, and [ ] symbols.

For operand register identifiers, r and rp, either function names (X, A, C, etc.) or absolute names (names in parentheses in the table below, R0, R1, R2, etc.) can be used for description.

| Identifier | Description Method                                             |

|------------|----------------------------------------------------------------|

| r          | X (R0), A (R1), C (R2), B (R3), E (R4), D (R5), L (R6), H (R7) |

| rp         | AX (RP0), BC (RP1), DE (RP2), HL (RP3)                         |

| sfr        | Special-function register symbol                               |

| saddr      | FE20H-FF1FH Immediate data or labels                           |

| saddrp     | FE20H-FF1FH Immediate data or labels (even addresses only)     |

| addr16     | 0000H-FFFFH Immediate data or labels                           |

|            | (Only even addresses in a 16-bit data transfer instructions)   |

| addr5      | 0040H-007FH Immediate data or labels (even addresses only)     |

| word       | 16-bit immediate data or label                                 |

| byte       | 8-bit immediate data or label                                  |

| bit        | 3-bit immediate data or label                                  |

#### Table 6-1. Operand Identifiers and Description Methods

#### 6.1.2 Description of "Operation" column

- A : A register ; 8-bit accumulator

- Х : X register В : B register С : C register D : D register Е : E register Н : H register L : L register : AX register pair; 16-bit accumulator AX BC : BC register pair

- DE : DE register pair

- HL : HL register pair

- PC : Program counter

- SP : Stack pointer

- PSW : Program status word

- CY : Carry flag

- AC : Auxiliary carry flag

- Z : Zero flag

- IE : Interrupt request enable flag

- NMIS : Non-maskable interrupt servicing flag

- ( ) : Memory contents indicated by the address or register contents in parentheses

- $X_{H},\,X_{L}$   $\ : \ High \ 8 \ bits \ and \ low \ 8 \ bits \ of \ a \ 16-bit \ register$

- ∧ : Logical product (AND)

- ∨ : Logical sum (OR)

- $\forall$  : Exclusive logical sum (exclusive OR)

- ----- : Inverted data

- addr16 : 16-bit immediate data or label

- jdisp8 : signed 8-bit data (displacement value)

#### 6.1.3 Description of "Flag Operation" column

- (Blank) : Unchanged 0 : Clear to 0.

- 1 : Set to 1.

- × : Set/cleared according to the result

- R : Previously saved value is restored.

\*

# 6.2 Operation List

| Mnemonic | Operand        | Bytes | Clock | Operation                       |   | Flag |    |

|----------|----------------|-------|-------|---------------------------------|---|------|----|

|          |                | -     |       |                                 | Z | AC   | CY |

| MOV      | r, #byte       | 3     | 6     | r ← byte                        |   |      |    |

|          | saddr, #byte   | 3     | 6     | (saddr) ← byte                  |   |      |    |

|          | sfr, #byte     | 3     | 6     | $sfr \leftarrow byte$           | _ |      |    |

|          | A, r Note 1    | 2     | 4     | $A \leftarrow r$                |   |      |    |

|          | r, A Note 1    | 2     | 4     | $r \leftarrow A$                | _ |      |    |

|          | A, saddr       | 2     | 4     | $A \leftarrow (saddr)$          |   |      |    |

|          | saddr, A       | 2     | 4     | (saddr) ← A                     |   |      | -  |

|          | A, sfr         | 2     | 4     | $A \leftarrow sfr$              |   |      |    |

|          | sfr, A         | 2     | 4     | $sfr \leftarrow A$              |   |      |    |

|          | A, !addr16     | 3     | 8     | $A \leftarrow (addr16)$         |   |      |    |

|          | !addr16, A     | 3     | 8     | $(addr16) \leftarrow A$         |   |      |    |

|          | PSW, #byte     | 3     | 6     | $PSW \leftarrow byte$           | × | ×    | ×  |

|          | A, PSW         | 2     | 4     | $A \leftarrow PSW$              |   |      |    |

|          | PSW, A         | 2     | 4     | $PSW \leftarrow A$              | × | ×    | ×  |

|          | A, [DE]        | 1     | 6     | $A \leftarrow (DE)$             |   |      |    |

|          | [DE], A        | 1     | 6     | $(DE) \leftarrow A$             |   |      |    |

|          | A, [HL]        | 1     | 6     | $A \leftarrow (HL)$             |   |      |    |

|          | [HL], A        | 1     | 6     | $(HL) \leftarrow A$             |   |      |    |

|          | A, [HL + byte] | 2     | 6     | $A \leftarrow (HL + byte)$      |   |      |    |

|          | [HL + byte], A | 2     | 6     | (HL + byte) ← A                 |   |      |    |

| ХСН      | Α, Χ           | 1     | 4     | $A \leftrightarrow X$           |   |      |    |

|          | A, r Note 2    | 2     | 6     | $A \leftrightarrow r$           |   |      |    |

|          | A, saddr       | 2     | 6     | $A \leftrightarrow (saddr)$     |   |      |    |

|          | A, sfr         | 2     | 6     | $A \leftrightarrow (sfr)$       |   |      |    |

|          | A, [DE]        | 1     | 8     | $A \leftrightarrow (DE)$        |   |      |    |

|          | A, [HL]        | 1     | 8     | $A \leftrightarrow (HL)$        |   |      |    |

|          | A, [HL + byte] | 2     | 8     | $A \leftrightarrow (HL + byte)$ |   |      |    |

| MOVW     | rp, #word      | 3     | 6     | $rp \leftarrow word$            |   |      |    |

|          | AX, saddrp     | 2     | 6     | $AX \leftarrow (saddrp)$        |   |      |    |

|          | saddrp, AX     | 2     | 8     | $(saddrp) \leftarrow AX$        |   |      |    |

|          | AX, rp Note 3  | 1     | 4     | AX ← rp                         |   |      |    |

|          | rp, AX Note 3  | 1     | 4     | $rp \leftarrow AX$              |   |      |    |

| XCHW     | AX, rp Note 3  | 1     | 8     | $AX \leftrightarrow rp$         |   |      |    |

#### Notes 1. Except r = A

- 2. Except r = A or X

- **3.** Only when rp = BC, DE, or HL

**Remark** One instruction clock cycle is one cycle of the CPU clock (fcPU) selected by the processor clock control register (PCC).

| Mnemonic | Operand                                                                                       | Bytes | Clock | Operation                                                                |   | Flag    |      |

|----------|-----------------------------------------------------------------------------------------------|-------|-------|--------------------------------------------------------------------------|---|---------|------|

| ADD      | A, #byte                                                                                      | 2     | 4     | A, CY $\leftarrow$ A + byte                                              | Z | AC<br>× | × CY |

|          | saddr, #byte                                                                                  | 3     | 6     | (saddr), CY $\leftarrow$ (saddr) + byte                                  | × | ×       | ×    |

|          | A, r                                                                                          | 2     | 4     | $A, CY \leftarrow A + r$                                                 | × | ×       | X    |

|          | A, saddr                                                                                      | 2     | 4     | $A, CY \leftarrow A + (saddr)$                                           | × | ×       | ×    |

|          | A, !addr16                                                                                    | 3     | 8     | $A, CY \leftarrow A + (addr)$                                            |   | ×       | ×    |

|          | A, [HL]                                                                                       | 1     | 6     | $A, CY \leftarrow A + (HL)$                                              | × | ×       | ×    |

|          | A, [HL + byte]                                                                                | 2     | 6     | $A, CY \leftarrow A + (HL + byte)$                                       | × | ×       | ×    |

| ADDC     | A, #byte                                                                                      | 2     | 4     | $A, CY \leftarrow A + byte + CY$                                         | × | ×       | ×    |

| ADDO     | saddr, #byte                                                                                  | 3     | 6     | (saddr), $CY \leftarrow$ (saddr) + byte + $CY$                           | × | ×       | ×    |

|          | Saddi, #byteS6(Saddi), C1 $\leftarrow$ (Saddi) + byte + C1A, r24A, CY $\leftarrow$ A + r + CY |       | ×     | ×                                                                        | × |         |      |

|          | A, saddr                                                                                      | 2     | 4     | $A, CY \leftarrow A + (saddr) + CY$                                      | × | ×       | ×    |

|          | A, !addr16                                                                                    | 3     | 8     | $A, CY \leftarrow A + (add1) + CY$                                       | × | ×       | ×    |

|          | A, [HL]                                                                                       | 1     | 6     | $A, CY \leftarrow A + (HL) + CY$                                         | × | ×       | ×    |

|          | A, [HL + byte]                                                                                | 2     | 6     | $A, CY \leftarrow A + (HL) + CY$ $A, CY \leftarrow A + (HL + byte) + CY$ | × | ×       | ×    |

| SUB      | A, #byte                                                                                      | 2     | 4     | A, $CY \leftarrow A - byte$                                              | × | ×       | ×    |

| 000      | saddr, #byte                                                                                  | 3     | 6     | (saddr), $CY \leftarrow$ (saddr) – byte                                  | × | ×       | ×    |

|          | A, r                                                                                          | 2     | 4     | A, $CY \leftarrow A - r$                                                 | × | ×       | ×    |

|          | A, saddr                                                                                      | 2     | 4     | $A, CY \leftarrow A - (saddr)$                                           | × | ×       | ×    |

|          | A, laddr16                                                                                    | 3     | 8     | $A, CY \leftarrow A - (addr)^{2}$                                        | × | ×       | X    |

|          | A, [HL]                                                                                       | 1     | 6     | $A, CY \leftarrow A - (HL)$                                              | × | ×       | ×    |

|          | A, [HL + byte]                                                                                | 2     | 6     | $A, CY \leftarrow A - (HL + byte)$                                       | × | ×       | X    |

| SUBC     | A, #byte                                                                                      | 2     | 4     | $A, CY \leftarrow A - byte - CY$                                         | × | ×       | ×    |

| 0020     | saddr, #byte                                                                                  | 3     | 6     | (saddr), $CY \leftarrow$ (saddr) – byte – $CY$                           | × | ×       | ×    |

|          | A, r                                                                                          | 2     | 4     | $A, CY \leftarrow A - r - CY$                                            | × | ×       | ×    |

|          | A, saddr                                                                                      | 2     | 4     | $A, CY \leftarrow A - (saddr) - CY$                                      | × | ×       | ×    |

|          | A, !addr16                                                                                    | 3     | 8     | $A, CY \leftarrow A - (addr16) - CY$                                     | × | ×       | ×    |

|          | A, [HL]                                                                                       | 1     | 6     | $A, CY \leftarrow A - (HL) - CY$                                         | × | ×       | ×    |

|          | A, [HL + byte]                                                                                | 2     | 6     | A, $CY \leftarrow A - (HL + byte) - CY$                                  | × | ×       | ×    |

| AND      | A, #byte                                                                                      | 2     | 4     | $A \leftarrow A \land byte$                                              | × |         |      |

|          | saddr, #byte                                                                                  | 3     | 6     | $(saddr) \leftarrow (saddr) \land byte$                                  | × |         |      |

|          | A, r                                                                                          | 2     | 4     | $A \leftarrow A \land r$                                                 | × |         |      |

|          | A, saddr                                                                                      | 2     | 4     | $A \leftarrow A \land (saddr)$                                           | × |         |      |

|          | A, !addr16                                                                                    | 3     | 8     | $A \leftarrow A \land (addr16)$                                          | × |         |      |

|          | A, [HL]                                                                                       | 1     | 6     | $A \leftarrow A \land (HL)$                                              | × |         |      |

|          | A, [HL + byte]                                                                                | 2     | 6     | $A \leftarrow A \land (HL + byte)$                                       | × |         |      |

| Mnemonic | Operand        | Bytes | Clock | Operation                                                                 |   | Flags |    |

|----------|----------------|-------|-------|---------------------------------------------------------------------------|---|-------|----|

|          |                | -     |       | -                                                                         |   | AC    | CY |

| OR       | A, #byte       | 2     | 4     | $A \leftarrow A \lor$ byte                                                | × |       |    |

|          | saddr, #byte   | 3     | 6     | $(saddr) \leftarrow (saddr) \lor byte$                                    | × |       |    |

|          | A, r           | 2     | 4     | $A \leftarrow A \lor r$                                                   | × |       |    |

|          | A, saddr       | 2     | 4     | $A \leftarrow A \lor (saddr)$                                             | × |       |    |

|          | A, !addr16     | 3     | 8     | $A \leftarrow A \lor$ (addr16)                                            | × |       |    |

|          | A, [HL]        | 1     | 6     | $A \leftarrow A \lor (HL)$                                                | × |       |    |

|          | A, [HL + byte] | 2     | 6     | $A \leftarrow A \lor (HL + byte)$                                         | × |       |    |

| XOR      | A, #byte       | 2     | 4     | $A \leftarrow A \forall byte$                                             | × |       |    |

|          | saddr, #byte   | 3     | 6     | $(saddr) \leftarrow (saddr) \forall byte$                                 | × |       |    |

|          | A, r           | 2     | 4     | $A \leftarrow A \forall r$                                                | × |       |    |

|          | A, saddr       | 2     | 4     | $A \leftarrow A \forall$ (saddr)                                          | × |       |    |

|          | A, !addr16     | 3     | 8     | $A \leftarrow A \forall$ (addr16)                                         | × |       |    |

|          | A, [HL]        | 1     | 6     | $A \leftarrow A \forall (HL)$                                             | × |       |    |

|          | A, [HL + byte] | 2     | 6     | $A \leftarrow A \forall$ (HL + byte)                                      | × |       |    |

| CMP      | A, #byte       | 2     | 4     | A – byte                                                                  | × | ×     | ×  |

|          | saddr, #byte   | 3     | 6     | (saddr) – byte                                                            | × | ×     | ×  |

|          | A, r           | 2     | 4     | A – r                                                                     | × | ×     | ×  |

|          | A, saddr       | 2     | 4     | A – (saddr)                                                               | × | ×     | ×  |

|          | A, !addr16     | 3     | 8     | A – (addr16)                                                              | × | ×     | ×  |

|          | A, [HL]        | 1     | 6     | A – (HL)                                                                  | × | ×     | Х  |

|          | A, [HL + byte] | 2     | 6     | A – (HL + byte)                                                           | × | ×     | Х  |

| ADDW     | AX, #word      | 3     | 6     | AX, CY $\leftarrow$ AX + word                                             | × | ×     | ×  |

| SUBW     | AX, #word      | 3     | 6     | AX, CY $\leftarrow$ AX – word                                             | × | ×     | ×  |

| CMPW     | AX, #word      | 3     | 6     | AX – word                                                                 | × | ×     | ×  |

| INC      | r              | 2     | 4     | r ← r + 1                                                                 | × | ×     |    |

|          | saddr          | 2     | 4     | $(saddr) \leftarrow (saddr) + 1$                                          | × | ×     |    |

| DEC      | r              | 2     | 4     | r ← r + 1                                                                 | × | ×     |    |

|          | saddr          | 2     | 4     | $(saddr) \leftarrow (saddr) - 1$                                          | × | ×     |    |

| INCW     | rp             | 1     | 4     | $rp \leftarrow rp + 1$                                                    |   |       |    |

| DECW     | rp             | 1     | 4     | $rp \leftarrow rp - 1$                                                    |   |       |    |

| ROR      | A, 1           | 1     | 2     | $(CY, A_7 \leftarrow A_0, A_{m-1} \leftarrow A_m) \times 1$               |   |       | ×  |

| ROL      | A, 1           | 1     | 2     | $(CY, A_0 \leftarrow A_7, A_{m+1} \leftarrow A_m) \times 1$               |   |       | ×  |

| RORC     | A, 1           | 1     | 2     | $(CY \leftarrow A_0, A_7 \leftarrow CY, A_{m-1} \leftarrow A_m) \times 1$ |   |       | ×  |

| ROLC     | A, 1           | 1     | 2     | $(CY \leftarrow A7, A0 \leftarrow CY, Am+1 \leftarrow Am) \times 1$       |   |       | ×  |

| Mnemonic | Operand    | Bytes | Clock | Operation                                                                                                                                                                                                        |   | Flag |    |

|----------|------------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----|

|          | oporana    |       |       |                                                                                                                                                                                                                  | Z | AC   | CY |

| SET1     | saddr. bit | 3     | 6     | (saddr. bit) ← 1                                                                                                                                                                                                 |   |      |    |

|          | sfr. bit   | 3     | 6     | sfr. bit $\leftarrow 1$                                                                                                                                                                                          |   |      |    |

|          | A. bit     | 2     | 4     | A. bit ← 1                                                                                                                                                                                                       |   |      |    |

|          | PSW. bit   | 3     | 6     | PSW. bit $\leftarrow 1$                                                                                                                                                                                          | × | ×    | ×  |

|          | [HL]. bit  | 2     | 10    | (HL). bit $\leftarrow 1$                                                                                                                                                                                         |   |      |    |

| CLR1     | saddr. bit | 3     | 6     | (saddr. bit) $\leftarrow 0$                                                                                                                                                                                      |   |      |    |

|          | sfr. bit   | 3     | 6     | sfr. bit $\leftarrow 0$                                                                                                                                                                                          |   |      |    |

|          | A. bit     | 2     | 4     | A. bit $\leftarrow 0$                                                                                                                                                                                            |   |      |    |

|          | PSW. bit   | 3     | 6     | PSW. bit $\leftarrow 0$                                                                                                                                                                                          | × | ×    | ×  |

|          | [HL]. bit  | 2     | 10    | (HL). bit $\leftarrow 0$                                                                                                                                                                                         |   |      |    |

| SET1     | CY         | 1     | 2     | CY ← 1                                                                                                                                                                                                           |   |      | 1  |

| CLR1     | CY         | 1     | 2     | $CY \leftarrow 0$                                                                                                                                                                                                |   |      | 0  |

| NOT1     | CY         | 1     | 2     | $CY \leftarrow \overline{CY}$                                                                                                                                                                                    |   |      | ×  |

| CALL     | !addr16    | 3     | 6     | $(SP-1) \leftarrow (PC + 3)_{H}, (SP - 2) \leftarrow (PC + 3)_{L},$<br>$PC \leftarrow addr16, SP \leftarrow SP - 2$                                                                                              |   |      |    |

| CALLT    | [addr5]    | 1     | 8     | $\begin{split} (SP-1) &\leftarrow (PC + 1)_{H},  (SP - 2) \leftarrow (PC + 1)_{L}, \\ PC_{H} &\leftarrow (00000000,  addr5 + 1), \\ PC_{L} &\leftarrow (00000000,  addr5), \\ SP &\leftarrow SP - 2 \end{split}$ |   |      |    |

| RET      |            | 1     | 6     | $PC_{H} \leftarrow (SP+1),  PC_{L} \leftarrow (SP),  SP \leftarrow SP+2$                                                                                                                                         |   |      |    |

| RETI     |            | 1     | 8     | PC <sub>H</sub> ← (SP + 1), PC <sub>L</sub> ← (SP),<br>PSW ← (SP + 2), SP ← SP + 3, NMIS ← 0                                                                                                                     | R | R    | R  |

| PUSH     | PSW        | 1     | 2     | $(SP - 1) \leftarrow PSW, SP \leftarrow SP - 1$                                                                                                                                                                  |   |      |    |

|          | rp         | 1     | 4     | $(SP - 1) \leftarrow rp_H, (SP - 2) \leftarrow rp_L, SP \leftarrow SP - 2$                                                                                                                                       |   |      |    |

| POP      | PSW        | 1     | 4     | $PSW \leftarrow (SP),  SP \leftarrow SP + 1$                                                                                                                                                                     | R | R    | R  |

|          | rp         | 1     | 6     | $rp_{H} \leftarrow (SP + 1), rp_{L} \leftarrow (SP), SP \leftarrow SP + 2$                                                                                                                                       |   |      |    |

| MOVW     | SP, AX     | 2     | 8     | $SP \leftarrow AX$                                                                                                                                                                                               |   |      |    |

|          | AX, SP     | 2     | 6     | $AX \leftarrow SP$                                                                                                                                                                                               |   |      |    |

| BR       | !addr16    | 3     | 6     | $PC \leftarrow addr16$                                                                                                                                                                                           |   |      |    |

|          | \$addr16   | 2     | 6     | $PC \leftarrow PC + 2 + jdisp8$                                                                                                                                                                                  |   |      |    |

|          | AX         | 1     | 6     | $PCH \leftarrow A, PCL \leftarrow X$                                                                                                                                                                             | + |      |    |

| Masaasia | Onerend              | Durtaa | Clask | Oreartier                                                  | Flags   |  |  |

|----------|----------------------|--------|-------|------------------------------------------------------------|---------|--|--|

| Mnemonic | Operand              | Bytes  | Clock | Operation                                                  | Z AC CY |  |  |

| BC       | \$saddr16            | 2      | 6     | $PC \leftarrow PC + 2 + jdisp8$ if $CY = 1$                |         |  |  |

| BNC      | \$addr16             | 2      | 6     | $PC \leftarrow PC + 2 + jdisp8$ if $CY = 0$                |         |  |  |

| BZ       | \$addr16             | 2      | 6     | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 1$                 |         |  |  |

| BNZ      | \$addr16             | 2      | 6     | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 0$                 |         |  |  |

| BT       | saddr. bit, \$addr16 | 4      | 10    | $PC \leftarrow PC + 4 + jdisp8$                            |         |  |  |

|          |                      |        |       | if (saddr. bit) = 1                                        |         |  |  |

|          | sfr. bit, \$addr16   | 4      | 10    | $PC \leftarrow PC + 4 + jdisp8$ if sfr. bit = 1            |         |  |  |

|          | A. bit, \$addr16     | 3      | 8     | $PC \leftarrow PC + 3 + jdisp8$ if A. bit = 1              |         |  |  |

|          | PSW. bit, \$addr16   | 4      | 10    | $PC \leftarrow PC + 4 + jdisp8$ if PSW. bit = 1            |         |  |  |

| BF       | saddr. bit, \$addr16 | 4      | 10    | $PC \leftarrow PC + 4 + jdisp8$                            |         |  |  |

|          |                      |        |       | if (saddr. bit) = 0                                        |         |  |  |

|          | sfr. bit, \$addr16   | 4      | 10    | $PC \leftarrow PC + 4 + jdisp8$ if sfr. bit = 0            |         |  |  |

|          | A. bit, \$addr16     | 3      | 8     | $PC \leftarrow PC + 3 + jdisp8$ if A. bit = 0              |         |  |  |

|          | PSW. bit, \$addr16   | 4      | 10    | $PC \leftarrow PC + 4 + jdisp8$ if PSW. bit = 0            |         |  |  |

| DBNZ     | B, \$addr16          | 2      | 6     | $B \leftarrow B - 1$ , then                                |         |  |  |

|          |                      |        |       | $PC \leftarrow PC + 2 + jdisp8$ if $B \neq 0$              |         |  |  |

|          | C, \$addr16          | 2      | 6     | $C \leftarrow C - 1$ , then                                |         |  |  |

|          |                      |        |       | $PC \leftarrow PC + 2 + jdisp8$ if $C \neq 0$              |         |  |  |

|          | saddr, \$addr16      | 3      | 8     | $(saddr) \leftarrow (saddr) - 1$ , then                    |         |  |  |

|          |                      |        |       | $PC \leftarrow PC + 3 + jdisp8 \text{ if } (saddr) \neq 0$ |         |  |  |

| NOP      |                      | 1      | 2     | No Operation                                               |         |  |  |

| EI       |                      | 3      | 6     | $IE \leftarrow 1$ (Enable Interrupt)                       |         |  |  |

| DI       |                      | 3      | 6     | $IE \leftarrow 0$ (Disable Interrupt)                      |         |  |  |

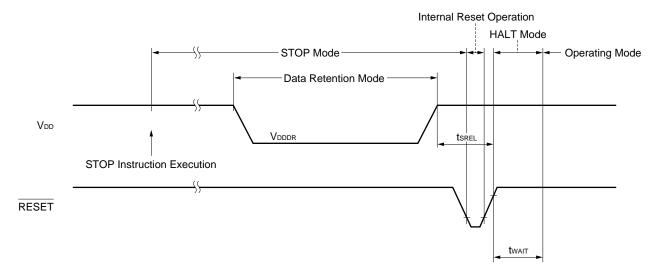

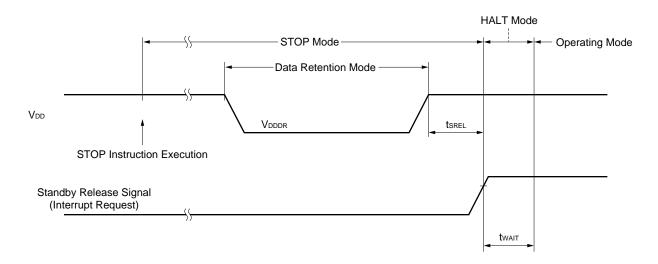

| HALT     |                      | 1      | 2     | Set HALT Mode                                              |         |  |  |

| STOP     |                      | 1      | 2     | Set STOP Mode                                              |         |  |  |

#### 7. PROM PROGRAMMING

The program memory in  $\mu$ PD78P9014 is an 8K-byte one-time PROM that can be written electrically. The pins listed in Table 7-1 are used to write or verify this one-time PROM. For the connections for unused pins, see to "(2) PROM programming mode" in section 1, "Pin Connection Diagram (Top View)." The method updates the address by the clock input from the X1 pin and not the address input.

| Pin Name | Function                                                                                                                                                                                   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vpp      | High voltage pin for setting the PROM programming mode and writing or verifying a program (usually, the $V_{DD}$ potential)                                                                |

| MD0-MD3  | Operating mode selection pin when writing or verifying a program                                                                                                                           |

| D0-D7    | Data bus                                                                                                                                                                                   |

| X1       | Address update clock input when writing or verifying a program                                                                                                                             |

| ★ Vdd    | Pin for setting the PROM programming mode and applying the power supply voltage. In the normal operating mode, 1.8 to 5.5 V are applied. In the PROM programming mode, +5.5 V are applied. |

#### Table 7-1. Pins in the PROM Programming Mode

#### 7.1 Operating Modes

If +5.5 V is applied to the V<sub>DD</sub> pin and +12.5 V is applied to V<sub>PP</sub> pin, the PROM programming mode is entered. This mode becomes an operating mode in Table 7-2 based on the settings of the MD0 to MD3 pins.

| Table 7-2. | Operating | Modes in | PROM | Programming |

|------------|-----------|----------|------|-------------|

|------------|-----------|----------|------|-------------|

|   | Pins<br>Operating Mode                   | Vpp   | Vdd  | MD0 | MD1 | MD2 | MD3 |

|---|------------------------------------------|-------|------|-----|-----|-----|-----|

| * | Zero clear of the program memory address | +12.5 | +5.5 | н   | L   | Н   | L   |

|   | Write mode                               |       |      | L   | Н   | Н   | Н   |

|   | Verify mode                              |       |      | L   | L   | Н   | Н   |

|   | Program inhibit mode                     |       |      | Н   | ×   | Н   | Н   |

$\mathsf{X}:\mathsf{L} \text{ or }\mathsf{H}$

\*

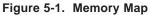

#### 7.2 PROM writing procedure

The following is the PROM writing procedure. High-speed writing is enabled.

- (1) Pull down each unused pin through a resistor to Vss. The X1 pin has the low level.

- (2) Supply +5 V to the VDD and VPP pins.

- (3) Wait 10 μs.

- (4) 0 clear mode in the program memory address

- (5) Supply 5.5 V to the V\_DD pin and 12.5 V to the V\_PP pin.

- (6) Write data in the 1-ms write mode.

- (7) Verify mode. If written, go to (8). If not written, repeat (6) and (7).

- (8) Additional write for (Counts written in (6) and (7): X)  $\times$  1 ms

- (9) Update (+1) the program memory address by the input of four pulses at the X1 pin.

- (10) Repeat (6) to (9) until the last address.

- (11) 0 clear mode of the program memory address

- (12) Change the voltages at the VDD and VPP pins to 5 V.

- (13) Power off

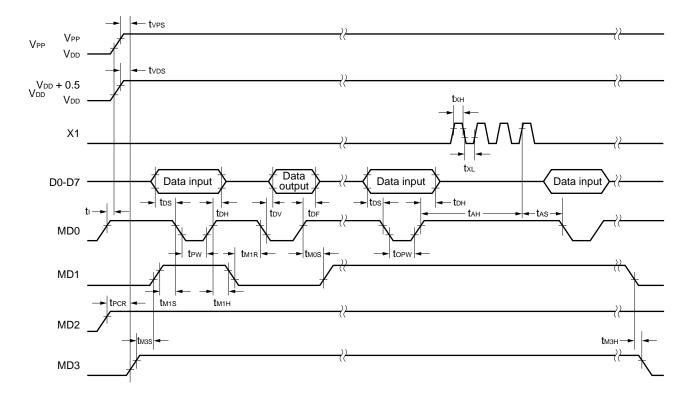

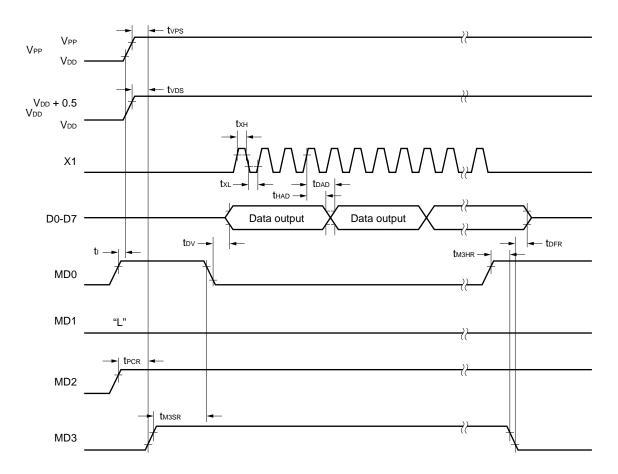

Steps (2) to (9) are illustrated in the following diagram.

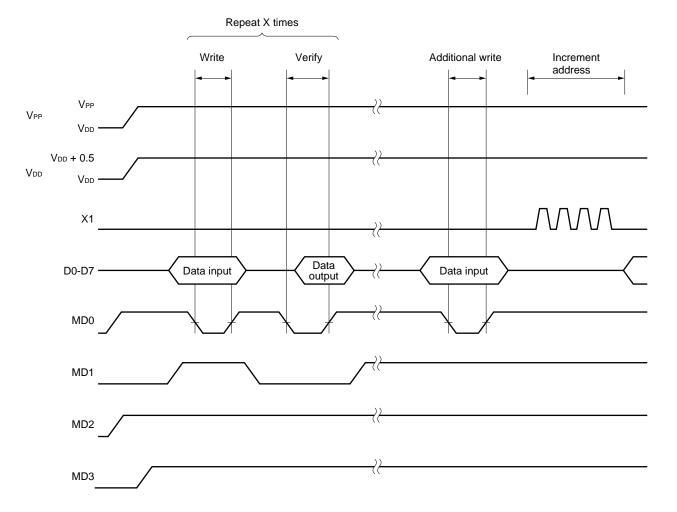

#### 7.3 PROM reading procedure

The following is the PROM reading procedure.

- (1) Pull down each unused pin through the resistor to Vss. The X1 pin has the low level.

- (2) Supply +5 V to the VDD and VPP pins.

- (3) Wait 10 μs.

- (4) 0 clear mode in the program memory address

- ★ (5) Supply +5.5V to V<sub>DD</sub> and +12.5 V to V<sub>PP</sub>.

- (6) Verify mode. When clock pulses are input to the X1 pin, the data are sequentially output for each address for a period of four clock pulses.

- (7) 0 clear mode in the program memory address

- (8) Supply +5 V to the VDD and VPP pins.

- (9) Power off

Steps (2) to (7) are shown in the figure below.

#### 7.4 One-Time PROM Product Screening

The one-time PROM product cannot be tested completely by NEC before it is shipped, because of its structure. It is recommended to perform screening to verify PROM after writing necessary data and performing high-temperature storage under the following conditions.

| Storage Temperature | Storage Time |

|---------------------|--------------|

| 125 °C              | 24 hours     |

\*

NEC provides a fee-based, one-time microprocessor PROM writing, marking, screening, and verifying service called QTOP. For details, contact your NEC distributor.

#### ★ 8. ELECTRICAL SPECIFICATIONS

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Parameter                     | Symbol               | Test Condition    | ons        | Rating                        | Unit |

|-------------------------------|----------------------|-------------------|------------|-------------------------------|------|

| Supply voltages               | Vdd                  |                   |            | -0.3 to + 7.0                 | V    |

|                               | Vpp                  |                   |            | -0.3 to + 13.5                | V    |

| Input voltage                 | Vı                   |                   |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage                | Vo                   |                   |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output current, high          | I <sub>OH</sub> Note | 1 pin             | Peak value | -10                           | mA   |

|                               |                      |                   | r.m.s.     | -5                            | mA   |

|                               |                      | Total of all pins | Peak value | -30                           | mA   |

|                               |                      |                   | r.m.s.     | -15                           | mA   |

| Output current, low           | <sub>OL</sub> Note   | 1 pin             | Peak value | 30                            | mA   |

|                               |                      |                   | r.m.s.     | 15                            | mA   |

|                               |                      | Total of all pins | Peak value | 160                           | mA   |

|                               |                      |                   | r.m.s.     | 80                            | mA   |

| Operating ambient temperature | TA                   |                   |            | -40 to +85                    | °C   |

| Storage temperature           | Tstg                 |                   |            | -65 to +150                   | °C   |

**Note** r.m.s. should be calculated as follows [r.m.s.] = [peak value]  $\times \sqrt{duty}$

Caution Product quality may suffer if the absolute maximum rating is exceeded for even an single parameter or even momentarily. That is, the absolute maximum ratings are the rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions which ensure that the absolute maximum ratings are not exceeded.

**Remark** The characteristics of an alternate function pin and a port pin are the same unless specified otherwise.

Capacitance (TA = 25°C, VDD = Vss = 0 V)

| Parameter          | Symbol | Test Condition                             | MIN. | TYP. | MAX. | Unit |

|--------------------|--------|--------------------------------------------|------|------|------|------|

| Input capacitance  | CIN    | f = 1 MHz, Unmeasured pins returned to 0 V |      |      | 15   | pF   |

| Output capacitance | Соит   |                                            |      |      | 15   | pF   |

| I/O capacitance    | Сю     |                                            |      |      | 15   | pF   |

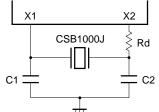

| Resonator            | Recommended Circuit | Parameter                                           | Test Condition                                              | MIN. | TYP. | MAX. | Unit |

|----------------------|---------------------|-----------------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| Ceramic<br>resonator | X1 X2               | Oscillator frequency (fx) <sup>Note 1</sup>         | VDD = Oscillating voltage range                             | 1.0  |      | 5.0  | MHz  |

|                      |                     | Oscillation stabilization<br>time <sup>Note 2</sup> | After V <sub>DD</sub> reaches oscillator voltage range MIN. |      |      | 4    | ms   |

| Crystal resonator    | X1 X2               | Oscillating frequency (fx)Note 1                    |                                                             | 1.0  |      | 5.0  | MHz  |

|                      |                     | Oscillation stabilization                           | V <sub>DD</sub> = 4.5 to 5.5 V                              |      |      | 10   | ms   |

|                      |                     | time <sup>Note 2</sup>                              |                                                             |      |      | 30   |      |

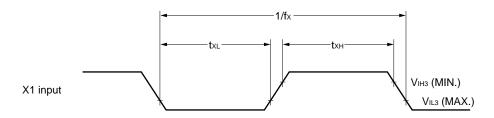

| External clock       | X2 X1               | X1 input frequency (fx) <sup>Note 1</sup>           |                                                             | 1.0  |      | 5.0  | MHz  |

|                      |                     | X1 input high/low level width<br>(txH, txL)         |                                                             | 100  |      | 500  | ns   |

#### Main System Clock Oscillation Circuit Characteristics(TA = -40 to +85 °C, VDD = 1.8 to 5.5 V)

- **Notes 1.** Indicates only oscillation circuit characteristics. Refer to AC characteristics for instruction execution time.

- 2. Time required to stabilize oscillation after reset or STOP mode release.

Caution When using the main system clock oscillator, wiring the area enclosed with the dotted line should be carried out as follows to avoid an adverse effect from wiring capacitance.

- Wiring should be as short as possible.

- Wiring should not cross other signal lines.

- Wiring should not be placed close to a varying higher current.

- The potential of the oscillator capacitor ground should be the same as Vss.

- Do not ground wiring to a ground pattern in which a high current flows.

- · Do not fetch a signal from the oscillator.

#### ★ Recommended Oscillating Circuit Constants

#### Ceramic Resonator (T<sub>A</sub> = -40 to $+85^{\circ}$ C)

| Manufacturer             | Product Name             | Frequency<br>(MHz) | Oscillat<br>Circuit<br>Consta | nt (pF) | (Vdd) | Range | Remarks                                                     |

|--------------------------|--------------------------|--------------------|-------------------------------|---------|-------|-------|-------------------------------------------------------------|

|                          |                          |                    | C1                            | C2      | MIN.  | MAX.  |                                                             |

| Murata Mfg.<br>Co., Ltd. | CSB1000J <sup>Note</sup> | 1.00               | 100                           | 100     | 1.8   | 5.5   | Rd = 1.0 kΩ                                                 |

| CO., LIU.                | CSA2.00MG040             | 2.00               | 100                           | 100     | 2.0   | 5.5   |                                                             |

|                          | CST2.00MG040             |                    | _                             | -       |       |       | Product containing capacitor                                |

|                          | CSA4.19MG                | 4.19               | 30                            | 30      | 1.8   | 5.5   |                                                             |

|                          | CST4.19MGW               |                    | _                             | -       |       |       | Product containing capacitor                                |

|                          | CSA5.00MG                | 5.00               | 30                            | 30      | 2.2   | 5.5   |                                                             |

|                          | CST5.00MGW               |                    | -                             | -       |       |       | Product containing capacitor                                |

|                          | CSA5.00MGU               |                    | 30                            | 30      | 1.8   | 5.5   |                                                             |

|                          | CST5.00MGWU              |                    | _                             | -       |       |       | Product containing capacitor                                |

| ток                      | CCR1000K2                | 1.0                | 100                           | 100     | 1.8   | 5.5   |                                                             |

|                          | CCR4.19MC3               | 4.19               | _                             | -       | 1.8   | 5.5   | Product containing capacitor                                |

|                          | FCR4.19MC5               |                    | _                             | -       | 2.0   |       | Product containing capacitor                                |

|                          | CCR5.0MC3                | 5.0                | _                             | -       | 2.2   | 5.5   | Product containing capacitor                                |

|                          | FCR5.0MC5                |                    | -                             | -       | 2.0   |       | Product containing capacitor                                |

| Kyocera Corp.            | KBR-1000F/Y              | 1.0                | 100                           | 100     | 1.8   | 5.5   | $T_A = -20$ to +85 °C                                       |

|                          | KBR-2.0MS                | 2.0                | 68                            | 68      | 2.1   | 5.5   |                                                             |

|                          | PBRC4.19A                | 4.19               | 33                            | 33      | 1.8   | 5.5   |                                                             |

|                          | PBRC4.19B                |                    | -                             | -       |       |       | Product containing capacitor, $T_A = -20$ to +85°C          |

|                          | KBR-4.19MSB              |                    | 33                            | 33      |       |       | $T_{A} = -20 \text{ to } +85^{\circ}\text{C}$               |

|                          | KBR-4.19MKC              |                    | _                             | -       |       |       | Product containing capacitor, $T_A = -20$ to +85°C          |

|                          | PBRC5.00A                | 5.0                | 33                            | 33      | 1.8   | 5.5   | T <sub>A</sub> = −20 to +85°C                               |

|                          | PBRC5.00B                |                    | _                             | _       | 1     |       | Product containing capacitor, $T_A = -20$ to $+85^{\circ}C$ |

|                          | KBR-5.0MSB               |                    | 33                            | 33      |       |       | T <sub>A</sub> = −20 to +85°C                               |

|                          | KBR-5.0MKC               |                    | _                             | -       | 1     |       | Product containing capacitor, $T_A = -20$ to $+85^{\circ}C$ |

**Note** If the ceramic resonator is the CSB1000J (1.0 MHz) by Murata Mfg. Co., Ltd., the limiting resistor (Rd = 1.0  $k\Omega$ ) is needed (see the following figure). If another recommended oscillator is used, the limiting resistor is not needed.

Caution The oscillation circuit constants and oscillation voltage range indicate conditions for stable oscillation but do not guarantee the accuracy of the oscillation frequency. If the application circuit requires accuracy of the oscillation frequency, it is necessary to set the oscillation frequency of the resonator in the application circuit. For this, it is necessary to directly contact manufacturer of the resonator being used.

| Parameter                    | Symbol | Test Conditions                           |                                | MIN.      | TYP. | MAX.    | Unit |

|------------------------------|--------|-------------------------------------------|--------------------------------|-----------|------|---------|------|

| Output current, low          | lo∟    | 1 pin                                     |                                |           |      | 15      | mA   |

|                              |        | Total of all of the pins                  |                                |           | 80   | mA      |      |

| Input voltage, high          | VIH1   | P00 to P07, P10 to P17,                   | V <sub>DD</sub> = 2.7 to 5.5 V | 0.7 Vdd   |      | Vdd     | V    |

|                              |        | P20 to P22, P30 to P32                    |                                | 0.9 Vdd   |      | Vdd     | V    |

|                              | VIH2   | INTP0 to INTP2, SI0, RxD,                 | V <sub>DD</sub> = 2.7 to 5.5 V | 0.8 Vdd   |      | Vdd     | V    |

|                              |        | ASCK, SCK0, TI0, TI1, RESET               |                                | 0.9 Vdd   |      | Vdd     | V    |

|                              | Vінз   | X1, X2                                    |                                | Vdd - 0.1 |      | Vdd     | V    |

| Input voltage, low           | VIL1   | P00 to P07, P10 to P17,                   | V <sub>DD</sub> = 2.7 to 5.5 V | 0         |      | 0.3 Vdd | V    |

|                              |        | P20 to P22, P30 to P32                    |                                | 0         |      | 0.1 Vdd | V    |

|                              | VIL2   | INTP0 to INTP2, SI0, RXD,                 | V <sub>DD</sub> = 2.7 to 5.5 V | 0         |      | 0.2 Vdd | V    |

|                              |        | ASCK, SCK0, TI0, TI1, RESET               |                                | 0         |      | 0.1 Vdd | V    |

|                              | VIL3   | X1, X2                                    |                                | 0         |      | 0.1     | V    |

| Output voltage, high         | Vон    | VDD = 4.5 to 5.5 V, IOH = $-1 \text{ mA}$ |                                | Vdd - 1.0 |      |         | V    |

|                              |        | Іон = -100 μА                             |                                | Vdd - 0.5 |      |         | V    |

| Output voltage, low          | Vol    | $V_{DD}$ = 4.5 to 5.5 V, IoL = 10 mA      |                                |           |      | 1.0     | V    |

|                              |        | lol = 400 μA                              |                                |           |      | 0.5     | V    |

| Input leakage current, high  | Ілні   | Vin = Vdd                                 | Pins other than                |           |      | 3       | μΑ   |

|                              |        |                                           | X1 and X2                      |           |      |         |      |

|                              | ILIH2  |                                           | X1, X2                         |           |      | 20      | μΑ   |

| Input leakage current, low   | ILIL1  | $V_{IN} = 0 V$                            | Pins other than                |           |      | -3      | μΑ   |

|                              |        |                                           | X1 and X2                      |           |      |         |      |

|                              | ILIL2  |                                           | X1, X2                         |           |      | -20     | μΑ   |

| Output leakage current, high | Ігон   | Vout = Vdd                                |                                |           |      | 3       | μΑ   |

| Output leakage current, low  | Ilol   | Vout = 0 V                                |                                |           |      | -3      | μΑ   |

**Remark** The characteristics of an alternate function pin and a port pin are the same unless specified otherwise.

#### DC Characteristics (T<sub>A</sub> = -40 to $+85^{\circ}$ C, V<sub>DD</sub> = 1.8 to 5.5 V)

| Parameter                 | Symbol | Test Con                                                 | Test Conditions                                      |    |      | MAX. | Unit |

|---------------------------|--------|----------------------------------------------------------|------------------------------------------------------|----|------|------|------|

| Software pull-up resistor | R      | V <sub>IN</sub> = 0 V                                    |                                                      | 50 | 100  | 200  | kΩ   |

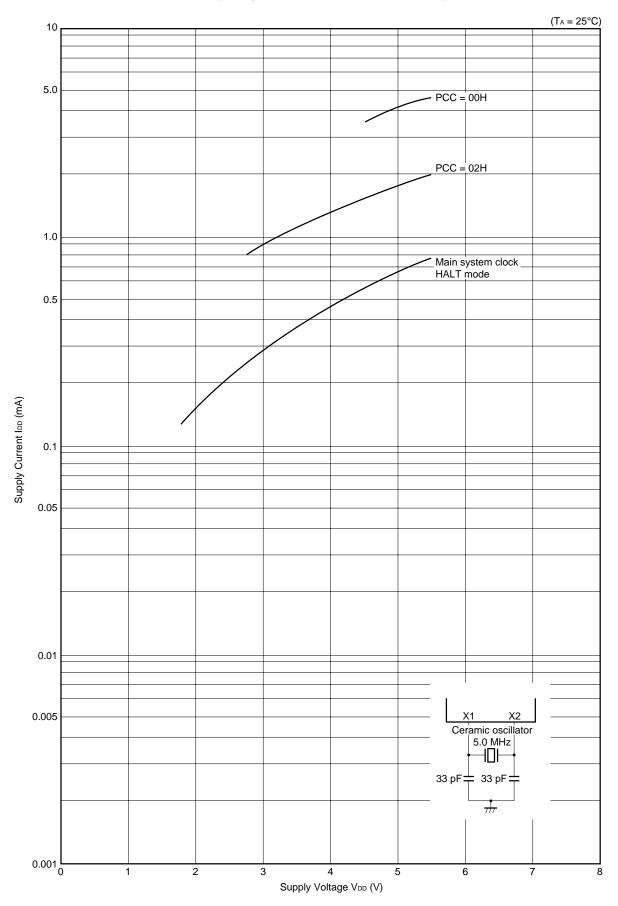

| Supply currentNote 1      | IDD1   | 5.0 MHz                                                  | 5.0 MHz V <sub>DD</sub> = 5.0 V ± 10 % <b>Note 2</b> |    | 4.2  | 12.0 | mA   |

|                           |        | Crystal oscillation operation                            | V <sub>DD</sub> = 3.0 V ± 10 %Note 3                 |    | 0.95 | 2.8  | mA   |

|                           | IDD2   | 5.0 MHz V <sub>DD</sub> = 5.0 V ± 10 % <sup>Note 2</sup> |                                                      |    | 0.7  | 2.0  | mA   |

|                           |        | Crystal oscillation HALT mode                            | $V_{DD}$ = 3.0 V ± 10 %Note 3                        |    | 0.3  | 0.9  | mA   |

|                           | Idd3   | STOP mode                                                | $V_{DD} = 5.0 \text{ V} \pm 10 \%$                   |    | 0.1  | 20   | μΑ   |

|                           |        |                                                          | $V_{DD} = 3.0 \text{ V} \pm 10 \%$                   |    | 0.05 | 8    | μA   |

|                           |        |                                                          | $V_{DD} = 2.0 \text{ V} \pm 10 \%$                   |    | 0.05 | 10   | μA   |

Notes 1. This does not include the port current (containing the current flowing through the on-chip pull-up resistor).

2. When operating at high-speed mode (when the processor clock control register (PCC) is set to 00H)

3. When operating at low-speed mode (when PCC is set to 02H)

**Remark** The characteristics of an alternate function pin and a port pin are the same unless specified otherwise.

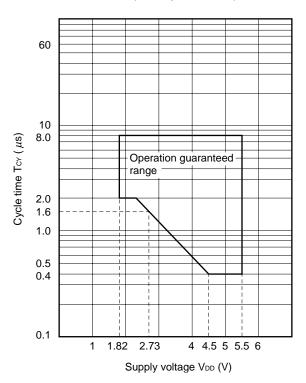

#### **AC Characteristics**

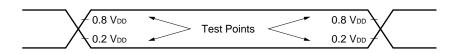

| Parameter                   | Symbol        | Test Conditions                                              |                                |    | TYP. | MAX. | Unit |

|-----------------------------|---------------|--------------------------------------------------------------|--------------------------------|----|------|------|------|

| Cycle time (Min.            | Тсү           | $4.5 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$ |                                |    |      | 8    | μs   |

| instruction execution time) |               | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}$ |                                |    |      | 8    | μs   |

|                             |               |                                                              |                                |    |      | 8    | μs   |

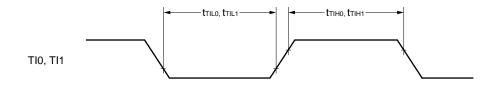

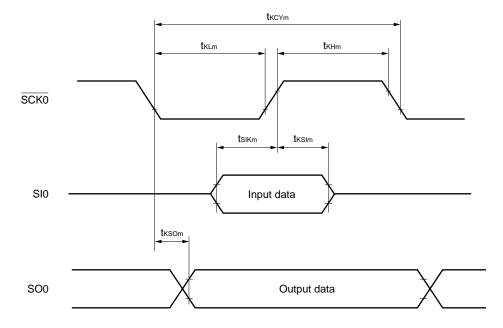

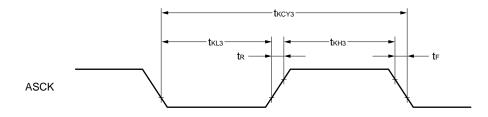

| TI0, TI1 inputs             | tтıн,         | V <sub>DD</sub> = 2.7 to 5.5 V                               |                                |    |      |      | μs   |

| High/low level widths       | t⊤ı∟          |                                                              |                                |    |      |      | μs   |

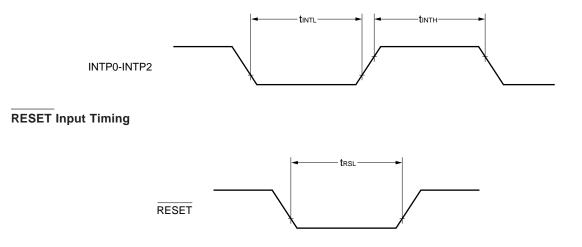

| TI0, TI1 input frequency    | fтı           | VDD = 2.7 to 5.5 V                                           |                                | 0  |      | 4    | MHz  |